Sobre la figura de méritos de Baliga (BFOM) Mejora de un nuevo transistor de efecto de campo vertical (FET) de nanopilar GaN con canal 2DEG y Sustrato estampado

Resumen

Un novedoso transistor de efecto de campo (FET) vertical de GaN en modo de mejora con 2DEG para reducir la resistencia en estado ( R ACTIVADO ) y patrón de sustrato (SP) para mejorar el voltaje de ruptura (BV) se propone en este trabajo. Al diseñar deliberadamente el ancho y la altura del SP, el campo eléctrico de alta concentración (campo E) debajo del límite de p-GaN podría separarse sin afectar drásticamente a la R ACTIVADO , resultando una figura de méritos de Baliga mejorada (BFOM, BV 2 / R ACTIVADO ). Verificado mediante simulación ATLAS calibrada experimentalmente, el dispositivo propuesto con un SP de 700 nm de largo y 4,6 μm de ancho presenta un BFOM seis veces mayor en comparación con el FET sin sustrato estampado. Además, el dispositivo de pilar propuesto y el SP en el interior solo ocupan un área de nanoescala, lo que permite una integración de alta densidad de dichos dispositivos, lo que genera su alto potencial en futuras aplicaciones de energía.

Antecedentes

Hoy en día, los semiconductores de banda ancha ancha como ZnO, In 2 O 3 , SiC y nitruro de galio (GaN) han atraído la atención [1,2,3,4,5]. Considerando que, considerando las propiedades electrónicas, el transistor lateral de alta movilidad de electrones (HEMT) AlGaN / GaN es ampliamente considerado como un candidato potencial para sustituir el dispositivo basado en Si en aplicaciones de potencia o frecuencia debido a la mayor tensión de ruptura (BV), así como a la estabilidad térmica más fuerte. Muchos esfuerzos, como el casquete tipo p [6, 7], la implantación de iones de flúor [8, 9], la barrera delgada [10, 11], el canal doble [5, 12] y la compuerta acoplada al campo [13] , se han realizado sobre la realización del tipo de mejora HEMT que se desea para simplificar el circuito del controlador.

Sin embargo, estas tecnologías enfrentan muchos desafíos formidables, como la baja uniformidad del voltaje de umbral, el desperdicio del área vertical del chip, el colapso de la corriente, la figura de méritos (BFOM) limitada de Baliga, etc. Especialmente, la contradicción entre la longitud de la deriva y el BV influye negativamente en la reducción del dispositivo [14, 15]. En otras palabras, un dispositivo más pequeño conduce a un BV más bajo, en el que es más difícil adoptar los terminales de unión que promueven el BFOM al optimizar la distribución del campo eléctrico. Con este fin, la barrera trasera [16], la unión enterrada [17], la placa de campo de pozos cuánticos [18] y otras estructuras que se insertan en el HEMT lateral que exhiben la característica de la placa de campo eléctrico se han propuesto para mejorar la VB mediante la utilización de la región vertical del chip.

Por otro lado, en virtud de la naturaleza superior de GaN, el transistor de efecto de campo vertical (VFET) de GaN a granel atrae cada vez más atención debido a la realización más fácil de la funcionalidad de tipo mejora y la plena utilización de la región vertical [19 , 20, 21, 22]. Muchas estructuras novedosas se presentan mediante experimentos o simulaciones para inclinar el BV y reducir simultáneamente la resistencia en estado ( R ACTIVADO ) [23, 24, 25]. Sin embargo, sin mencionar las dificultades para fabricar la superunión (SJ) en GaN, la falta del gas de electrones bidimensionales de alta movilidad (2DEG) conduce a un R más alto. ACTIVADO [26], lo que dificulta la optimización de BFOM en tales dispositivos.

En este trabajo, un novedoso modo de mejora vertical GaN FET con 2DEG para reducir la R ACTIVADO y se propone un patrón de sustrato (SP) para mejorar el BV, en el que la combinación del canal 2DEG y el SP equilibra eficazmente la contradicción entre la baja resistencia en estado activado y el alto BV. Además, el pilar del dispositivo propuesto y el SP en el interior solo ocupan un área de nanoescala, lo que permite una integración de alta densidad de dichos dispositivos. Verificado por simulación numérica construida en ATLAS, el dispositivo propuesto presenta un BFOM más alto en comparación con el mismo transistor de efecto de campo (FET) sin el sustrato estampado, lo que brinda su alto potencial en futuras aplicaciones de energía.

Método

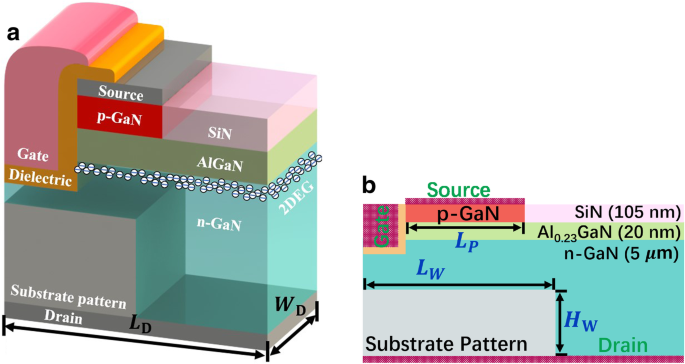

El dispositivo propuesto se genera en un Al 0.23 normal Oblea de GaN / GaN con un sustrato de tipo n altamente concentrado que actúa como electrodo de drenaje como se muestra en la Fig.1a, donde el espesor de la capa de nitruro de silicio (SiN), AlGaN y GaN son 105 nm, 20 nm y 5 μm , respectivamente. Un GaN de tipo n con 2 × 10 16 cm −3 dopaje n D y un límite de GaN tipo p con 2 × 10 17 cm −3 dopaje n A se establece como el búfer y el canal compuesto, respectivamente [27, 28]. Otro componente del canal al lado de la puerta es una capa delgada de AlGaN que se introduce para inducir 2DEG como se muestra en la Fig. 1b. Un SP, elaborado con óxido de aluminio (Al 2 O 3 ) por ejemplo en este documento, se cultiva sobre el sustrato.

El esquema a Estructura de pilares 3D y b sección transversal con parámetros geométricos etiquetados del SP-VFET propuesto

Por lo tanto, todo el dispositivo podría fabricarse mediante un proceso estándar sucesivamente:(1) la deposición epitaxial del sustrato de conducción y la capa SP integrada, (2) el grabado parcial del patrón SP, (3) la deposición y pulido de n- Tampón de GaN, (4) la deposición de la barrera de AlGaN y la tapa de p-GaN, y (5) la fabricación de electrodos y pasivación.

El simulador de ATLAS implantado se calibra con los datos experimentales de un HEMT de tipo realce con un límite de p-GaN [29, 30]. Las especificaciones calibradas y otras del dispositivo se muestran en la Tabla 1. Otras configuraciones se pueden encontrar en nuestro trabajo anterior [31]. El tipo y la densidad de la trampa de interfaz ubicada en la interfaz SP / GaN se refieren a mediciones experimentales basadas en capacitancia [32,33,34]. La carga de polarización en la superficie AlGaN / GaN se confirma de acuerdo con la ecuación de ajuste cuadrático simple correspondiente [35].

Mecanismo de física

En estado encendido, en comparación con el dispositivo sin el canal de 2 DEG y el SP, el transistor de efecto de campo vertical propuesto con patrón de sustrato (SP-VFET) presenta una ruta altamente conductora debido a los 2 DEG y un canal de corriente vertical más estrecho. que reduce la conductancia como se muestra en la Fig. 2. En detalle, gracias al 2DEG de alta densidad concentrado en la interfaz AlGaN / GaN, la trayectoria lateral del flujo de corriente podría mantenerse, lo que compensa parcialmente la conductancia total del dispositivo. Por el contrario, la capacidad de transporte actual del dispositivo SP-VFET sin canal 2DEG se vería influenciada dramáticamente.

La ilustración esquemática del flujo de corriente directo en a el dispositivo sin el SP, b el SP-VFET propuesto con un SP corto y c un SP largo

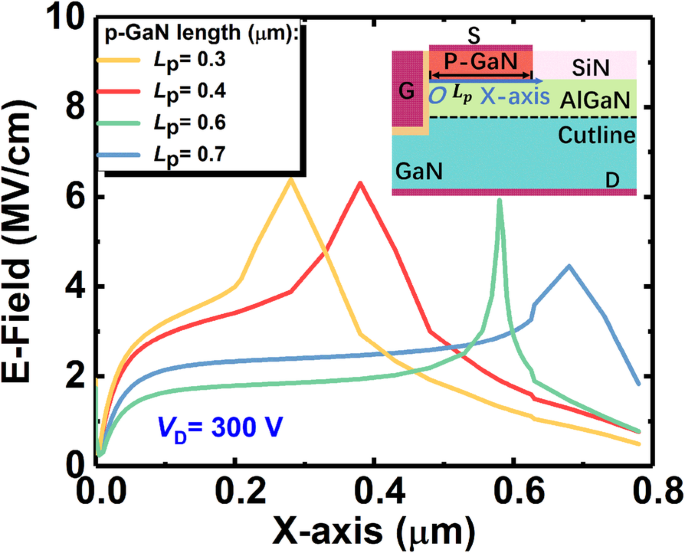

La longitud del límite de p-GaN no influiría drásticamente en la concentración del campo eléctrico (campo E) hasta que la longitud sea superior a 700 nm, por lo que el p-GaN cubre casi toda la superficie del dispositivo. Como se muestra en la Fig. 3, la distribución del campo E a lo largo de la interfaz AlGaN / GaN posee un pico alrededor de la esquina derecha de p-GaN. La posición del pico cambia junto con la longitud variable de p-GaN y, sin embargo, mantiene la misma magnitud. Se puede ver una pequeña diferencia del valor pico en la Fig.3 cuando la tapa de p-GaN es más larga que 600 nm, porque la tapa larga de p-GaN aplana todo el campo E en el dispositivo y, por lo tanto, expande la resistencia del dispositivo debido a al agotamiento del 2DEG.

La distribución del campo eléctrico del dispositivo sin el SP a lo largo de la heterounión AlGaN / GaN en diferentes longitudes de p-GaN

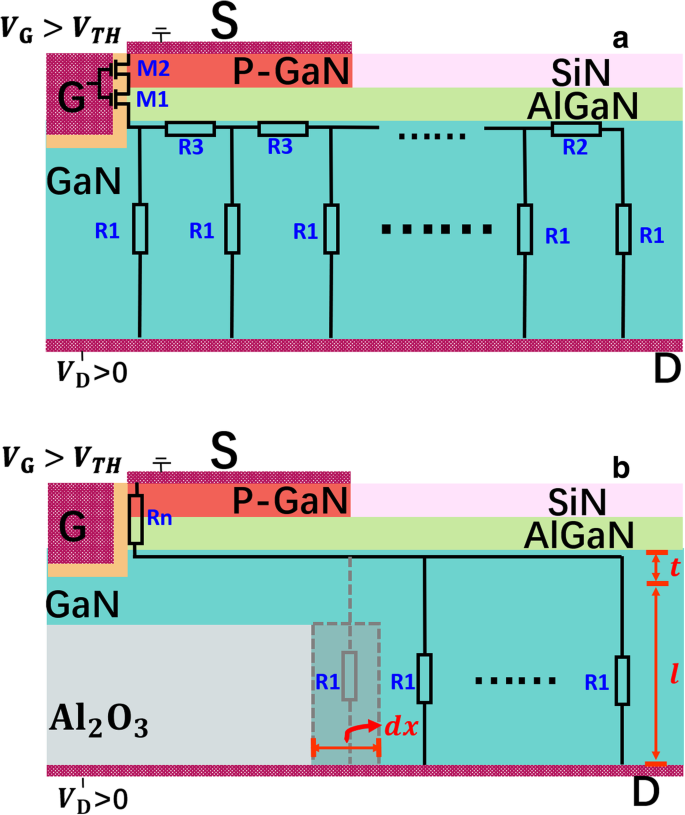

Para ilustrar la influencia de los p-GaN, 2-DEG y SP introducidos simultáneamente, se puede construir un modelo de conducción en estado, como se muestra esquemáticamente en la Fig. 4a. M 1 y M 2 son los transistores tipo MIS con el canal de conducción formado en p-GaN y AlGaN respectivamente. R 1 representa la parte infinitesimal de la resistencia vertical en el volumen de GaN. R 2 y R 3 representan las partes de resistencia infinitesimal del canal 2-DEG con y sin estar parcialmente agotado respectivamente. Según la ley de resistencia, R 1 , R 2 y R 3 se puede obtener como

$$ {R} _1 =\ frac {1} {n_1 q \ mu} \ bullet \ frac {l} {dx \ bullet {W} _D} $$$$ {R} _2 =\ frac {1} {n_2 q \ mu} \ bullet \ frac {dx} {t \ bullet {W} _D} $$$$ {R} _3 =\ frac {1} {n_3 q \ mu} \ bullet \ frac {dx} {t \ viñeta {W} _D} $$donde n 1 , n 2 y n 3 representan la concentración eléctrica en GaN, 2-DEG no empobrecido y 2-DEG empobrecido respectivamente; q es la carga del electrón y μ es la movilidad del electrón en GaN; l es la longitud de la ruta conductora vertical y dx es la longitud infinitesimal en el horizonte; W D es el ancho del dispositivo; y t es el espesor de 2-DEG. Para mayor comodidad, t se establece en 10 nm [7]. La concentración de 2-DEG empobrecido bajo p-GaN n 3 es igual a la concentración no completada n 1 menos la carga negativa total en el p-GaN agotado [31], que dice

$$ {n} _3 ={n} _2- {n} _A {x} _D $$

El esquema de a modelo propuesto en el estado sin SP b modelo de red de resistencia en estado con SP

El límite de p-GaN se puede considerar completamente agotado, por lo que x D es igual a 105 nm, el espesor de p-GaN. Comparado con R 1 , R 2 y R 3 son mucho más bajos que R 1 , debido a su mayor concentración de electrones y su camino conductor más corto. Por lo tanto, se puede ignorar la resistencia en el canal de 2 DEG. Además, cuando el voltaje de drenaje es pequeño y los transistores tipo MIS M 1 y M 2 trabajar en el modelo insaturado, la resistencia en estado de M 1 y M 2 puede considerarse como una resistencia constante ignorable R n . Para simplificar el cálculo, la forma analítica de la conductancia de la trayectoria de la corriente vertical G v de la trayectoria de la corriente vertical se puede obtener como

$$ {G} _v ={\ int} _0 ^ {L_D} \ frac {1} {R_1} ={\ int} _0 ^ {L_D} {n} _1 q \ mu \ bullet \ frac {dx \ bullet { W} _D} {l} $$donde L D es la longitud del dispositivo.

Por lo tanto, la resistencia del estado R en se puede obtener, que dice

$$ {R} _ {on} =\ frac {1} {G_v} + {R} _n =\ frac {1} {n_1 q \ mu} \ bullet \ frac {l} {L_D \ bullet {W} _D } + {R} _n $$Cuando existe SP, como se muestra en la Fig. 4b, el camino conductor vertical se ha bloqueado parcialmente. Por lo tanto, la conductancia de la ruta de la corriente vertical se puede expresar como

$$ {G} _v ={\ int} _ {L_W} ^ {L _ {\ mathrm {D}}} \ frac {1} {R_1} ={\ int} _ {L_W} ^ {L_D} {n} _1 q \ mu \ bullet \ frac {dx \ bullet {W} _D} {l} $$donde L W es la longitud del SP.

Por lo tanto, la R correspondiente en se puede expresar como

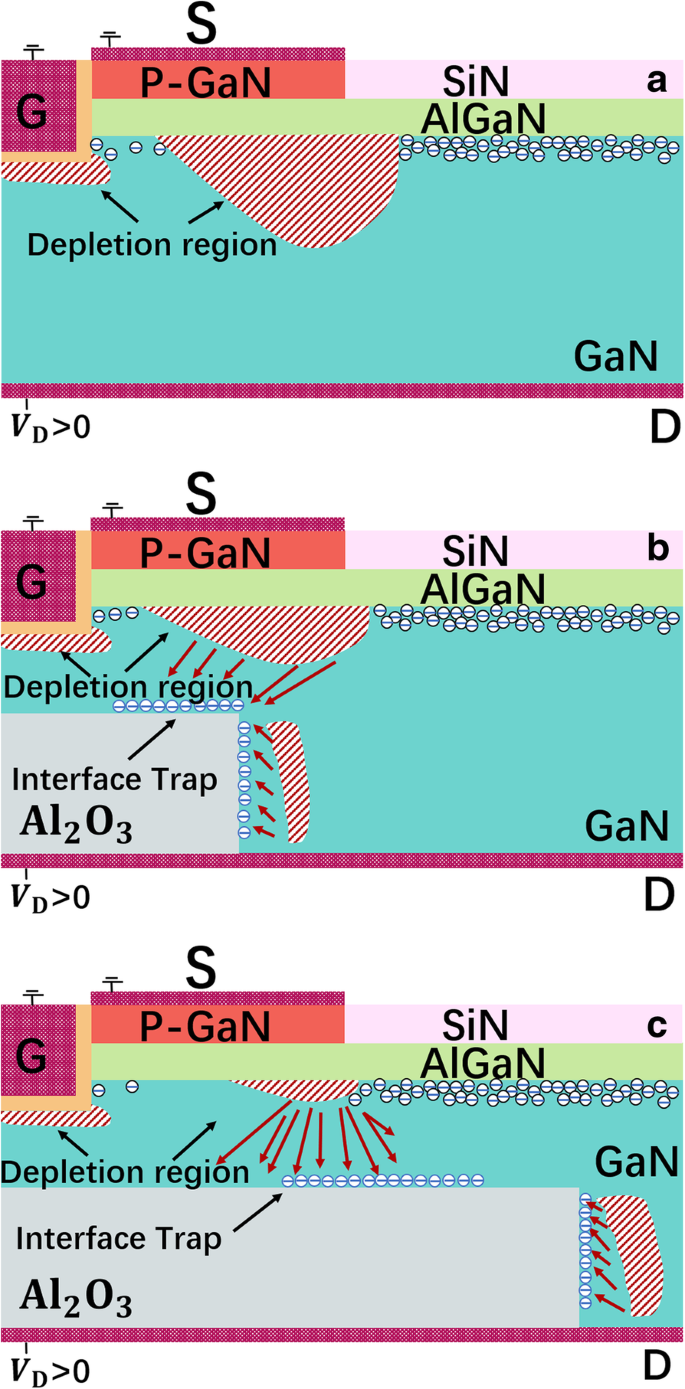

$$ {R} _ {on} =\ frac {1} {G_v} + {R} _n =\ frac {1} {n_1 q \ mu} \ bullet \ frac {l} {\ left ({L} _D - {L} _W \ right) \ bullet {W} _D} + {R} _n $$En estado apagado, debido a la funcionalidad similar a un condensador y la trampa de interfaz cargada negativamente, el SP redistribuiría el campo eléctrico debajo del límite de p-GaN de manera efectiva, produciendo una concentración de campo alrededor del SP que posee una banda prohibida más amplia como se muestra en Fig. 5. Tal redistribución del campo E encoge la región de agotamiento que aparece alrededor de p-GaN y la puerta, y por lo tanto alivia la alta concentración de campo alrededor de la tapa de p-GaN y la puerta, lo que mejoraría el BV del SP-VFET. notablemente. Por otro lado, como se mencionó anteriormente, el SP influiría en la conductancia del dispositivo de manera que la carga negativa introducida por el SP conduce al aumento de energía potencial cerca de la puerta, lo que explica la disminución de 2-DEG cerca de la puerta. Como resultado, se lograría un BFOM fluctuante al variar la longitud y la altura del SP.

La distribución esquemática del campo eléctrico y la región de agotamiento en a el dispositivo sin el SP, b el SP-VFET propuesto con un SP corto y c el SP-VFET propuesto con un SP largo

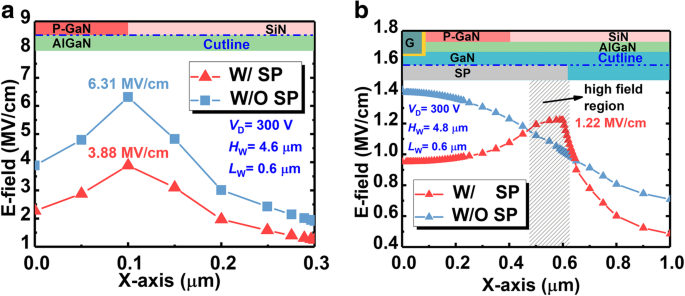

En otras palabras, el SP podría reducir el pico del campo E alrededor de la esquina de p-GaN y, simultáneamente, atraer el campo E concentrándose a través del SP, como se muestra en la Fig. 6a, b. Sin embargo, gracias al campo E crítico más alto del SP, tal concentración de campo E no rompería el dispositivo, por lo que el SP-VFET exhibiría un BV mucho más alto.

La distribución del campo eléctrico del SP-VFET propuesto a lo largo de la interfaz de a p-GaN / AlGaN y b GaN / SP

Resultado y discusión

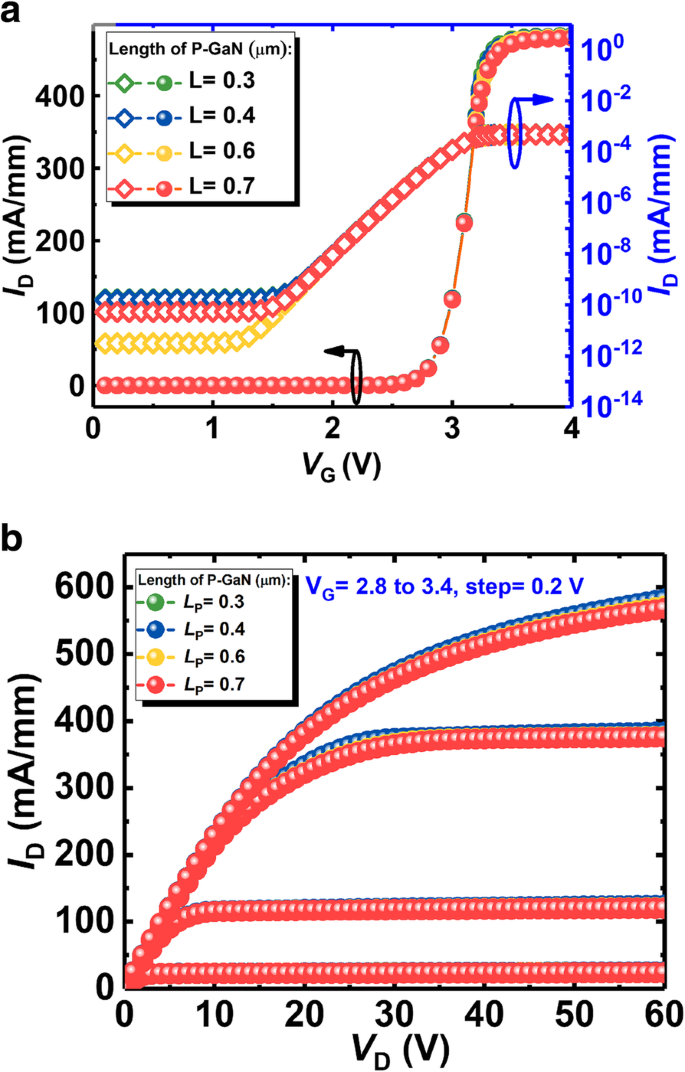

La Figura 7a, b muestra respectivamente las curvas de transferencia y salida del dispositivo propuesto sin el SP. Con diferente longitud del límite de p-GaN, estas curvas se superponen entre sí en los regímenes de activación y subumbral, lo que sugiere que la longitud del límite de p-GaN no influye en la conductancia del dispositivo sin el SP. En otras palabras, aunque el límite de p-GaN agotaría parcialmente el 2-DEG y por lo tanto afectaría la resistencia del canal de 2-DEG, el 2-DEG restante todavía posee una gran concentración n 3 que se aproxima a la concentración no completada n 2 , que se realiza optimizando la concentración de tipo p en el límite de p-GaN. Además, como se analizó anteriormente, la resistencia del canal 2-DEG es bastante pequeña en comparación con la resistencia del n-GaN en la trayectoria vertical. Por lo tanto, las curvas de transferencia se superponen entre sí en la Fig. 7a, b. Sin embargo, para proteger la puerta del campo E altamente concentrado, tal aglomeración no debe ser adyacente a la puerta, lo que significa que la longitud del p-GaN no puede ser demasiado corta. Por lo tanto, la longitud mínima de p-GaN en nuestro trabajo es de 400 nm a menos que se indique lo contrario.

un Las curvas de transferencia y b curvas de salida del dispositivo sin el SP en diferentes longitudes de la tapa de p-GaN

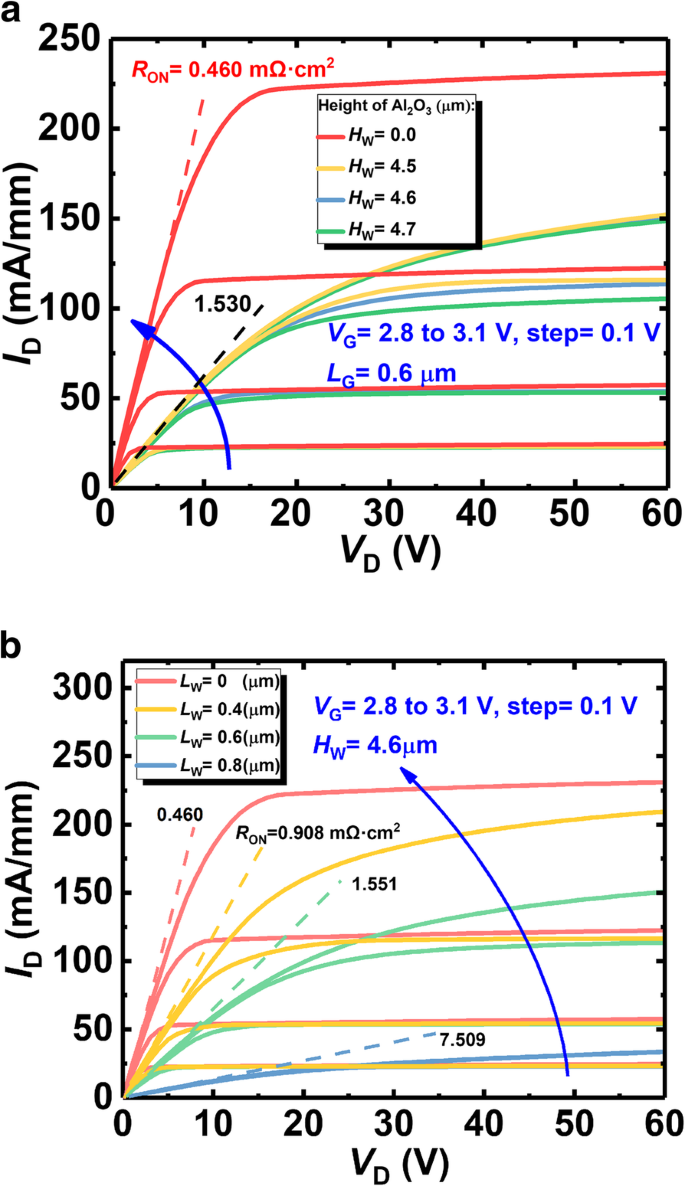

La Figura 8 muestra las características de salida del SP-VFET propuesto y el VFET sin el SP. Puede verse que el SP impone la resistencia del dispositivo al estrechar el canal de conducción vertical. En detalle, la resistencia en estado es independiente de la altura del SP cuando la altura es inferior a 4,7 μm, mientras que depende significativamente de la longitud del SP que coincide con el mecanismo de que la ruta de corriente vertical estrecha reduce la conductancia. La primera independencia se debe a que el 2DEG es el principal canal de conducción lateral que no sería debilitado por el SP dentro de su altura moderada. Sin embargo, si el SP es adyacente al canal de 2 DEG, la carga negativa introducida alrededor del SP nivelará la banda de energía, lo que resultará en una disminución drástica de la concentración de 2 DEG. En consecuencia, la resistencia de 2-DEG aumenta y la resistencia total en estado R en aumenta en consecuencia. Además, la dependencia posterior proviene de la resistencia notablemente aumentada en el canal vertical como se mencionó anteriormente. Además, debe tenerse en cuenta que los defectos de celosía en 2-DEG inducidos por un SP alto limitan la altura de SP.

Las curvas de salida del SP-VFET propuesto con a SP ancho y b Longitud de SP en comparación con el dispositivo sin SP

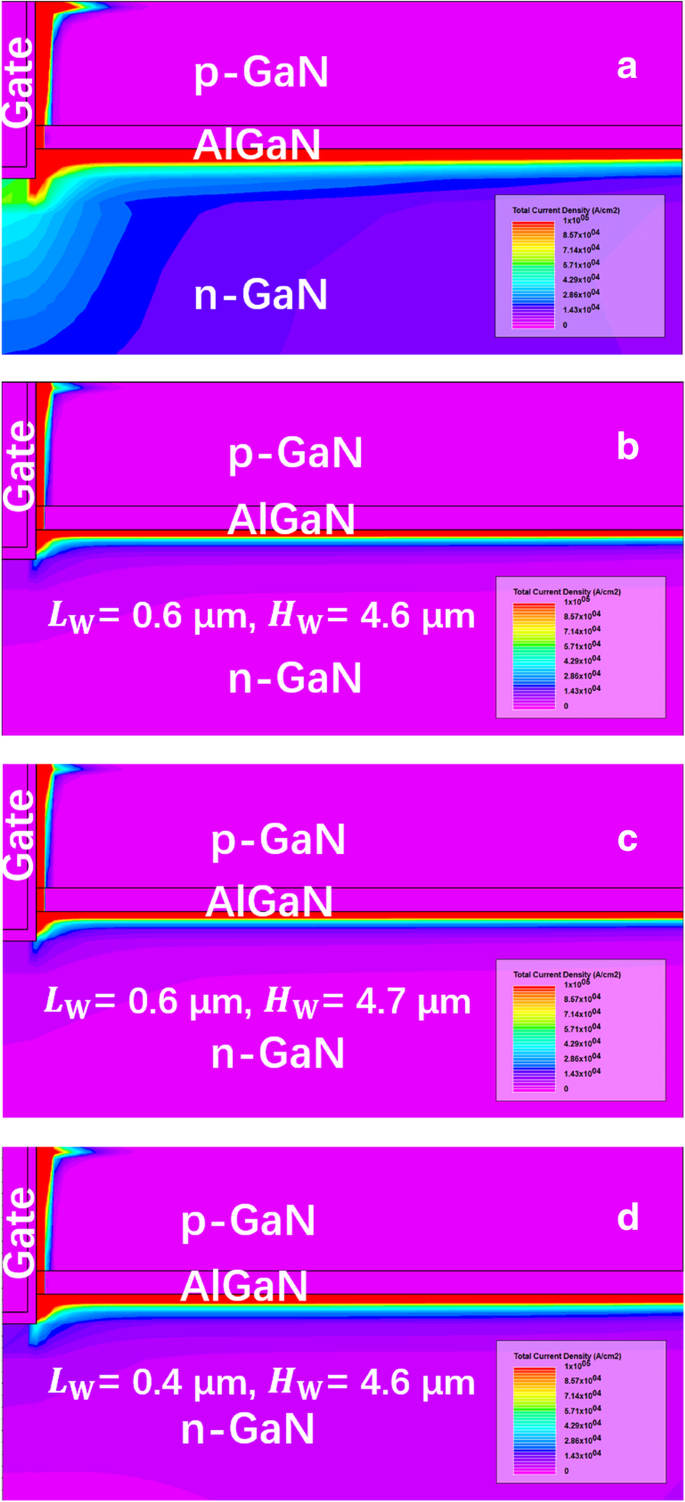

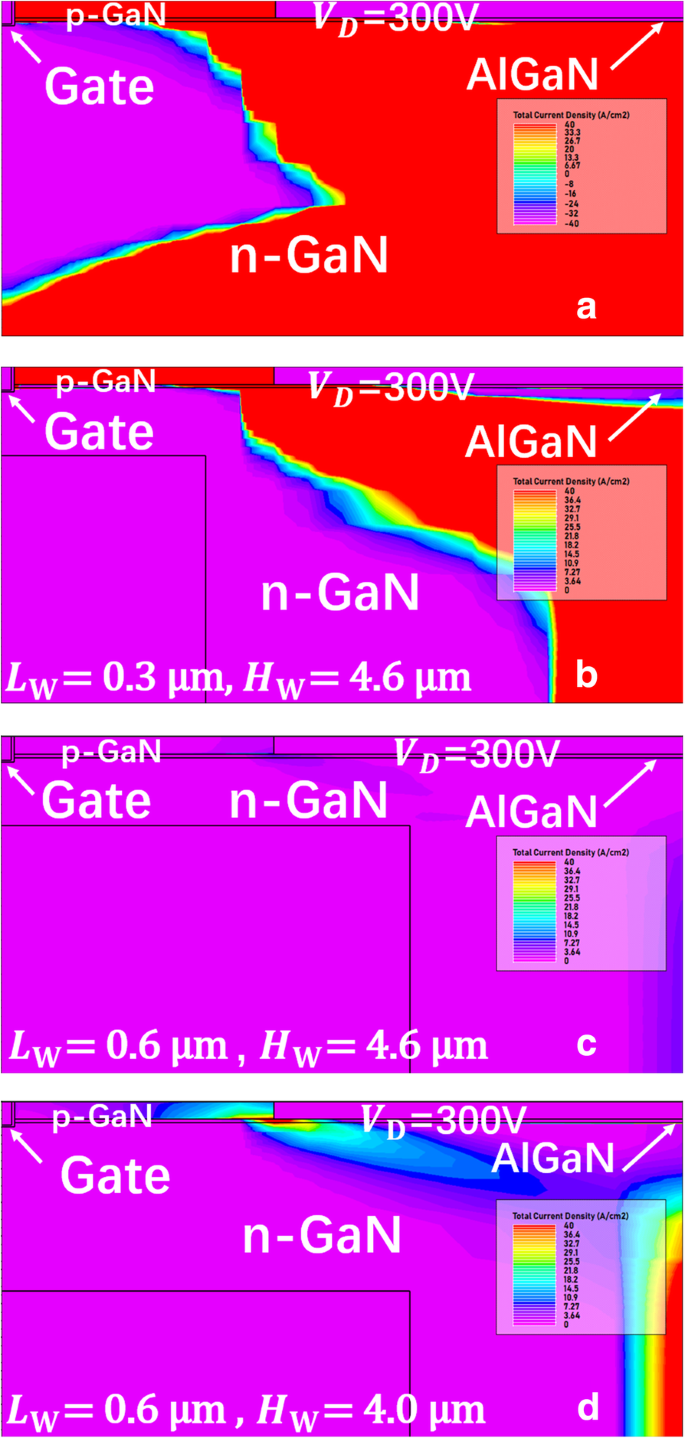

La Figura 9 muestra los detalles de la distribución de la densidad de corriente alrededor de la puerta de los dispositivos VFET con o sin el SP, en donde el VFET sin el SP tiene una capacidad de transporte de corriente más alta que se mantiene en línea con la Fig. 8a. Y al contrario, el SP-VFET contrae la conducción de corriente al estrechar el canal vertical. Mientras tanto, las figuras detalladas ilustran claramente que la corriente en el canal lateral es transportada por el 2DEG, y la densidad de corriente total cambia ligeramente con el aumento de la altura del SP, lo que también se demuestra en la sección del mecanismo. Los resultados indican que la resistencia del canal lateral no es impuesta notablemente por el SP dentro de una altura moderada.

La densidad actual de a el dispositivo sin el SP y b - d el SP-VFET propuesto con diferentes parámetros geométricos de SP

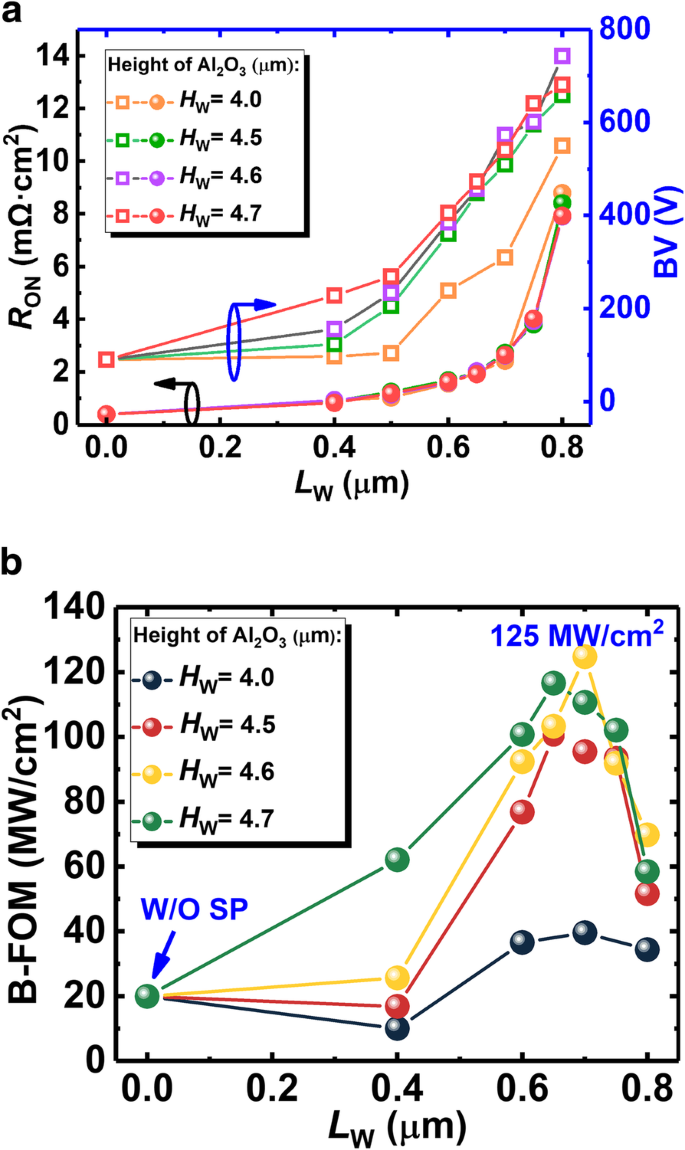

La Figura 10a muestra la resistencia en estado activado extraída y el BV correspondiente. La resistencia del SP-VFET aumenta con un SP más largo. Y especialmente, la curva de la resistencia frente a la longitud del SP presenta una tendencia hiperbólica y el gradiente de la curva aumenta con la longitud del SP más larga. Como se analizó antes, R en varía con diferentes longitudes de SP L W en forma de función hiperbólica, que coincide con el resultado de la simulación. Además, la curva de la resistencia con diferentes alturas de SP se superpone entre sí, ya que la altura es inferior a 4,7 μm, lo que sugiere que el canal de 2 DEG es el camino conductor lateral principal y el canal de 2 DEG no se ve afectado, como se mencionó anteriormente.

un La resistencia en estado activado extraída, así como BV y b el BFOM correspondiente del SP-VFET propuesto en diferentes longitudes y anchos de SP

La Figura 10b muestra el BFOM calculado del SP-VFET. Debido a la diferente tasa de aumento de BV y la resistencia en estado, el BFOM de todos los dispositivos primero crece y luego cae después de la longitud del SP superior a 400 nm. Un pico de BFOM de 125 MW / cm 2 se consigue cuando la longitud alcanza los 700 nm y la altura alcanza los 4,6 μm. Comparado con el dispositivo sin el SP, el SP-VFET propuesto funciona más de seis veces mejor en términos de BFOM.

Esta mejora se logra gracias a la supresión del campo E alto bajo el p-GaN, gracias a la trampa de interfaz cargada negativamente alrededor del SP. La interacción, que se produce entre la carga negativa atrapada en la interfaz del SP y la región de agotamiento alrededor del p-GaN, forma una nueva distribución del campo E principalmente hacia la carga atrapada. Según la ley de Gauss, el flujo eléctrico está limitado por la carga rodeada. Por lo tanto, el campo E introducido afectará el flujo eléctrico hacia otra parte. Como la carga negativa de la región de agotamiento es la fuente principal del campo E saturado alrededor de p-GaN, el campo E introducido por la carga atrapada desempeñará un papel en la supresión del campo E agitado alrededor de p-GaN y, en consecuencia, BV se mejora. Específicamente, cuando la longitud de SP es inferior a 400 nm, la carga negativa introducida por SP está lejos de la región de agotamiento. Por tanto, el campo E formado entre la región de agotamiento y la carga negativa atrapada es demasiado pequeño para influir en el campo E saturado bajo p-GaN. Y como resultado, el BV del dispositivo crece ligeramente. Sin embargo, como la longitud del SP es superior a 400 nm, debido a la carga negativa más atrapada en la interfaz del SP y la distancia más corta entre la región de agotamiento y la carga negativa atrapada, el campo E entre la región de agotamiento y la carga negativa atrapada es mejorado, lo que lleva al crecimiento de BV.

Además, la región alrededor del SP está enormemente agotada debido a la carga negativa introducida por SP. Y como se muestra en la Fig. 11, con el SP más largo, la trayectoria de la corriente de fuga vertical se estrecha debido a que la región agotada se aprieta hacia el borde del dispositivo, lo que también bloquea la corriente de fuga y, en consecuencia, mejora el BV. Por lo tanto, el BV aumenta notablemente con el aumento de la longitud del SP.

La densidad de corriente de fuga de a el dispositivo sin el SP y b - d el SP-VFET propuesto con diferentes parámetros geométricos de SP

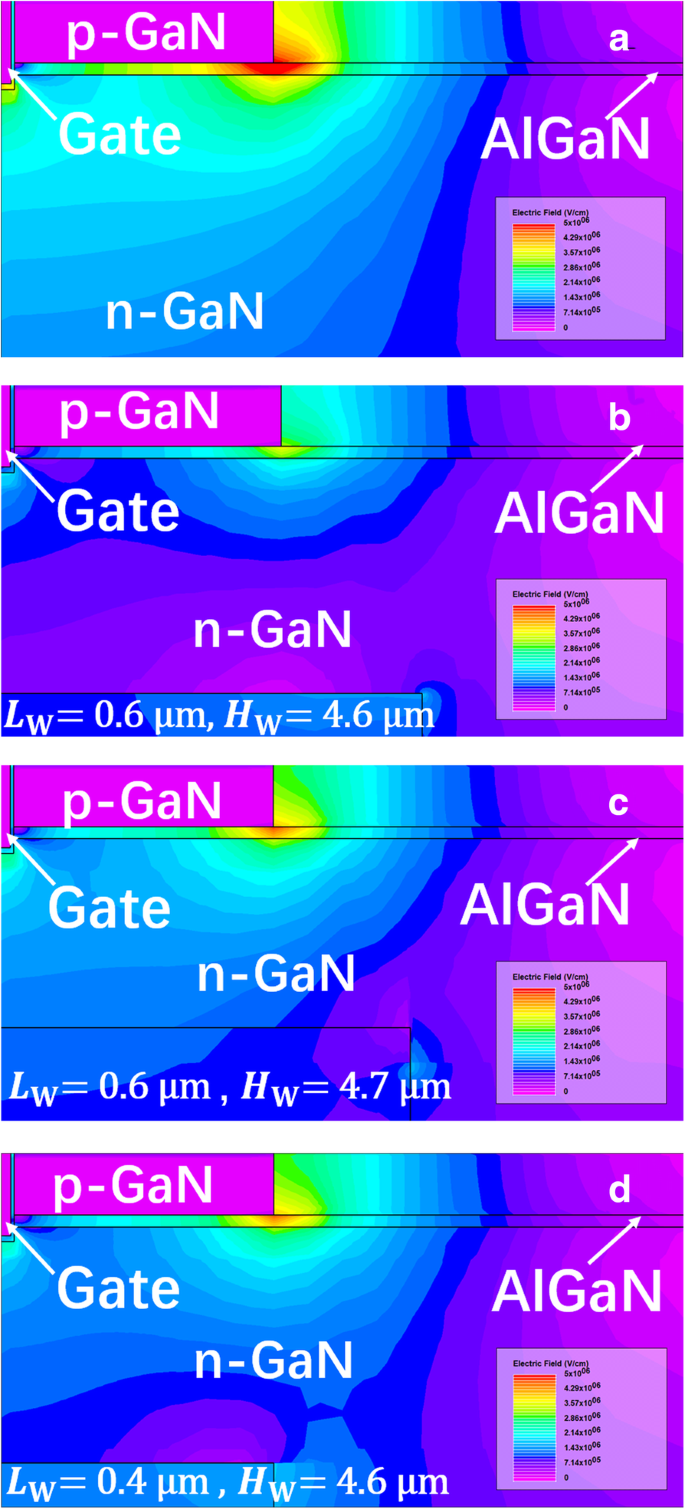

La Figura 12 muestra la distribución del campo E simulado en el SP-VFET cuando el voltaje de drenaje es de 300 V, donde aparentemente el SP induce otros nuevos puntos de concentración del campo E, lo que significa que se suprime la región del campo E pico bajo el p-GaN . En comparación con la distribución del campo E en los dispositivos con diferentes alturas de SP, el aumento de la longitud de SP suprime la congregación del campo E y, en consecuencia, mejora el BV de manera más eficiente.

La distribución del campo E alrededor de la puerta del VFET a con o b - d sin el SP cuando el voltaje de drenaje es de 300 V

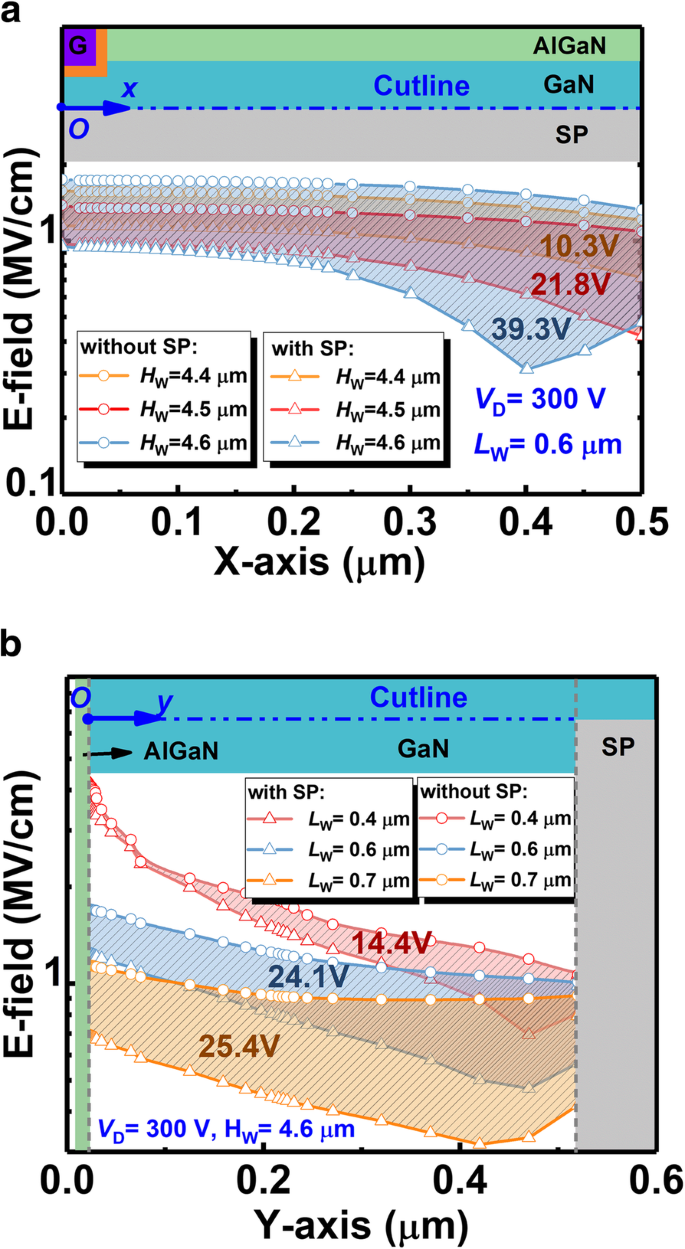

Este campo E aplanado también podría observarse explícitamente en la Fig. 13, en la que se trazan las distribuciones del campo E a lo largo del borde horizontal y perpendicular del SP (ver la línea de corte). Como se demuestra en la Fig.12 policromada, se puede ver en la Fig.13 que un SP más alto y más largo juega un papel cada vez más efectivo en la reconstrucción del campo E bajo p-GaN, y en la atracción del campo E para que se concentre a través del SP. borde. Esta redistribución contrarresta el campo E alrededor de p-GaN vulnerable. Por lo tanto, el BV del dispositivo se mejora, aumentando el B-FOM del SP-VFET propuesto.

La distribución del campo electrónico a horizontalmente y b extraído perpendicularmente a lo largo de la línea de corte del borde SP en el SP-VFET

Conclusión

En este trabajo, se propone e investiga un nuevo FET vertical de GaN de tipo mejora (SP-VFET) con canal 2DEG y patrón de sustrato para mejorar el BFOM del mismo. Verificado por simulación calibrada experimentalmente implementada con ATLAS, es el SP el que alivia el pico del campo E bajo el p-GaN y, simultáneamente, atrae una nueva concentración de campo E a través del SP que posee un campo E crítico más alto. En consecuencia, el BV del SP-VFET propuesto se ve reforzado con una resistencia en estado de aumento moderado debido a la compensación 2DEG. Por lo tanto, el BFOM del SP-VFET se mejora seis veces mejor que el del dispositivo sin el SP cuando la longitud y la altura del SP son 700 nm y 4,6 μm respectivamente, lo que convierte el potencial prometedor del SP-VFET propuesto en potencia de alta densidad. integración.

Abreviaturas

- n A :

-

Concentración de dopaje de GaN tipo p

- n D :

-

Concentración de dopaje de GaN tipo n

- 2DEG:

-

Gas de electrones bidimensionales

- Al 0.23 GaN:

-

Nitruro de galio y aluminio con una fracción molar de 0,23 para el aluminio

- Al 2 O 3 :

-

Óxido de aluminio

- BFOM:

-

Figura de méritos de Baliga

- D SP :

-

Densidad de trampa de interfaz del patrón del sustrato

- Campo electrónico:

-

Campo eléctrico

- E T :

-

La diferencia entre la banda de conducción y el nivel de energía de la trampa de interfaz

- FET:

-

Transistor de efecto de campo

- GaN:

-

Nitruro de galio

- HEMT:

-

Transistor de alta movilidad de electrones

- H G :

-

Altura de la puerta

- H W :

-

Altura del patrón del sustrato

- L D :

-

Longitud del dispositivo

- L G :

-

Longitud de la puerta

- L P :

-

Longitud de la tapa de p-GaN

- L W :

-

Longitud del patrón del sustrato

- SiN:

-

Nitruro de silicio

- SP:

-

Patrón de sustrato

- SP-VFET:

-

Transistor de efecto de campo vertical con patrón de sustrato

- W D :

-

Profundidad del dispositivo

- σ p :

-

Carga de polarización

Nanomateriales

- En la carretera con IoT

- Impacto de los estados de la superficie y la fracción molar de aluminio en el potencial de la superficie y 2DEG en los HEMT de AlGaN / GaN

- Modulación de las propiedades de anisotropía óptica y electrónica de ML-GaS por campo eléctrico vertical

- El efecto del plasma de no equilibrio por contacto sobre las propiedades estructurales y magnéticas de Mn Х Fe3 - X О4 Espinelas

- Efecto del tratamiento de recocido in situ sobre la movilidad y morfología de transistores de efecto de campo orgánico basados en TIPS-pentaceno

- Síntesis controlada de BaYF5:Er3 +, Yb3 + con morfología diferente para la mejora de la luminiscencia de conversión ascendente

- Efectos de la fotoconductividad, la sensibilidad al pH, el ruido y la longitud del canal en los sensores FET de nanocables de Si

- Síntesis verde de nanopartículas de metal y óxido de metal y su efecto sobre el alga unicelular Chlamydomonas reinhardtii

- Efecto de la morfología y la estructura cristalina en la conductividad térmica de los nanotubos de titania

- Preparación de una matriz periódica de nanoesferas de poliestireno utilizando el método de inmersión con grabado posterior a la deposición y su aplicación para mejorar la eficiencia de extracció…

- Influencia del sustrato en la longitud de onda y resistencia del acoplamiento LSP