LFSR en una FPGA – VHDL y código Verilog Cómo funciona un registro de desplazamiento de retroalimentación lineal dentro de una FPGA LFSR significa Registro de desplazamiento de retroalimentación lineal y es un diseño que es útil dentro de los FPGA. Los LFSR son fáciles de sintetizar, lo que signifi

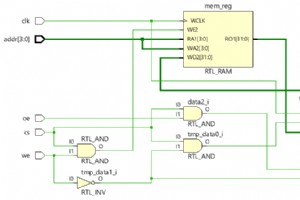

Diseño module single_port_sync_ram # (parameter ADDR_WIDTH = 4, parameter DATA_WIDTH = 32, parameter DEPTH = 16 ) ( input clk, input [ADDR_WIDTH-1:0] addr, inout [DATA_WIDTH-1:0] data, input cs, input we, input oe ); re

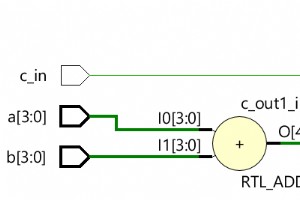

Un sumador es un componente digital que realiza la suma de dos números. Es el componente principal dentro de una ALU de un procesador y se usa para incrementar direcciones, índices de tablas, punteros de búfer y en muchos otros lugares donde se requiere agregar. Un sumador completo agrega una entra

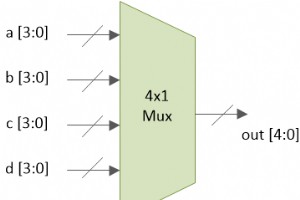

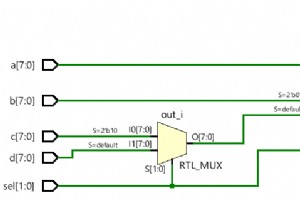

¿Qué es un mux o multiplexor? Un multiplexor o mux en resumen, es un elemento digital que transfiere datos de una de las N entradas a la salida en función de la señal seleccionada. El caso que se muestra a continuación es cuando N es igual a 4. Por ejemplo, un multiplexor de 4 bits tendría N entrad

Diseño module pr_en ( input [7:0] a, input [7:0] b, input [7:0] c, input [7:0] d, input [1:0] sel, output reg [7:0] out); always @ (a or b or c or d or sel) begin if (sel == 2b00) out <= a; else

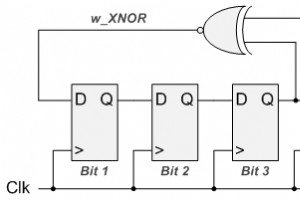

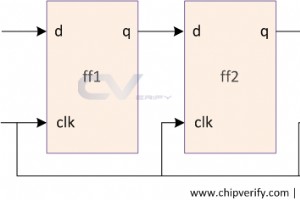

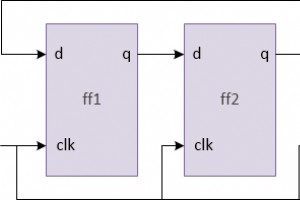

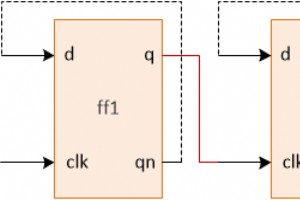

En electrónica digital, un registro de desplazamiento es una cascada de flip-flops donde el pin de salida q de un flop está conectado al pin de entrada de datos (d) del siguiente. Debido a que todos los flops funcionan en el mismo reloj, la matriz de bits almacenada en el registro de desplazamiento

Diseño module gray_ctr # (parameter N = 4) ( input clk, input rstn, output reg [N-1:0] out); reg [N-1:0] q; always @ (posedge clk) begin if (!rstn) begin q <= 0; out <= 0; end else begin q <= q + 1; `ifdef FOR_LOOP for (int i

Diseño module modN_ctr # (parameter N = 10, parameter WIDTH = 4) ( input clk, input rstn, output reg[WIDTH-1:0] out); always @ (posedge clk) begin if (!rstn) begin out <= 0; end else begin if (out == N-1) out <= 0; else ou

Diseño module johnson_ctr #(parameter WIDTH=4) ( input clk, input rstn, output reg [WIDTH-1:0] out ); always @ (posedge clk) begin if (!rstn) out <= 1; else begin out[WIDTH-1] <= ~out[0]; for (int i = 0; i < WIDTH-1; i=i+1

Diseño module ring_ctr #(parameter WIDTH=4) ( input clk, input rstn, output reg [WIDTH-1:0] out ); always @ (posedge clk) begin if (!rstn) out <= 1; else begin out[WIDTH-1] <= out[0]; for (int i = 0; i < WIDTH-1; i=i+1) b

Una onda counter es un contador asíncrono en el que todos los flop, excepto el primero, son cronometrados por la salida del flop anterior. Diseño module dff ( input d, input clk, input rstn, output reg q, output qn); always @ (p

El contador de 4 bits comienza a incrementarse de 4b0000 a 4h1111 y luego vuelve a 4b0000. Seguirá contando siempre que tenga un reloj en marcha y el reinicio se mantenga alto. El rollover ocurre cuando se descarta la parte más significativa de la adición final. Cuando el contador tiene un valor má

Un flip-flop captura datos en su entrada en el borde positivo o negativo de un reloj. Lo importante a tener en cuenta es que lo que suceda con los datos después del borde del reloj hasta el siguiente borde del reloj no se reflejará en la salida. Un pestillo por otro lado, no captura en el borde de u

Diseño module tff ( input clk, input rstn, input t, output reg q); always @ (posedge clk) begin if (!rstn) q <= 0; else if (t) q <= ~q; else q <= q; end endmodule Banco de pruebas module tb; reg clk

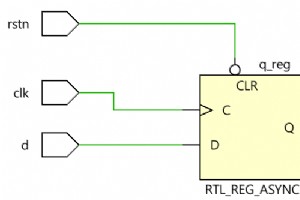

Una chancleta D es un elemento secuencial que sigue al pin de entrada d en el borde dado de un reloj. Diseño n.º 1:con reinicio asíncrono activo-bajo module dff ( input d, input rstn, input clk, output reg q); always @ (posedge clk or negedge rstn)

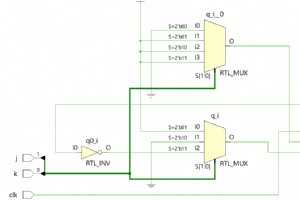

Diseño module jk_ff ( input j, input k, input clk, output q); reg q; always @ (posedge clk) case ({j,k}) 2b00 : q <= q; 2b01 : q <= 0; 2b10 : q <= 1; 2b11 : q <= ~q; endcase endmodule Esq

Siempre es mejor comenzar usando un ejemplo muy simple, y ninguno sirve mejor para el propósito que no sea ¡Hola mundo!. // Single line comments start with double forward slash // // Verilog code is always written inside modules, and each module represents a digital block with some functionalit

Verilog tiene tareas y funciones del sistema que pueden abrir archivos, generar valores en archivos, leer valores de archivos y cargar en otras variables y cerrar archivos. Abrir y cerrar archivos module tb; // Declare a variable to store the file handler integer fd; initial begin // Ope

Escala de tiempo predeterminada Aunque se espera que los módulos de Verilog tengan una escala de tiempo definida antes del módulo, los simuladores pueden insertar una escala de tiempo predeterminada. La escala de tiempo real que se aplica en cualquier ámbito en una jerarquía elaborada de Verilog se

La directiva de escala de tiempo de Verilog especifica la unidad de tiempo y la precisión para las simulaciones. Verilog $timeformat función del sistema especifica %t estilo de informe del especificador de formato en declaraciones de visualización como $display y $strobe . Sintaxis $timeformat

Verilog