Multiplexor/Mux Verilog 4 a 1

¿Qué es un mux o multiplexor?

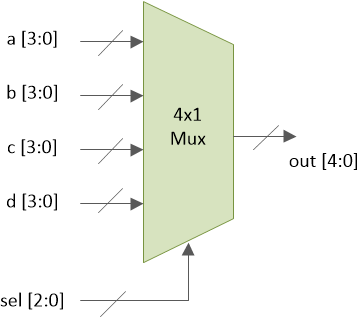

Un multiplexor o mux en resumen, es un elemento digital que transfiere datos de una de las N entradas a la salida en función de la señal seleccionada. El caso que se muestra a continuación es cuando N es igual a 4. Por ejemplo, un multiplexor de 4 bits tendría N entradas cada una de 4 bits donde cada entrada puede transferirse a la salida mediante el uso de una señal de selección.

sel es una entrada de 2 bits y puede tener cuatro valores. Cada valor en la línea de selección permitirá que una de las entradas se envíe al pin de salida.

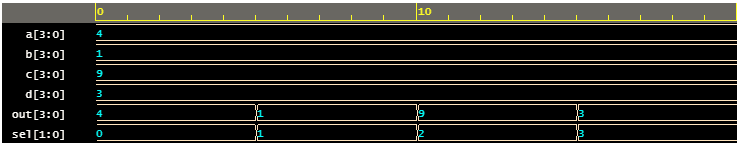

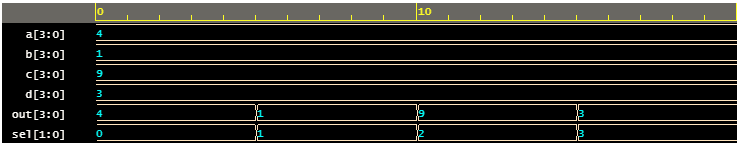

sel a b c d out 0 3 7 1 9 3 1 3 7 1 9 7 2 3 7 1 9 1 3 3 7 1 9 9

Un multiplexor 4x1 se puede implementar de varias formas y aquí verá dos de las formas más comunes:

- Usando un

assigndeclaración - Usando un

casedeclaración

Usando assign declaración

module mux_4to1_assign ( input [3:0] a, // 4-bit input called a

input [3:0] b, // 4-bit input called b

input [3:0] c, // 4-bit input called c

input [3:0] d, // 4-bit input called d

input [1:0] sel, // input sel used to select between a,b,c,d

output [3:0] out); // 4-bit output based on input sel

// When sel[1] is 0, (sel[0]? b:a) is selected and when sel[1] is 1, (sel[0] ? d:c) is taken

// When sel[0] is 0, a is sent to output, else b and when sel[0] is 0, c is sent to output, else d

assign out = sel[1] ? (sel[0] ? d : c) : (sel[0] ? b : a);

endmodule

El módulo llamado mux_4x1_assign tiene cuatro entradas de datos de 4 bits, una entrada de selección de 2 bits y una salida de datos de 4 bits. El multiplexor seleccionará a , b, c o d en función de la señal seleccionada sel utilizando el assign declaración.

Usando case declaración

Tenga en cuenta que la señal de salida se declara como reg porque se usa en un procedimiento bloquear como always .

module mux_4to1_case ( input [3:0] a, // 4-bit input called a

input [3:0] b, // 4-bit input called b

input [3:0] c, // 4-bit input called c

input [3:0] d, // 4-bit input called d

input [1:0] sel, // input sel used to select between a,b,c,d

output reg [3:0] out); // 4-bit output based on input sel

// This always block gets executed whenever a/b/c/d/sel changes value

// When that happens, based on value in sel, output is assigned to either a/b/c/d

always @ (a or b or c or d or sel) begin

case (sel)

2'b00 : out <= a;

2'b01 : out <= b;

2'b10 : out <= c;

2'b11 : out <= d;

endcase

end

endmodule

El módulo llamado mux_4x1_case tiene cuatro entradas de datos de 4 bits, una entrada de selección de 2 bits y una salida de datos de 4 bits. El multiplexor seleccionará a , b, c o d en función de la señal seleccionada sel utilizando el case declaración.

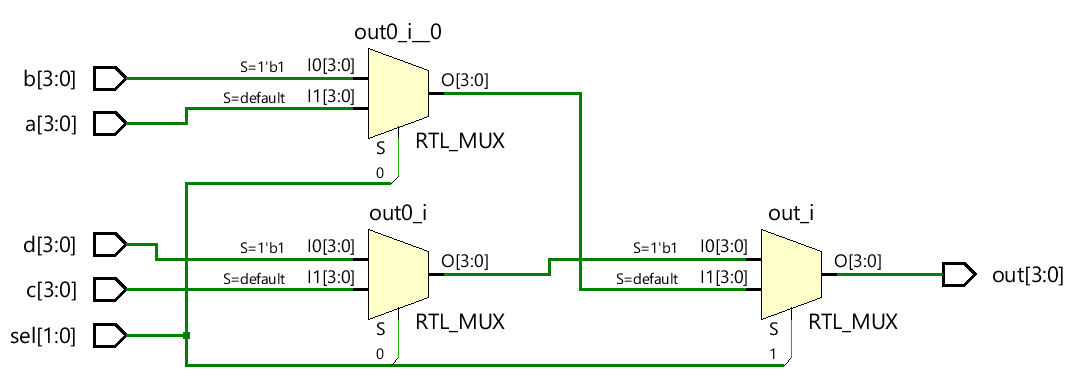

Esquema de hardware

Ambos tipos de modelos de multiplexor se sintetizan en el mismo hardware, como se muestra en la imagen a continuación.

Banco de pruebas

module tb_4to1_mux;

// Declare internal reg variables to drive design inputs

// Declare wire signals to collect design output

// Declare other internal variables used in testbench

reg [3:0] a;

reg [3:0] b;

reg [3:0] c;

reg [3:0] d;

wire [3:0] out;

reg [1:0] sel;

integer i;

// Instantiate one of the designs, in this case, we have used the design with case statement

// Connect testbench variables declared above with those in the design

mux_4to1_case mux0 ( .a (a),

.b (b),

.c (c),

.d (d),

.sel (sel),

.out (out));

// This initial block is the stimulus

initial begin

// Launch a monitor in background to display values to log whenever a/b/c/d/sel/out changes

$monitor ("[%0t] sel=0x%0h a=0x%0h b=0x%0h c=0x%0h d=0x%0h out=0x%0h", $time, sel, a, b, c, d, out);

// 1. At time 0, drive random values to a/b/c/d and keep sel = 0

sel <= 0;

a <= $random;

b <= $random;

c <= $random;

d <= $random;

// 2. Change the value of sel after every 5ns

for (i = 1; i < 4; i=i+1) begin

#5 sel <= i;

end

// 3. After Step2 is over, wait for 5ns and finish simulation

#5 $finish;

end

endmodule

Registro de simulación ncsim> run [0] sel=0x0 a=0x4 b=0x1 c=0x9 d=0x3 out=0x4 [5] sel=0x1 a=0x4 b=0x1 c=0x9 d=0x3 out=0x1 [10] sel=0x2 a=0x4 b=0x1 c=0x9 d=0x3 out=0x9 [15] sel=0x3 a=0x4 b=0x1 c=0x9 d=0x3 out=0x3 Simulation complete via $finish(1) at time 20 NS + 0

Verilog

- Tutorial de Verilog

- Concatenación Verilog

- Asignaciones de Verilog

- Bloqueo y no bloqueo de Verilog

- Funciones de Verilog

- Tarea Verilog

- Generador de reloj Verilog

- Funciones matemáticas de Verilog

- Formato de hora de Verilog

- Alcance de la escala de tiempo de Verilog

- Operaciones de E/S de archivos de Verilog