Sumador completo de Verilog

Un sumador es un componente digital que realiza la suma de dos números. Es el componente principal dentro de una ALU de un procesador y se usa para incrementar direcciones, índices de tablas, punteros de búfer y en muchos otros lugares donde se requiere agregar.

Un sumador completo agrega una entrada de acarreo junto con otros números binarios de entrada para producir una suma y una salida de acarreo.

Tabla de verdad

| A | B | cin | Cout | Suma |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 | 1 |

| 0 | 1 | 0 | 0 | 1 |

| 0 | 1 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 | 0 |

| 1 | 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 1 | 1 |

Diseño

A continuación se muestra un ejemplo de un sumador de 4 bits que acepta dos números binarios a través de las señales a y b, que tienen 4 bits de ancho. Dado que un sumador es un circuito combinacional, se puede modelar en Verilog usando una asignación continua con assign o un always bloque con una lista de sensibilidad que comprende todas las entradas. El código que se muestra a continuación es el del enfoque anterior.

module fulladd ( input [3:0] a,

input [3:0] b,

input c_in,

output c_out,

output [3:0] sum);

assign {c_out, sum} = a + b + c_in;

endmodule

El código que se muestra a continuación utiliza un always bloque que se ejecuta cada vez que alguna de sus entradas cambia de valor.

module fulladd ( input [3:0] a,

input [3:0] b,

input c_in,

output reg c_out,

output reg [3:0] sum);

always @ (a or b or c_in) begin

{c_out, sum} = a + b + c_in;

end

endmodule

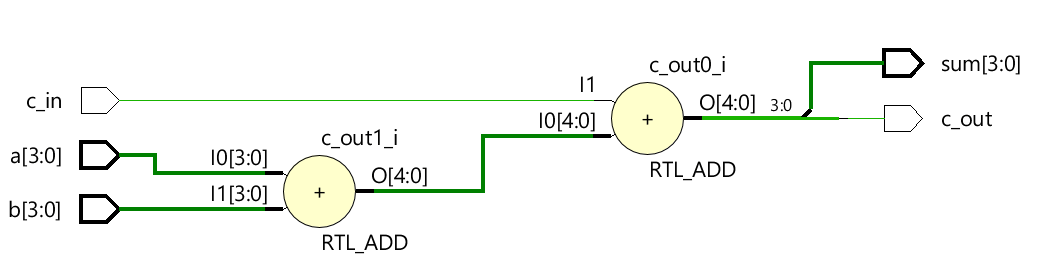

Esquema de hardware

Banco de pruebas

module tb_fulladd;

// 1. Declare testbench variables

reg [3:0] a;

reg [3:0] b;

reg c_in;

wire [3:0] sum;

integer i;

// 2. Instantiate the design and connect to testbench variables

fulladd fa0 ( .a (a),

.b (b),

.c_in (c_in),

.c_out (c_out),

.sum (sum));

// 3. Provide stimulus to test the design

initial begin

a <= 0;

b <= 0;

c_in <= 0;

$monitor ("a=0x%0h b=0x%0h c_in=0x%0h c_out=0x%0h sum=0x%0h", a, b, c_in, c_out, sum);

// Use a for loop to apply random values to the input

for (i = 0; i < 5; i = i+1) begin

#10 a <= $random;

b <= $random;

c_in <= $random;

end

end

endmodule

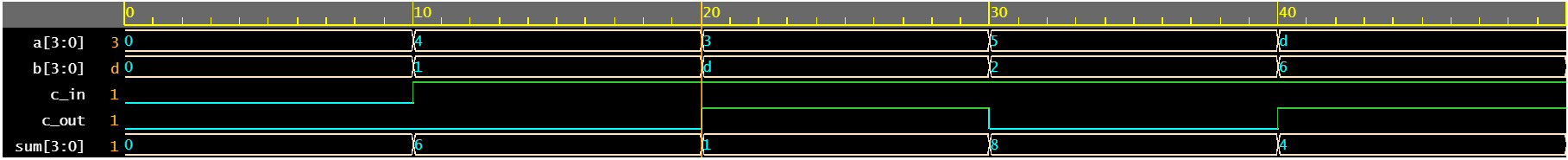

Tenga en cuenta que cuando a y b se suman para dar un número de más de 4 bits de ancho, la suma vuelve a cero y c_out se convierte en 1. Por ejemplo, la línea resaltada en amarillo se suma para dar 0x11 y los 4 bits inferiores se asignan a sum y bit#4 a c_out.

Registro de simulaciónncsim> run a=0x0 b=0x0 c_in=0x0 c_out=0x0 sum=0x0 a=0x4 b=0x1 c_in=0x1 c_out=0x0 sum=0x6 a=0x3 b=0xd c_in=0x1 c_out=0x1 sum=0x1 a=0x5 b=0x2 c_in=0x1 c_out=0x0 sum=0x8 a=0xd b=0x6 c_in=0x1 c_out=0x1 sum=0x4 a=0xd b=0xc c_in=0x1 c_out=0x1 sum=0xa ncsim: *W,RNQUIE: Simulation is complete.

Verilog

- Tutorial de Verilog

- Concatenación Verilog

- Asignaciones de Verilog

- Bloqueo y no bloqueo de Verilog

- Funciones de Verilog

- Tarea Verilog

- Generador de reloj Verilog

- Funciones matemáticas de Verilog

- Formato de hora de Verilog

- Alcance de la escala de tiempo de Verilog

- Operaciones de E/S de archivos de Verilog