Parámetros de Verilog

Los parámetros son construcciones de Verilog que permiten reutilizar un módulo con una especificación diferente. Por ejemplo, se puede parametrizar un sumador de 4 bits para aceptar un valor para el número de bits y se pueden pasar nuevos valores de parámetros durante la instanciación del módulo. Entonces, un sumador de N bits puede convertirse en un sumador de 4 bits, 8 bits o 16 bits. Son como argumentos a una función que se pasan durante una llamada de función.

parameter MSB = 7; // MSB is a parameter with a constant value 7

parameter REAL = 4.5; // REAL holds a real number

parameter FIFO_DEPTH = 256,

MAX_WIDTH = 32; // Declares two parameters

parameter [7:0] f_const = 2'b3; // 2 bit value is converted to 8 bits; 8'b3

Los parámetros son básicamente constantes y, por lo tanto, es ilegal modificar su valor en tiempo de ejecución. Es ilegal volver a declarar un nombre que ya está siendo utilizado por una red, variable u otro parámetro.

Hay dos tipos principales de parámetros, módulo y especificar y ambos aceptan una especificación de rango. Sin embargo, normalmente se hacen tan amplios como el valor que se va a almacenar los requiere y, por lo tanto, no es necesaria una especificación de rango.

Parámetros del módulo

Los parámetros del módulo se pueden usar para anular las definiciones de parámetros dentro de un módulo y esto hace que el módulo tenga un conjunto diferente de parámetros en el momento de la compilación. Un parámetro se puede modificar con el defparam sentencia o en la sentencia de instancia del módulo. Es una práctica común usar letras mayúsculas en los nombres de los parámetros para que se noten al instante.

El módulo que se muestra a continuación usa parámetros para especificar el ancho del bus, el ancho de los datos y la profundidad de FIFO dentro del diseño, y se puede anular con nuevos valores cuando se instancia el módulo o usando defparam declaraciones.

// Verilog 1995 style port declaration

module design_ip ( addr,

wdata,

write,

sel,

rdata);

parameter BUS_WIDTH = 32,

DATA_WIDTH = 64,

FIFO_DEPTH = 512;

input addr;

input wdata;

input write;

input sel;

output rdata;

wire [BUS_WIDTH-1:0] addr;

wire [DATA_WIDTH-1:0] wdata;

reg [DATA_WIDTH-1:0] rdata;

reg [7:0] fifo [FIFO_DEPTH];

// Design code goes here ...

endmodule

En el nuevo estilo ANSI de declaración de puerto Verilog, puede declarar parámetros como se muestra a continuación.

module design_ip

#(parameter BUS_WIDTH=32,

parameter DATA_WIDTH=64) (

input [BUS_WIDTH-1:0] addr,

// Other port declarations

);

Anulación de parámetros

Los parámetros se pueden anular con nuevos valores durante la instanciación del módulo. La primera parte crea una instancia del módulo llamado design_ip con el nombre d0 donde se pasan nuevos parámetros dentro de #( ) . La segunda parte usa una construcción Verilog llamada defparam para establecer los nuevos valores de los parámetros. El primer método es la forma más utilizada para pasar nuevos parámetros en diseños RTL. El segundo método se usa comúnmente en simulaciones de banco de pruebas para actualizar rápidamente los parámetros de diseño sin tener que volver a crear una instancia del módulo.

module tb;

// Module instantiation override

design_ip #(BUS_WIDTH = 64, DATA_WIDTH = 128) d0 ( [port list]);

// Use of defparam to override

defparam d0.FIFO_DEPTH = 128;

endmodule

Ejemplo

El contador del módulo tiene dos parámetros N y DOWN declarados para tener un valor predeterminado de 2 y 0 respectivamente. N controla el número de bits en la salida controlando efectivamente el ancho del contador. Por defecto es un contador de 2 bits. El parámetro DOWN controla si el contador debe aumentar o disminuir. De forma predeterminada, el contador disminuirá porque el parámetro está establecido en 0.

Contador ascendente de 2 bits

module counter

#( parameter N = 2,

parameter DOWN = 0)

( input clk,

input rstn,

input en,

output reg [N-1:0] out);

always @ (posedge clk) begin

if (!rstn) begin

out <= 0;

end else begin

if (en)

if (DOWN)

out <= out - 1;

else

out <= out + 1;

else

out <= out;

end

end

endmodule

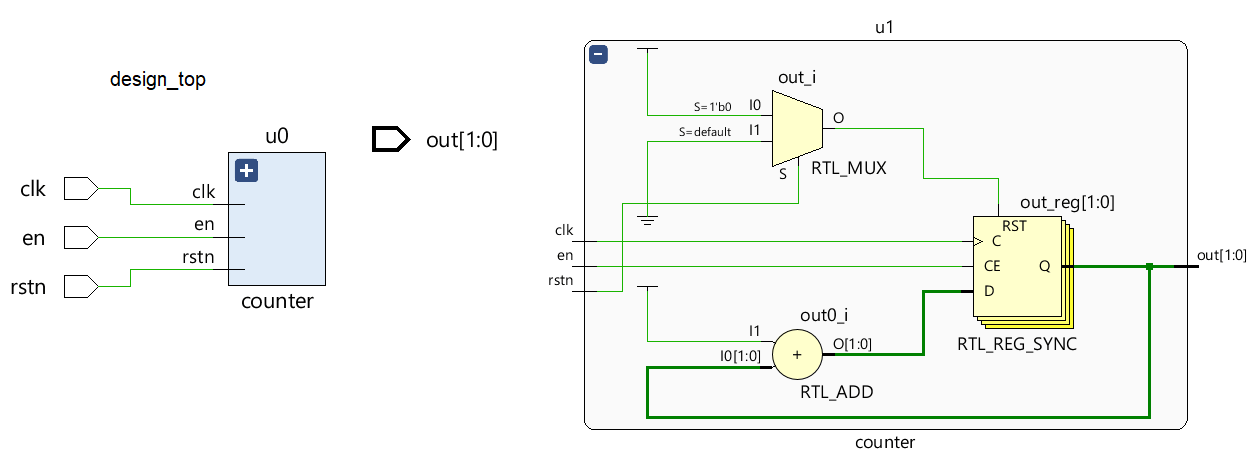

El contador del módulo se instancia con N como 2 aunque no es necesario porque el valor predeterminado es de todos modos 2. DOWN no se pasa durante la instanciación del módulo y, por lo tanto, toma el valor predeterminado de 0, lo que lo convierte en un contador ascendente.

module design_top ( input clk,

input rstn,

input en,

output [1:0] out);

counter #(.N(2)) u0 ( .clk(clk),

.rstn(rstn),

.en(en));

endmodule

Vea que los parámetros predeterminados se utilizan para implementar el contador donde N es igual a dos, lo que lo convierte en un contador de 2 bits, y DOWN es igual a cero, lo que lo convierte en un contador ascendente. La salida del contador se deja desconectada en el nivel superior.

Contador regresivo de 4 bits

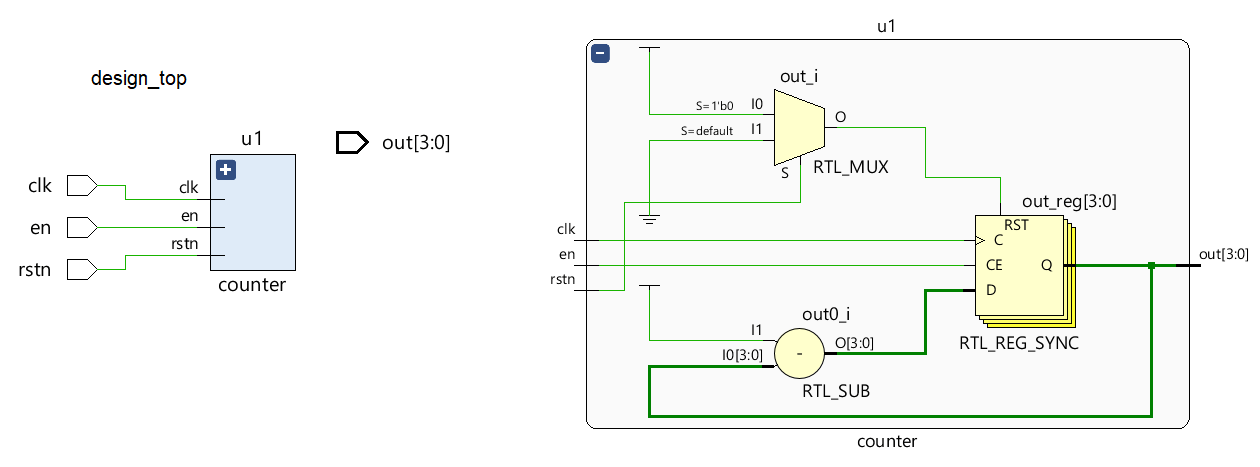

En este caso, el contador del módulo se instancia con N como 4, lo que lo convierte en un contador de 4 bits. A DOWN se le pasa un valor de 1 durante la instanciación del módulo y, por lo tanto, se implementa un contador descendente.

module design_top ( input clk,

input rstn,

input en,

output [3:0] out);

counter #(.N(4), .DOWN(1))

u1 ( .clk(clk),

.rstn(rstn),

.en(en));

endmodule

Especificar parámetros

Estos se utilizan principalmente para proporcionar valores de temporización y retraso y se declaran utilizando el specparam palabra clave. Se permite su uso tanto dentro de especificar bloque y el cuerpo del módulo principal.

// Use of specify block

specify

specparam t_rise = 200, t_fall = 150;

specparam clk_to_q = 70, d_to_q = 100;

endspecify

// Within main module

module my_block ( ... );

specparam dhold = 2.0;

specparam ddly = 1.5;

parameter WIDTH = 32;

endmodule

Diferencia entre especificar y parámetros de módulo

| Especificar parámetro | Parámetro del módulo |

|---|---|

Declarado por specparam | Declarado por parameter |

Se puede declarar dentro de specify bloque o dentro del módulo principal | Solo se puede declarar dentro del módulo principal |

| Pueden asignarse parámetros y parámetros específicos | No se pueden asignar parámetros específicos |

| SDF se puede usar para anular valores | Valores de parámetro de declaración de instancia o defparam se puede usar para anular |

Verilog