Declaración del caso Verilog

El case La instrucción comprueba si la expresión dada coincide con una de las otras expresiones de la lista y se bifurca en consecuencia. Normalmente se utiliza para implementar un multiplexor. La construcción if-else puede no ser adecuada si hay muchas condiciones que verificar y se sintetizaría en un codificador de prioridad en lugar de un multiplexor.

Sintaxis

Un caso de Verilog declaración comienza con el case palabra clave y termina con el endcase palabra clave. La expresión entre paréntesis se evaluará exactamente una vez y se comparará con la lista de alternativas en el orden en que se escriben y se ejecutan las declaraciones para las que la alternativa coincide con la expresión dada. Un bloque de declaraciones múltiples debe agruparse y estar dentro de begin y end .

// Here 'expression' should match one of the items (item 1,2,3 or 4)

case (<expression>)

case_item1 : <single statement>

case_item2,

case_item3 : <single statement>

case_item4 : begin

<multiple statements>

end

default : <statement>

endcase

Si ninguno de los elementos del caso coincide con la expresión dada, las declaraciones dentro del default se ejecuta el elemento. El default declaración es opcional, y solo puede haber un default declaración en una declaración de caso. Las declaraciones de casos se pueden anidar.

La ejecución saldrá del bloque de casos sin hacer nada si ninguno de los elementos coincide con la expresión y un default no se da declaración.

Ejemplo

El módulo de diseño que se muestra a continuación tiene una señal de selección de 2 bits para enrutar una de las otras tres entradas de 3 bits a la señal de salida indicada. Un case se utiliza para asignar la entrada correcta a la salida en función del valor de sel. Dado que sel es una señal de 2 bits, puede tener 2

2

combinaciones, de 0 a 3. La declaración predeterminada ayuda a establecer la salida en 0 si sel es 3.

module my_mux (input [2:0] a, b, c, // Three 3-bit inputs

[1:0] sel, // 2-bit select signal to choose from a, b, c

output reg [2:0] out); // Output 3-bit signal

// This always block is executed whenever a, b, c or sel changes in value

always @ (a, b, c, sel) begin

case(sel)

2'b00 : out = a; // If sel=0, output is a

2'b01 : out = b; // If sel=1, output is b

2'b10 : out = c; // If sel=2, output is c

default : out = 0; // If sel is anything else, out is always 0

endcase

end

endmodule

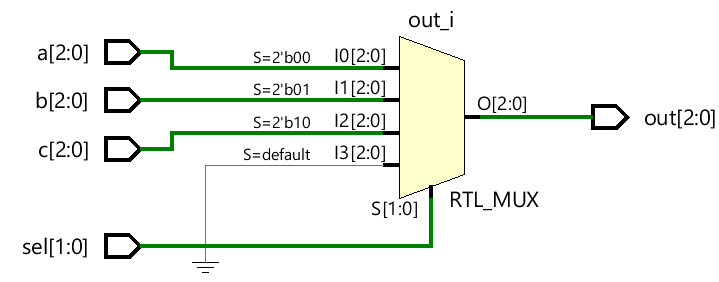

Esquema de hardware

El código rtl se elabora para obtener un esquema de hardware que representa un multiplexor 4 a 1.

Vea que la salida es cero cuando sel es 3 y corresponde a las entradas asignadas para otros valores.

Registro de simulaciónncsim> run [0] a=0x4 b=0x1 c=0x1 sel=0b11 out=0x0 [10] a=0x5 b=0x5 c=0x5 sel=0b10 out=0x5 [20] a=0x1 b=0x5 c=0x6 sel=0b01 out=0x5 [30] a=0x5 b=0x4 c=0x1 sel=0b10 out=0x1 [40] a=0x5 b=0x2 c=0x5 sel=0b11 out=0x0 ncsim: *W,RNQUIE: Simulation is complete.

En una declaración de caso, la comparación solo tiene éxito cuando cada bit de la expresión coincide con una de las alternativas, incluidos 0, 1, x y z. En el ejemplo que se muestra arriba, si alguno de los bits en sel es x o z, el default se ejecutará porque ninguna de las otras alternativas coincidió. En tal caso, la salida será todo ceros.

ncsim> run [0] a=0x4 b=0x1 c=0x1 sel=0bxx out=0x0 [10] a=0x3 b=0x5 c=0x5 sel=0bzx out=0x0 [20] a=0x5 b=0x2 c=0x1 sel=0bxx out=0x0 [30] a=0x5 b=0x6 c=0x5 sel=0bzx out=0x0 [40] a=0x5 b=0x4 c=0x1 sel=0bxz out=0x0 [50] a=0x6 b=0x5 c=0x2 sel=0bxz out=0x0 [60] a=0x5 b=0x7 c=0x2 sel=0bzx out=0x0 [70] a=0x7 b=0x2 c=0x6 sel=0bzz out=0x0 [80] a=0x0 b=0x5 c=0x4 sel=0bxx out=0x0 [90] a=0x5 b=0x5 c=0x5 sel=0bxz out=0x0 ncsim: *W,RNQUIE: Simulation is complete.

Si la declaración del caso en el diseño tiene x y z en las alternativas del elemento del caso, los resultados serían bastante diferentes.

module my_mux (input [2:0] a, b, c,

[1:0] sel,

output reg [2:0] out);

// Case items have x and z and sel has to match the exact value for

// output to be assigned with the corresponding input

always @ (a, b, c, sel) begin

case(sel)

2'bxz : out = a;

2'bzx : out = b;

2'bxx : out = c;

default : out = 0;

endcase

end

endmodule

Registro de simulación ncsim> run [0] a=0x4 b=0x1 c=0x1 sel=0bxx out=0x1 [10] a=0x3 b=0x5 c=0x5 sel=0bzx out=0x5 [20] a=0x5 b=0x2 c=0x1 sel=0bxx out=0x1 [30] a=0x5 b=0x6 c=0x5 sel=0bzx out=0x6 [40] a=0x5 b=0x4 c=0x1 sel=0bxz out=0x5 [50] a=0x6 b=0x5 c=0x2 sel=0bxz out=0x6 [60] a=0x5 b=0x7 c=0x2 sel=0bzx out=0x7 [70] a=0x7 b=0x2 c=0x6 sel=0bzz out=0x0 [80] a=0x0 b=0x5 c=0x4 sel=0bxx out=0x4 [90] a=0x5 b=0x5 c=0x5 sel=0bxz out=0x5 ncsim: *W,RNQUIE: Simulation is complete.

¿En qué se diferencia un caso de if-else?

El case declaración es diferente de if-else-if de dos maneras:

- Expresiones dadas en un

if-elsebloque son más generales mientras que en uncasebloque, una sola expresión se compara con varios elementos caseproporcionará un resultado definitivo cuando haya valores X y Z en una expresión

Verilog

- Introducción a Verilog

- Declaración de cambio de C#

- Declaración de interrupción de C#

- Declaración de continuación de C#

- Declaración de caso de cambio de C ++ con EJEMPLO

- Tutorial de Verilog

- Concatenación Verilog

- Asignaciones de Verilog

- Bloqueo y no bloqueo de Verilog

- Funciones de Verilog

- Tarea Verilog