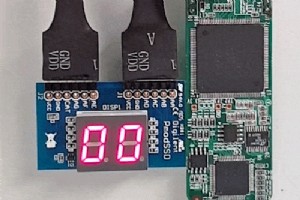

En este artículo, presentaré un módulo VHDL que puede mostrar un número de dos dígitos en el Pmod SSD:pantalla de siete segmentos de Digilent. La pantalla dual de 7 segmentos es compatible con la interfaz Pmod, lo que significa que puede usarla sin necesidad de soldadura. Encaja en el conector Pmod,

* Este artículo contiene un enlace publicitario para UpCloud VPS La entrega continua y la integración continua son metodologías ágiles de desarrollo de software que acortan el tiempo del ciclo entre el cambio de código y la implementación. Al utilizar la automatización para verificar los cambios d

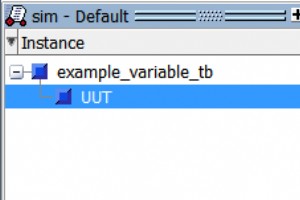

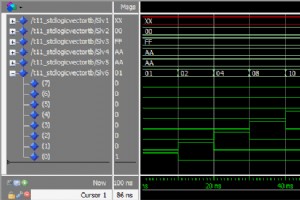

Cómo ver las variables VHDL en la forma de onda de su simulación Modelsim tiene una forma de ver las variables VHDL durante una simulación, pero no facilita la tarea. En Modelsim, los Objetos La ventana nunca muestra variables. Ventana de objetos de Modelsim, sin variables Las variables se pued

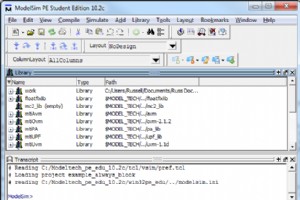

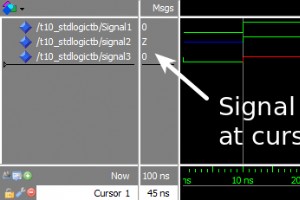

Tutorial:uso de Modelsim para simulación, para principiantes. Modelsim es un programa creado por Mentor Graphics que se utiliza para simular sus diseños VHDL y Verilog. Es el programa de simulación más utilizado en los negocios y la educación. Este tutorial explica primero por qué la simulación es

Tutorial – Introducción a VHDL VHDL es un acrónimo horrible. Significa V HSICH hardware D descripción L lenguaje. Un acrónimo dentro de un acrónimo, ¡increíble! VHSIC significa V muy H alto S orinar yo C integrada circuito. Por lo tanto, VHDL expandido es V Todo circuito integrado de alta velocidad

En resumen, VHDL es un lenguaje informático utilizado para diseñar circuitos digitales. Utilizo el término lenguaje informático para distinguir VHDL de otros lenguajes de programación más comunes como Java o C++. Pero, ¿es VHDL un lenguaje de programación? Sí, lo es. ¡Es un lenguaje de programac

Aunque las herramientas VHDL y FPGA suelen ser muy caras, es fácil acceder a software de última generación de forma gratuita si eres estudiante. Hay varios simuladores, editores e IDE para trabajar con VHDL. Este artículo le muestra cómo instalar dos de los programas más populares utilizados por los

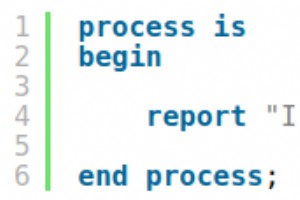

Cuando aprendo un nuevo lenguaje de programación, siempre me gusta comenzar aprendiendo a imprimir. Cuando dominas la salida de ¡Hola mundo!, sabes que tienes el entorno funcionando. También le muestra el esqueleto básico del lenguaje, el código mínimo necesario para producir cualquier resultado. P

En el tutorial anterior aprendimos que un proceso puede considerarse como un hilo de programa. También aprendimos que un wait; hace que el programa se detenga indefinidamente. Pero, ¿hay alguna manera de hacer que un programa espere por cualquier otro valor de tiempo que no sea para siempre? Si qui

En el tutorial anterior aprendimos cómo retrasar el tiempo usando el wait for declaración. También aprendimos sobre el ciclo del proceso. Ahora sabemos que si lo permitimos, el hilo del proceso se repetirá dentro del proceso para siempre. Pero, ¿y si queremos hacer algo solo una vez al principio de

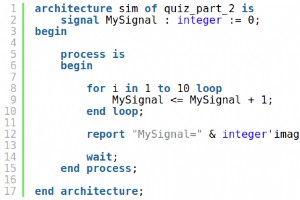

En el tutorial anterior aprendimos a crear un bucle infinito usando el loop declaración. También aprendimos cómo salir de un bucle usando el exit declaración. Pero, ¿y si queremos que el ciclo itere un cierto número de veces? For-Loop es la forma más fácil de lograr esto. For-Loop le permite iterar

En el tutorial anterior, aprendimos cómo usar un For-Loop para iterar sobre un rango de enteros. Pero, ¿qué pasa si queremos un control más detallado del ciclo que solo un rango de enteros fijo? Podemos usar un ciclo while para esto. El ciclo while continuará iterando sobre el código adjunto siempr

Así que ha completado la primera parte de la serie Tutorial básico de VHDL. ¡Felicidades! Estás a solo horas y horas y horas de convertirte en un verdadero genio de VHDL. ¡Pero ha completado el primer paso, y esa es la parte más importante en este momento! Antes de continuar, deberías poner a prueb

En el tutorial anterior aprendimos cómo declarar una variable en un proceso. Las variables son buenas para crear algoritmos dentro de un proceso, pero no son accesibles para el mundo exterior. Si el alcance de una variable está solo dentro de un solo proceso, ¿cómo puede interactuar con cualquier ot

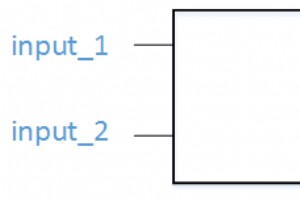

En el tutorial anterior aprendimos las principales diferencias entre señales y variables. Aprendimos que las señales tienen un alcance más amplio que las variables, a las que solo se puede acceder dentro de un proceso. Entonces, ¿cómo podemos usar señales para la comunicación entre varios procesos?

En el tutorial anterior, usamos una expresión condicional con la instrucción Esperar hasta. La expresión aseguró que el proceso solo se desencadenara cuando las dos señales de contador fueran iguales. Pero, ¿y si quisiéramos que el programa en un proceso tomara diferentes acciones en función de dife

Siempre debe usar una lista de sensibilidad para desencadenar procesos en los módulos de producción. Las listas de sensibilidad son parámetros de un proceso que enumera todas las señales a las que el proceso es sensible. Si alguna de las señales cambia, el proceso se reactivará y se ejecutará el cód

El tipo más común usado en VHDL es el std_logic . Piense en este tipo como un solo bit, la información digital transportada por un solo cable físico. El std_logic nos da un control más detallado sobre los recursos en nuestro diseño que el integer type, que hemos estado usando en los tutoriales anter

El std_logic_vector El tipo se puede utilizar para crear buses de señal en VHDL. El std_logic es el tipo más utilizado en VHDL y el std_logic_vector es la versión de matriz de la misma. Mientras que el std_logic es excelente para modelar el valor que puede transportar un solo cable, no es muy práct

¡Pon a prueba tus habilidades de codificación con este cuestionario de VHDL después de completar los tutoriales 6-11 de la serie Tutorial básico de VHDL! Si leyó las publicaciones del blog, vio los videos e hizo los ejercicios, debe estar calificado para responder la mayoría de las preguntas del cu

VHDL