Estaba un poco molesto por las peculiaridades de la interfaz AXI la primera vez que tuve que crear lógica para interconectar un módulo AXI. En lugar de las señales de control habituales ocupado/válido, completo/válido o vacío/válido, la interfaz AXI utiliza dos señales de control denominadas listo y

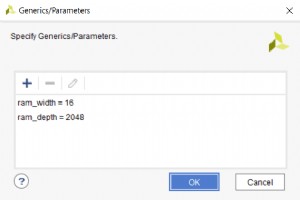

Una forma conveniente de llenar la memoria RAM de bloques con valores iniciales es leer literales binarios o hexadecimales de un archivo ASCII. Esta también es una buena manera de crear una ROM (memoria de solo lectura) en VHDL. Después de todo, la RAM y la ROM son lo mismo en las FPGA, la ROM es un

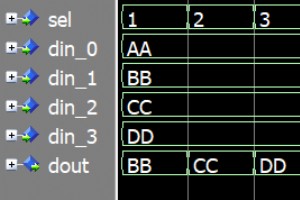

La lectura de valores de señal del archivo es una forma alternativa de generar estímulos para el dispositivo en prueba (DUT). La secuencia y el tiempo del banco de pruebas están codificados en un archivo de estímulo que lee el banco de pruebas VHDL, línea por línea. Esto le permite cambiar fácilment

Convertir el archivo de imagen a un formato de mapa de bits es la forma más fácil de leer una imagen usando VHDL. La compatibilidad con el formato de archivo de imagen de gráficos de trama BMP está integrada en el sistema operativo Microsoft Windows. Eso hace que BMP sea un formato de imagen adecuad

Este video es una presentación introductoria sobre FPGA y tecnología de lógica programable. Pronuncié esta charla de 45 minutos en un evento organizado por 7 Peaks Software en Bangkok, Tailandia, el 19 de noviembre de 2019. Los puntos destacados de la presentación incluyen: 05:07 ¿Quién usa FPGA?

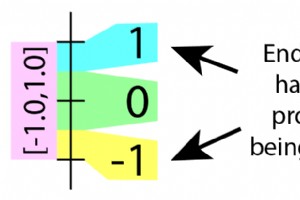

VHDL tiene un generador pseudoaleatorio incorporado, pero solo puede generar números de coma flotante entre 0 y 1. Afortunadamente, puede derivar de esto cualquier otro tipo de formato de datos aleatorios que necesite. Continúe leyendo este artículo para descubrir cómo producir real o integer valore

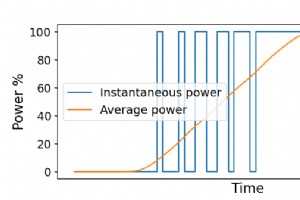

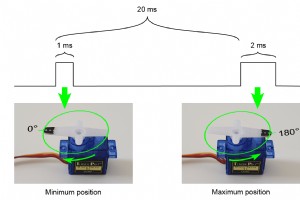

La modulación de ancho de pulso (PWM) es una forma eficiente de controlar la electrónica analógica desde pines FPGA puramente digitales. En lugar de intentar regular el voltaje analógico, PWM enciende y apaga rápidamente la corriente de suministro a plena potencia del dispositivo analógico. Este mét

Me di cuenta de que muchos de los dispositivos que compré en los últimos años han pasado del parpadeo del LED a la respiración del LED. La mayoría de los aparatos electrónicos contienen un LED de estado cuyo comportamiento brinda indicaciones de lo que sucede dentro del dispositivo. Mi cepillo de d

¿Cómo se detiene el simulador VHDL cuando se completa la simulación? Hay varias maneras de hacer eso. En este artículo, examinaremos las formas más comunes de finalizar una ejecución exitosa del banco de pruebas. El código VHDL que se presenta aquí es universal y debería funcionar en cualquier simu

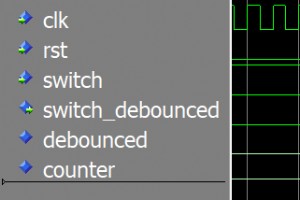

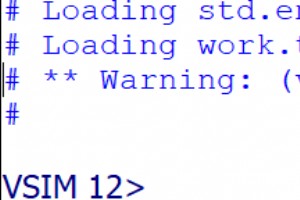

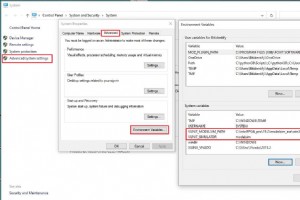

La mayoría de los simuladores VHDL utilizan el lenguaje de comandos de herramientas (Tcl) como lenguaje de secuencias de comandos. Cuando escribes un comando en la consola del simulador, estás usando Tcl. Además, puede crear scripts con Tcl que se ejecutan en el simulador e interactúan con su código

Los servos modelo controlados por radio (RC) son actuadores diminutos que se utilizan normalmente en modelos de aviones, automóviles y barcos para aficionados. Permiten al operador controlar el vehículo a través de un enlace de radio de forma remota. Debido a que los modelos RC existen desde hace mu

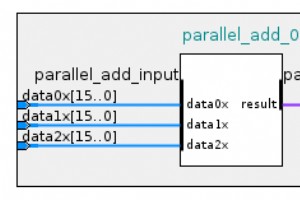

La declaración de generación en VHDL puede duplicar automáticamente un bloque de código para cierres con señales, procesos e instancias idénticas. Es un bucle for para la región de la arquitectura que puede crear procesos encadenados o instancias de módulos. A diferencia de un bucle for regular,

Las cadenas de texto en VHDL generalmente se limitan a matrices de caracteres de longitud fija. Eso tiene sentido porque VHDL describe hardware y las cadenas de longitud genérica requieren memoria dinámica. Para definir una matriz de cadenas, debe asignar espacio en tiempo de compilación para la ma

Este tutorial cubre el uso del Integrated Logic Analyzer (ILA) y Entrada/Salida Virtual (VIO) núcleos para depurar y monitorear su diseño VHDL en el IDE de Xilinx Vivado. En muchos casos, los diseñadores necesitan realizar una verificación en el chip. Es decir, obtener acceso al comportamiento de u

Al diseñar VHDL para aplicaciones FPGA críticas para la seguridad, no es suficiente escribir bancos de prueba al máximo. Debe presentar una prueba de que el módulo funciona según lo previsto y sin efectos secundarios no deseados. Las técnicas de verificación formal pueden ayudarlo a asignar un requ

VUnit es uno de los marcos de verificación de VHDL de código abierto más populares disponibles en la actualidad. Combina un ejecutor de conjunto de pruebas de Python con una biblioteca VHDL dedicada para automatizar sus bancos de pruebas. Para brindarle este tutorial gratuito de VUnit, VHDLwhiz r

¿Alguna vez ha querido ejecutar una simulación VHDL que incluya un núcleo IP de Quartus a través del marco de verificación de VUnit? Eso es lo que tenía en mente el ingeniero de FPGA Konstantinos Paraskevopoulos, pero no pudo encontrar un tutorial adecuado para ello. Afortunadamente, usó su talento

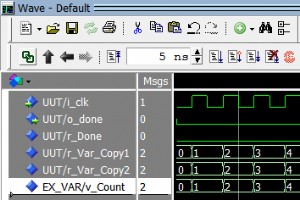

Las variables en VHDL actúan de manera similar a las variables en C. Su valor es válido en la ubicación exacta del código donde se modifica la variable. Por tanto, si una señal utiliza el valor de la variable antes la asignación, tendrá el antiguo valor de la variable. Si una señal usa el valor de l

Todos los diseñadores digitales deben comprender cómo funcionan las matemáticas dentro de un FPGA o ASIC. El primer paso para eso es comprender cómo funcionan los tipos de señales firmadas y no firmadas. Los tipos firmados y sin firmar existen en numeric_std paquete, que forma parte de la biblioteca

La construcción Record en VHDL se puede usar para simplificar su código. Los registros son similares a las estructuras en C . Los registros se utilizan con mayor frecuencia para definir un nuevo tipo de VHDL. Este nuevo tipo contiene cualquier grupo de señales que el usuario desee. La mayoría de las

VHDL

Cómo administrar un programa de monitoreo de condición de múltiples tecnologías

Thermwood mejora las capacidades de LSAM con el control automático de la temperatura de impresión

Construcción sostenible y fabricación de acero estructural

Introducción a Connext DDS, tercera parte:la herramienta esencial que TODOS los desarrolladores de DDS deben conocer