Cómo crear un proceso sincronizado en VHDL

La gran mayoría de los diseños de VHDL utilizan lógica sincronizada , también conocido como lógica síncrona o lógica secuencial . Un proceso cronometrado se activa solo por una señal de reloj maestro, no cuando cambia cualquiera de las otras señales de entrada.

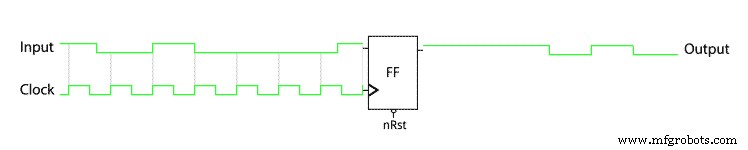

El componente básico de la lógica sincronizada es un componente llamado flip-flop . Existen diferentes variantes y en este tutorial nos vamos a centrar en el flip-flop activado por flanco positivo con reinicio negativo:

El flip-flop es un circuito de muestreo y retención, lo que significa que copia el valor de la entrada a la salida cuando llega el flanco ascendente de la señal del reloj. Luego, la salida se mantiene estable en el valor muestreado hasta el siguiente flanco ascendente del reloj, o hasta que se pulsa la señal de reinicio.

Esta publicación de blog es parte de la serie Tutoriales básicos de VHDL.

Todos los procesos cronometrados se activan simultáneamente y leerán sus entradas a la vez. Al mismo tiempo, generarán los resultados de la última iteración. La señal del reloj crea de manera efectiva pasos de tiempo en el flujo de datos. Esto hace que sea manejable para el diseñador crear una lógica compleja y profunda. Él o ella puede dividir las acciones del algoritmo en eventos que suceden en los ciclos del reloj.

Los flip-flops o conjuntos de flip-flops a veces se denominan registros , es lo mismo.

La lista de sensibilidad para procesos cronometrados generalmente contiene solo la señal del reloj. Esto se debe a que un proceso cronometrado se activa solo por un flanco en la señal del reloj, las otras señales de entrada no harán que se despierte en absoluto.

Esta es una plantilla para crear un proceso cronometrado con reinicio síncrono:process(Clk) is

begin

if rising_edge(Clk) then

if nRst = '0' then

<reset all output signals here>

else

<main logic here>

end if;

end if;

end process;

Ejercicio

En este video tutorial aprenderemos a crear un proceso cronometrado en VHDL:

El código final para flip-flop testbench :

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity T17_ClockedProcessTb is

end entity;

architecture sim of T17_ClockedProcessTb is

constant ClockFrequency : integer := 100e6; -- 100 MHz

constant ClockPeriod : time := 1000 ms / ClockFrequency;

signal Clk : std_logic := '1';

signal nRst : std_logic := '0';

signal Input : std_logic := '0';

signal Output : std_logic;

begin

-- The Device Under Test (DUT)

i_FlipFlop : entity work.T17_FlipFlop(rtl)

port map(

Clk => Clk,

nRst => nRst,

Input => Input,

Output => Output);

-- Process for generating the clock

Clk <= not Clk after ClockPeriod / 2;

-- Testbench sequence

process is

begin

-- Take the DUT out of reset

nRst <= '1';

wait for 20 ns;

Input <= '1';

wait for 22 ns;

Input <= '0';

wait for 6 ns;

Input <= '1';

wait for 20 ns;

-- Reset the DUT

nRst <= '0';

wait;

end process;

end architecture;

El código final para el módulo flip-flop :

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity T17_FlipFlop is

port(

Clk : in std_logic;

nRst : in std_logic; -- Negative reset

Input : in std_logic;

Output : out std_logic);

end entity;

architecture rtl of T17_FlipFlop is

begin

-- Flip-flop with synchronized reset

process(Clk) is

begin

if rising_edge(Clk) then

if nRst = '0' then

Output <= '0';

else

Output <= Input;

end if;

end if;

end process;

end architecture;

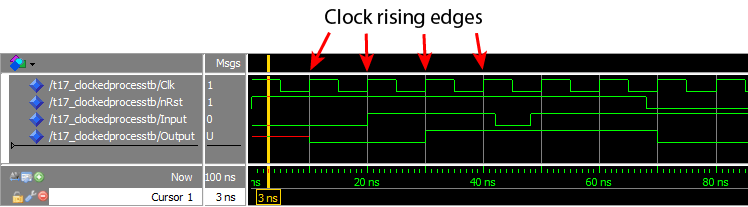

La ventana de forma de onda en ModelSim después de presionar Ejecutar y hacer zoom en la línea de tiempo:

Análisis

Podemos ver en la forma de onda que la señal de salida solo se actualiza en cada flanco ascendente de la señal del reloj. La señal de entrada se muestrea solo cuando la señal del reloj cambia de '0' a '1'. La caída negativa de la señal de entrada que comienza en aproximadamente 45 ns se pierde por completo. No se copia en la salida porque se encuentra entre dos flancos ascendentes del reloj y, por lo tanto, se ignora.

Esta animación ilustra cómo reacciona la salida a las señales cambiantes de entrada y de reloj:

Las líneas verticales indican cómo es la señal de entrada en relación con los flancos ascendentes del reloj.

Preste especial atención al pulso positivo en la señal de entrada que comienza en 20 ns. Es sincronizado con el reloj y dura exactamente un período de reloj. La salida no reacciona instantáneamente, se retrasa un período de reloj.

Cuando estaba aprendiendo VHDL, encontré esto particularmente difícil de entender. El flanco ascendente del reloj está sincronizado con el flanco ascendente de la entrada, entonces, ¿cómo puede el flip-flop elegir un valor u otro?

El simulador utiliza pasos de tiempo para modelar eventos de manera predecible y las señales se propagan en tiempo cero. Debido a que el flip-flop lee la entrada exactamente en el mismo paso de tiempo que actualiza la salida, ve el valor anterior de la entrada y lo copia en la salida.

Lea más sobre los pasos de tiempo de VHDL aquí:Explicación de los ciclos delta

Debo agregar a esta respuesta que esto no es realmente cómo funciona. En el mundo físico, una señal necesita tiempo para propagarse, no sabemos exactamente cuándo llega al flip-flop. Estos retrasos de propagación son estimados automáticamente por el proceso de software (lugar y ruta) que convierte el código VHDL en una lista de conexiones.

En realidad, la entrada debe mantenerse estable durante unos nanosegundos antes y después del flanco ascendente del reloj:

Estos períodos de tiempo críticos se conocen como tiempo de preparación y espera. Afortunadamente, esto no es algo que normalmente deba tener en cuenta. Cuando se trabaja únicamente con lógica sincronizada, estos problemas son manejados por el software que convierte el código VHDL en una lista de conexiones.

Para llevar

- Los procesos cronometrados con reinicio sincronizado solo tienen la señal del reloj en la lista de sensibilidad

- El

if rising_edge(Clk)asegura que el proceso solo se despierte en los flancos ascendentes del reloj - En un diseño síncrono, las cosas solo suceden en el borde del reloj activo

Realice el cuestionario básico de VHDL, parte 3 »

o

Pase al siguiente tutorial »

VHDL

- Cómo crear una lista de cadenas en VHDL

- Cómo crear un banco de pruebas controlado por Tcl para un módulo de bloqueo de código VHDL

- Cómo detener la simulación en un banco de pruebas VHDL

- Cómo crear un controlador PWM en VHDL

- Cómo generar números aleatorios en VHDL

- Cómo crear un FIFO de búfer de anillo en VHDL

- Cómo crear un banco de pruebas de autocomprobación

- Cómo crear una lista enlazada en VHDL

- Cómo usar un procedimiento en un proceso en VHDL

- Cómo usar una función impura en VHDL

- Cómo usar una función en VHDL