Cómo crear un controlador PWM en VHDL

La modulación de ancho de pulso (PWM) es una forma eficiente de controlar la electrónica analógica desde pines FPGA puramente digitales. En lugar de intentar regular el voltaje analógico, PWM enciende y apaga rápidamente la corriente de suministro a plena potencia del dispositivo analógico. Este método nos brinda un control preciso sobre el promedio móvil de energía proporcionada al dispositivo consumidor.

Ejemplos de casos de uso que son buenos candidatos para PWM son modulación de audio (altavoces), control de intensidad de luz (lámparas o LED) y motores de inducción. Este último incluye servomotores, ventiladores de computadora, bombas, motores de CC sin escobillas para automóviles eléctricos, y la lista continúa.

Ver también:

Controlador servo RC usando PWM desde un pin FPGA

Cómo funciona PWM

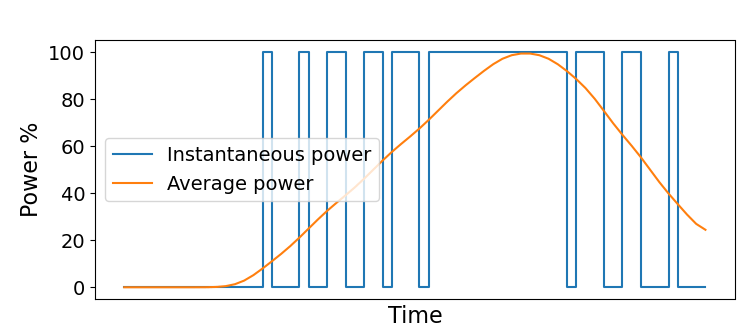

Al encender y apagar la fuente de alimentación de un dispositivo con alta frecuencia, podemos controlar con precisión la corriente promedio que fluye a través de él. La siguiente ilustración muestra los conceptos básicos de cómo funciona PWM. La salida PWM controla un interruptor binario que puede configurar la potencia al 100 % o al 0 %. Al alternar rápidamente entre los dos extremos, el promedio de la ventana deslizante será una función del tiempo pasado en cada uno de los estados.

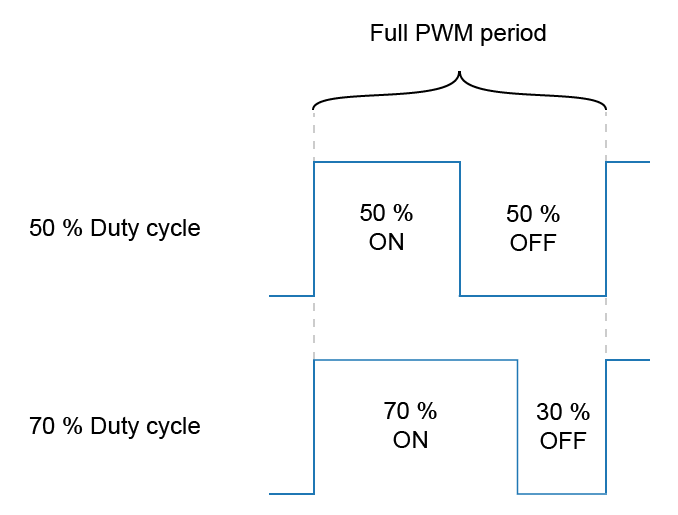

Ciclo de trabajo

El ciclo de trabajo es clave para controlar la potencia que se le da al dispositivo analógico en PWM. El término ciclo de trabajo significa cuánto tiempo pasa la salida PWM en la posición ON. Es común describir el ciclo de trabajo como un porcentaje, como se muestra en la imagen a continuación. Sin embargo, en mi ejemplo de VHDL, usaré un número binario sin firmar más adelante en este artículo. Tiene más sentido para nosotros usar un número binario, que puede representar la resolución completa del ciclo de trabajo en nuestra implementación de VHDL.

Con un ciclo de trabajo de 0, la salida PWM permanecería en la posición de APAGADO continuamente, mientras que al 100 %, no se detendría en la posición de ENCENDIDO. El grado de precisión que el controlador PWM puede ejercer sobre el efecto de la carga útil está directamente relacionado con la longitud del contador PWM. Veremos cómo funciona esto en el código VHDL cuando implementemos un controlador PWM más adelante en este artículo.

A continuación se muestra la fórmula para convertir la representación binaria del ciclo de trabajo en un porcentaje.

\mathit{trabajo\_ciclo\_porcentaje} =\frac{\mathit{ordenado\_trabajo\_ciclo} * 100}{2^\mathit{pwm\_bits} - 1}Frecuencia PWM

Cuando hablamos de la frecuencia de conmutación de PWM, nos referimos a la frecuencia con la que la salida de PWM alterna entre los estados ON y OFF, cuánto tiempo tarda el contador de PWM en ajustarse. Como siempre, la frecuencia es la inversa del período PWM completo:

\mathit{pwm\_freq} =\frac{1}{\mathit{pwm\_period}}La frecuencia PWM ideal depende del tipo de dispositivo que esté controlando. Cualquier número superior a unos pocos cientos de Hertz se verá como una fuente de luz estable a simple vista si el consumidor es un LED. Para un motor de CC sin escobillas, el punto óptimo se encuentra en el rango de las decenas de kilohercios. Ajuste la frecuencia demasiado baja y puede experimentar vibraciones físicas. Con una oscilación demasiado rápida, estás desperdiciando energía.

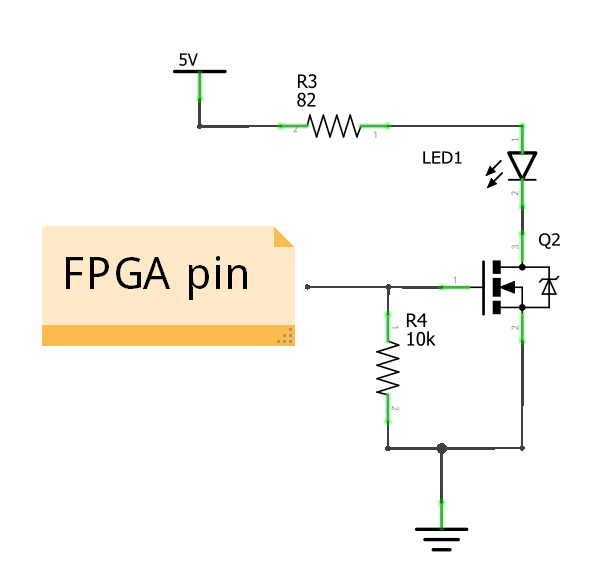

Un problema a tener en cuenta es que la electrónica de potencia analógica no es tan rápida como el pin FPGA digital. Una configuración típica de PWM utiliza MOSFET de potencia como interruptores para controlar la corriente que fluye a través del dispositivo analógico.

Considere el esquema que se muestra en la imagen. Es parte del circuito controlador de LED utilizado en mi curso avanzado Dot Matrix VHDL. El pin FPGA controla la puerta del MOSFET, actuando como un disyuntor para el LED en serie. Con una frecuencia de conmutación más alta, el transistor pasará más tiempo sin estar completamente abierto ni completamente cerrado. Eso se traduce en energía desperdiciada y exceso de producción de calor en el MOSFET.

Módulo generador PWM

Vamos a crear una implementación estándar y genérica de un controlador PWM en VHDL. A qué me refiero con estándar es que esto se acerca a lo que los diseñadores de VHDL más experimentados crearían si les pidiera que escribieran un controlador PWM en VHDL. Es genérico en el sentido de que la frecuencia PWM se puede personalizar para adaptarse a la mayoría de las aplicaciones.

Para probar nuestro generador PWM en un FPGA real, necesitaremos algunos módulos más además del controlador PWM. Los presentaré más adelante cuando use el módulo PWM para controlar la iluminación de un LED en la placa de desarrollo de FPGA Lattice iCEstick. Pero primero, hablemos del módulo generador de PWM.

Entidad del módulo PWM

Para que el módulo sea personalizable, agregué un puerto genérico que le permite especificar dos constantes en el momento de la instanciación.

El primero, llamado pwm_bits , determina la longitud del contador PWM interno. Esta constante establece la longitud de bits, no el valor máximo del contador. No podrá especificar la frecuencia PWM como un número específico de períodos de reloj. Pero, por lo general, no necesitamos configurar la frecuencia PWM con una precisión del 100 %. La frecuencia PWM ideal es un rango que funcione bien en lugar de un número exacto.

La otra constante genérica se llama clk_cnt_len . Especifica la duración de un segundo contador que reduce efectivamente la frecuencia PWM. Actúa como un divisor de reloj, pero sin crear realmente una señal de reloj derivada. Tenga en cuenta que se le asigna un valor predeterminado de 1. Establecer esta constante en 1 desactiva el divisor de reloj y también elimina la lógica adicional que lo maneja.

Explicaré esto y presentaré la fórmula para calcular la frecuencia PWM exacta más adelante en este artículo.

entity pwm is

generic (

pwm_bits : integer;

clk_cnt_len : positive := 1

);

port (

clk : in std_logic;

rst : in std_logic;

duty_cycle : in unsigned(pwm_bits - 1 downto 0);

pwm_out : out std_logic

);

end pwm;

Debido a que este es un módulo totalmente síncrono, las dos primeras señales son el reloj y el reinicio.

La tercera entrada en la lista de declaración de puerto es el ciclo de trabajo. Como puede ver en el código VHDL anterior, la duración del duty_cycle la señal sigue los pwm_bits constante genérica. Esto significa que los pwm_bits La constante determina la precisión con la que puede regular la alimentación del dispositivo analógico.

La señal final en la entidad es pwm_out . Esa es la señal de control modulada por PWM, la que enruta a un pin FPGA y conecta a la puerta de su MOSFET.

Señales internas del módulo PWM

El módulo PWM contiene solo dos señales internas. El primero es el contador PWM, que es idéntico al duty_cycle aporte. Al igual que este último, los pwm_bits constante también determina la duración de esta señal.

signal pwm_cnt : unsigned(pwm_bits - 1 downto 0); signal clk_cnt : integer range 0 to clk_cnt_len - 1;

La segunda señal interna se llama clk_cnt , y como su nombre lo indica, es para contar ciclos de reloj. Es de tipo entero, y si establece clk_cnt_len a 1, el rango de conteo se evaluará a (0 a 0) —solo el número 0.

Proceso de contador de ciclos de reloj PWM

El proceso que implementa el contador del reloj es sencillo. Si el módulo no está reiniciado, la lógica contará los ciclos de reloj continuamente, volviendo a cero en el valor máximo que clk_cnt entero puede contener.

CLK_CNT_PROC : process(clk)

begin

if rising_edge(clk) then

if rst = '1' then

clk_cnt <= 0;

else

if clk_cnt < clk_cnt_len - 1 then

clk_cnt <= clk_cnt + 1;

else

clk_cnt <= 0;

end if;

end if;

end if;

end process;

Tenga en cuenta que si utilizó el valor predeterminado de 1 para clk_cnt_len genérico, este proceso debería evaporarse durante la síntesis. La sentencia if interna siempre será falsa porque 0 < 1 - 1 Es falso. El valor de clk_cnt es entonces siempre 0. La mayoría de las herramientas de síntesis reconocerán esto y optimizarán todo el proceso.

Proceso de salida PWM

El proceso que establece la señal de salida PWM también controla el contador PWM. Incrementa el contador de PWM cuando el contador de ciclos de reloj es 0. Así es como funciona el mecanismo de limitación de frecuencia de PWM.

Inicialmente, tenía la intención de escribir solo if clk_cnt = 0 then en la línea 9, pero descubrí que la herramienta de síntesis no eliminó toda la lógica relacionada con el contador del reloj cuando usé el valor predeterminado clk_cnt_len valor de 1. Sin embargo, incluyendo clk_cnt_len en la declaración if hizo el truco. No debería tener efectos adversos en la síntesis porque clk_cnt_len es una constante La herramienta de síntesis puede determinar su valor en tiempo de compilación y luego decidir si el contenido del proceso es redundante o no.

PWM_PROC : process(clk)

begin

if rising_edge(clk) then

if rst = '1' then

pwm_cnt <= (others => '0');

pwm_out <= '0';

else

if clk_cnt_len = 1 or clk_cnt = 0 then

pwm_cnt <= pwm_cnt + 1;

pwm_out <= '0';

if pwm_cnt = unsigned(to_signed(-2, pwm_cnt'length)) then

pwm_cnt <= (others => '0');

end if;

if pwm_cnt < duty_cycle then

pwm_out <= '1';

end if;

end if;

end if;

end if;

end process;

Cuando clk_cnt_len es mayor que 1, el pwm_cnt la señal se comporta como un contador de ejecución libre, incrementándose cuando clk_cnt es 0. Es un tipo sin firmar, que volvería a 0 automáticamente cuando se desborde. Pero debemos asegurarnos de que omita el valor más alto antes de volver a cero.

En la línea 14 del código anterior, compruebo si el contador está en su segundo valor más alto. Si es así, lo establecemos en 0 en este punto. Estoy usando un truco que funcionará, sin importar cuánto tiempo dure el pwm_cnt la señal es. Mediante el uso de to_signed función, estoy creando una nueva constante firmada con la misma longitud que pwm_cnt , pero con el valor -2.

El número con signo -2 en VHDL, y en las computadoras en general, siempre será una serie de 1 y un 0 en la posición más a la derecha. Eso se debe a cómo funciona la extensión de signos. Lea más sobre eso en mi tutorial anterior:

Cómo utilizar firmado y sin firmar en VHDL

Finalmente, al convertir el tipo firmado en uno sin firmar, obtenemos el segundo valor más alto que pwm_cnt puede contener.

En la línea 18, estamos comprobando si el contador PWM de ejecución libre es mayor que la entrada del ciclo de trabajo. Si eso es cierto, configuramos la salida PWM en '1' porque estamos en el período de ENCENDIDO del ciclo de trabajo.

Es por eso que tuvimos que ajustar el contador PWM a 0 en su segundo valor más alto. Si el contador PWM pudiera alcanzar el valor más alto posible que puede tener el ciclo de trabajo, no sería posible configurar el ciclo de trabajo al 100%. El pwm_cnt < duty_cycle la línea siempre sería falsa cuando pwm_cnt estaba en su valor máximo.

Tiene sentido porque tenemos que representar los estados totalmente APAGADO y ENCENDIDO además de los pasos intermedios del ciclo de trabajo. Imagina que pwm_bits es el conjunto a 2, y recorre toda la secuencia de conteo como un ejercicio mental para ver a qué me refiero.

\mathit{pwm\_hz} =\frac{\mathit{clk\_hz}}{(2^\mathit{pwm\_bits} - 1) * \mathit{clk\_cnt\_len}}Teniendo en cuenta estos hechos, podemos derivar la fórmula que se muestra arriba para calcular la frecuencia PWM precisa. Mientras clk_hz es la frecuencia del reloj del sistema FPGA, las otras dos variables son las constantes de entrada genéricas.

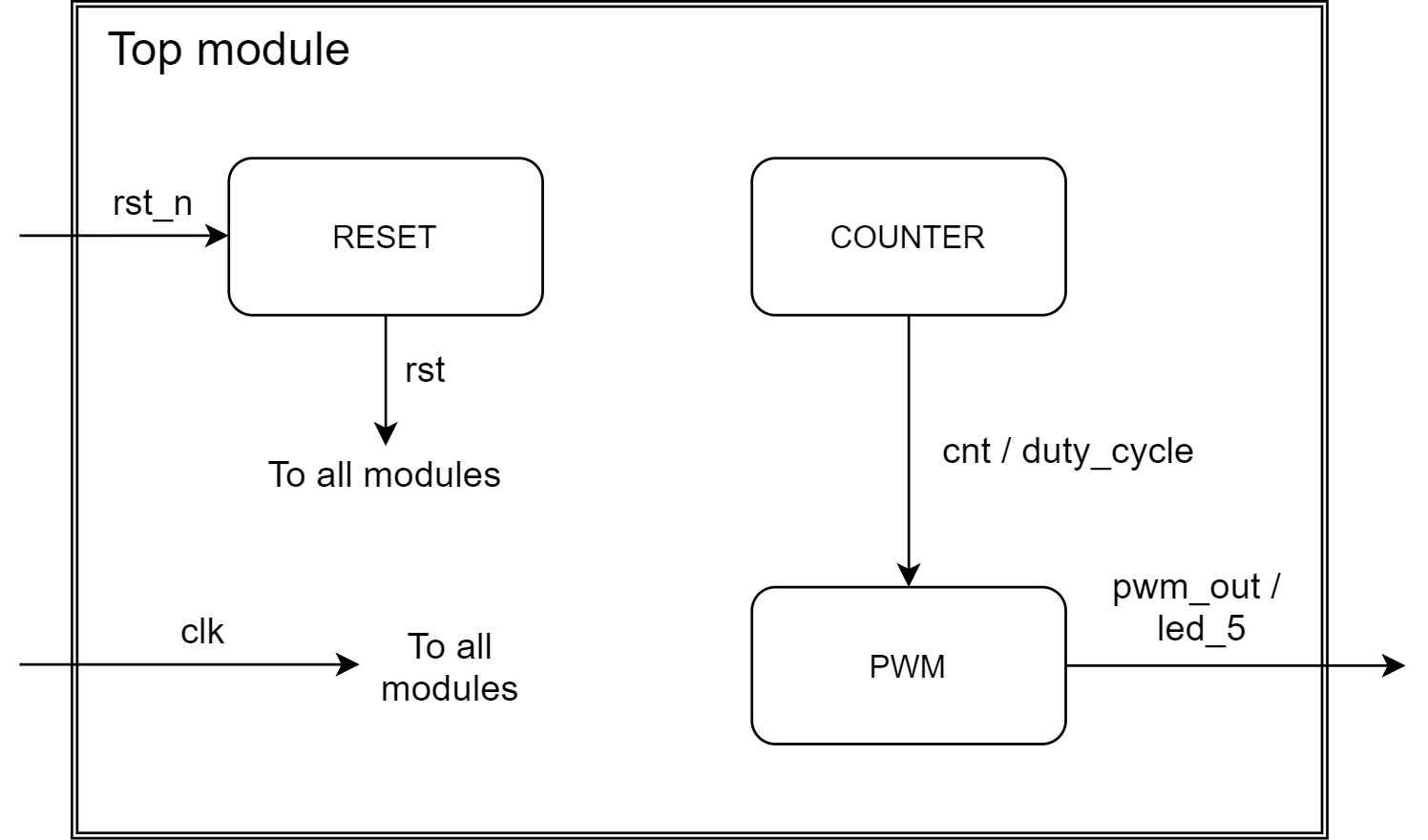

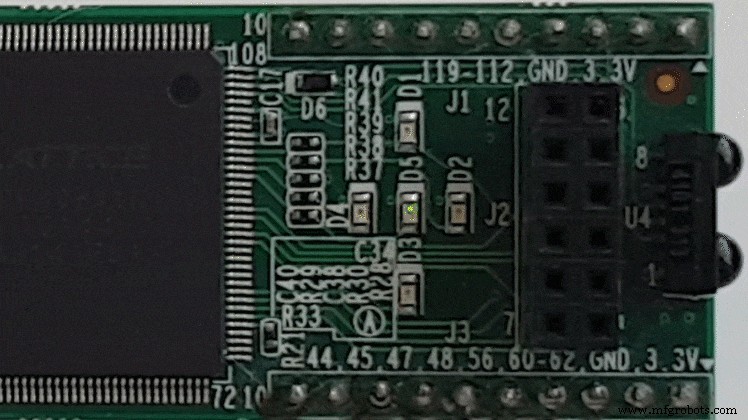

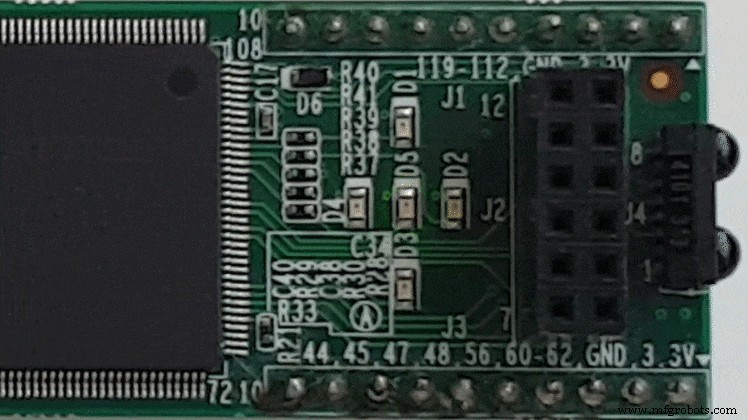

Módulo superior

Para probar el módulo PWM en hardware real, creé una implementación que regulará la iluminación del LED de encendido en Lattice iCEstick. Estoy usando esta asequible placa de desarrollo de FPGA tanto en mi curso para principiantes VHDL Fast-Track como en mi curso avanzado de FPGA de matriz de puntos.

La imagen de arriba muestra la parte frontal del iCEstick con conexión USB con el LED de encendido indicado por la flecha. Hay cinco LED en el iCEstick dispuestos en forma de estrella. El LED de encendido es verde, mientras que los demás emiten luz de color rojo. En el iCEstick, hay un pin FPGA dedicado para cada uno de los LED. Consulte el manual de usuario de iCEstick para ver los números de pin exactos para controlarlos.

El siguiente diagrama muestra cómo se conectan los submódulos en el módulo superior. Ya hemos hablado sobre el módulo PWM, y describiré brevemente los módulos de contador y reinicio más adelante en este artículo.

Entidad del módulo superior

En lugar de codificar las constantes dentro del módulo superior, las declaro como genéricas en la entidad de nivel superior. Luego, asigno valores predeterminados que son adecuados para el iCEstick. Una ventaja de este enfoque es que puede anular estos valores en el banco de pruebas para acelerar la simulación. No asigno nada a los genéricos cuando sintetizo el diseño. Por lo tanto, los valores predeterminados correctos terminarán en el diseño enrutado.

Transmitiremos pwm_bits y clk_cnt_len a los genéricos en la entidad del módulo PWM con los mismos nombres. La frecuencia de reloj del oscilador iCEstick es de 12 Mhz. Usando la fórmula presentada anteriormente, podemos conectar estos valores para calcular la frecuencia PWM:\frac{12e6}{(2^8 - 1) * 47} \approx 1 \mathit{kHz}

entity pwm_led is

generic (

pwm_bits : integer := 8;

cnt_bits : integer := 25;

clk_cnt_len : positive := 47

);

port (

clk : in std_logic;

rst_n : in std_logic; -- Pullup

led_1 : out std_logic;

led_2 : out std_logic;

led_3 : out std_logic;

led_4 : out std_logic;

led_5 : out std_logic

);

end pwm_led;

Es posible que haya notado que hay una tercera constante, cnt_bits , en la declaración de genéricos en el código anterior. Controla la longitud de un contador de dientes de sierra autoenvolvente. Vamos a usar este contador adicional para crear una iluminación gradual del LED de encendido para que podamos observar el funcionamiento del módulo PWM en tiempo real.

Conectaremos los bits altos de este nuevo contador a la entrada del ciclo de trabajo del módulo PWM. Debido a que este contador contará ciclos de reloj, los cnt_bits generic determina la frecuencia de pulsación del LED de encendido. La fórmula, que es una función de la frecuencia del reloj y la longitud del contador, se muestra a continuación.

\frac{2^{\mathit{cnt\_bits}}}{\mathit{clk\_hz}} =\frac{2^{25}}{12e6} \aprox. 2,8 \mathit{Hz}En la declaración del puerto, agregué la entrada de reinicio con _n , indicando que el reset externo tiene polaridad negativa. Configuraremos el Lattice FPGA para usar una resistencia pull-up interna en este pin.

Finalmente, puede ver que he enumerado todos los LED presentes en el iCEstick en la declaración del puerto. Solo vamos a usar el LED número 5, pero tenemos que controlar los otros LED de forma activa. Si se dejan desconectados, se iluminarán en un color rojo tenue.

Si desea ver más de cerca el código VHDL y los archivos de restricciones, ingrese su correo electrónico en el siguiente formulario. Recibirás un archivo Zip con el código completo con los proyectos ModelSim y Lattice iCEcube2.

Señales internas del módulo superior

Me gusta mantener mis módulos superiores libres de lógica RTL. Es un concepto que se llama módulo estructural . Según mi experiencia, es más fácil mantener un proyecto VHDL estructurado cuando se separa la lógica RTL y se interconecta. El siguiente código muestra las declaraciones de señales en el módulo superior y las asignaciones de señales concurrentes.

architecture str of pwm_led is signal rst : std_logic; signal cnt : unsigned(cnt_bits - 1 downto 0); signal pwm_out : std_logic; alias duty_cycle is cnt(cnt'high downto cnt'length - pwm_bits); begin led_1 <= '0'; led_2 <= '0'; led_3 <= '0'; led_4 <= '0'; led_5 <= pwm_out;

Primero, declaramos una señal de reinicio que será nuestra versión síncrona no invertida del reinicio externo.

La segunda señal declarada, denominada cnt , es el contador de ciclos de reloj infinitamente envolvente. Es un tipo sin firmar que mantendrá el estado de nuestra onda de diente de sierra de intensidad LED en cualquier momento.

El siguiente es el pwm_out señal. Podríamos haber conectado el pwm_out señal del módulo PWM directamente al led_5 salida, pero quería observar pwm_out en el simulador. La herramienta de síntesis se dará cuenta de que las dos señales pertenecen a la misma red. No costará recursos adicionales.

Finalmente llega la declaración del duty_cycle vector:esta vez, usé el alias palabra clave en lugar de crear una nueva señal. Los alias de VHDL funcionan como macros en C. Cuando usamos el duty_cycle de ahora en adelante, el compilador lo sustituirá por los bits altos del cnt vector.

Después del comienzo palabra clave, asignamos la pwm_out señal al led_5 producción. Todos los demás LED están cableados a '0' para evitar que se enciendan con luz de color rojo.

Instancias

Antes de usar señales externas dentro de la FPGA, siempre debemos sincronizarlas con el reloj interno del sistema. De lo contrario, podemos experimentar problemas de metaestabilidad, problemas que son difíciles de depurar.

RESET : entity work.reset(rtl)

port map (

clk => clk,

rst_n => rst_n,

rst => rst

);

El restablecimiento externo no es una excepción, pero debido a que no permito ninguna lógica RTL en el módulo estructural de nivel superior, implementamos el sincronizador de restablecimiento como un módulo independiente.

La siguiente instanciación es el módulo PWM, como se muestra en el fragmento de código a continuación. En la instanciación del módulo PWM, estamos usando el duty_cycle alias para asignar los bits más significativos del cnt vector al duty_cycle aporte. Eso hará que el brillo del LED se intensifique hasta que el contador alcance su valor máximo. Cuando cnt vuelve a cero, el LED se apaga brevemente y el ciclo se repite.

PWM : entity work.pwm(rtl)

generic map (

pwm_bits => pwm_bits,

clk_cnt_len => clk_cnt_len

)

port map (

clk => clk,

rst => rst,

duty_cycle => duty_cycle,

pwm_out => pwm_out

);

La tercera y última instancia en el módulo superior es el contador de ciclos de reloj, como se muestra a continuación. Para hacer que este módulo sea más genérico, he incluido un count_enable señal. Pero en este diseño, lo estableceremos en un '1' constante porque queremos contar cada ciclo de reloj.

COUNTER : entity work.counter(rtl)

generic map (

counter_bits => cnt'length

)

port map (

clk => clk,

rst => rst,

count_enable => '1',

counter => cnt

);

Deje su dirección de correo electrónico en el siguiente formulario si necesita el código VHDL completo para este proyecto.

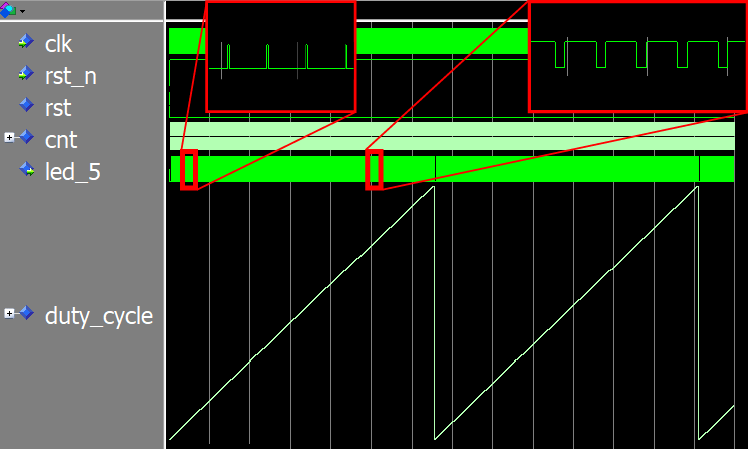

Simulación de la pulsación del LED PWM

Una ventaja significativa de hacer que las longitudes de los contadores se puedan personalizar a través de genéricos es que le permite acelerar la simulación. La mayor parte del tiempo, estamos interesados en probar las transiciones y eventos en nuestra lógica. No estamos tan interesados en correr a través de un contador ultralargo mientras no sucede nada más en el diseño.

Con los genéricos, podemos cambiar estas cosas de una forma no invasiva desde el banco de pruebas. El siguiente código muestra los valores que asigné al mapa genérico al instanciar el módulo PWM en el banco de pruebas.

DUT : entity work.pwm_led(str)

generic map (

pwm_bits => 8,

cnt_bits => 16,

clk_cnt_len => 1

)

Cuando simulamos el uso de estas constantes en ModelSim, basta con ejecutar durante 1400 microsegundos a 100 MHz para revelar dos ciclos completos de PWM. Si hubiésemos utilizado los valores reales, tendríamos que simular cerca de 6 segundos. Eso es 32 millones de ciclos de reloj de casi nada más que contar. Tomaría una eternidad en ModelSim.

La siguiente imagen muestra la forma de onda de la simulación PWM en ModelSim. He cambiado el formato del duty_cycle señal del tipo de número predeterminado a una presentación de onda analógica. Puede hacer esto en ModelSim haciendo clic derecho en la señal en la forma de onda y seleccionando Formato->Analógico (personalizado)… y configure la altura de píxel y el rango de datos para que coincidan con los valores mínimo y máximo de su señal.

En la forma de onda, podemos ver por qué se llama señal de diente de sierra. El contador envolvente de movimiento libre se asemeja a los dientes de una hoja de sierra.

Observe cómo la duración de los períodos altos de la salida PWM (led_5 ) aumenta a medida que crece el ciclo de trabajo. También podemos ver que led_5 es un '1' continuo muy brevemente en la punta del diente de sierra. Ahí es cuando el ciclo de trabajo es 255, el valor máximo.

Si no agregamos la declaración if adicional en el módulo PWM, la que envuelve el pwm_cnt señal de nuevo a cero en su segundo valor más alto, no veríamos esto. Nunca seríamos capaces de alcanzar la máxima potencia de salida. Es un error común al implementar generadores PWM. Yo también lo he hecho una o dos veces.

La implementación de FPGA

Implementé el diseño en Lattice iCEstick usando iCEcube2, el software de diseño de Lattice. La siguiente lista muestra el uso de recursos informado después del lugar y la ruta. Aunque el FPGA iCE40 es pequeño, el PWM y los módulos compatibles solo usan el 5 % de los LUT disponibles.

Resource Usage Report for pwm_led Mapping to part: ice40hx1ktq144 Cell usage: GND 3 uses SB_CARRY 31 uses SB_DFF 5 uses SB_DFFSR 39 uses SB_GB 1 use VCC 3 uses SB_LUT4 64 uses I/O ports: 7 I/O primitives: 7 SB_GB_IO 1 use SB_IO 6 uses I/O Register bits: 0 Register bits not including I/Os: 44 (3%) Total load per clock: pwm_led|clk: 1 @S |Mapping Summary: Total LUTs: 64 (5%)

Después de generar el flujo de bits de programación en iCEcube2, utilicé el programador independiente Lattice Diamond para configurar la FPGA a través de USB.

La siguiente animación Gif muestra cómo la señal del ciclo de trabajo de la onda de diente de sierra hace que se comporte el LED de encendido en el iCEstick. Se ilumina con intensidad creciente hasta el cnt envolturas de mostrador. Luego, el ciclo de trabajo se convierte en ceros y el LED se apaga brevemente. Después de eso, el ciclo se repite indefinidamente.

El iCEstick es una placa de desarrollo FPGA económica y versátil. Es bueno para principiantes, pero también es adecuado para proyectos integrados avanzados. Además, el software Lattice es sencillo y fácil de usar. Es por eso que estoy usando iCEstick tanto en mi curso de VHDL para principiantes como en el curso de FPGA avanzado.

Si ya posee un iCEstick, puede usar el siguiente formulario para descargar el proyecto iCEcube2.

Ciclo de trabajo de onda sinusoidal para efecto de respiración LED

Ahora ya sabes cómo controlar la iluminación de un LED usando PWM.

Podría decirse que el LED que pulsa en un patrón de onda de diente de sierra es más genial que una simple aplicación de parpadeo de ENCENDIDO/APAGADO. Esa es una primera tarea típica para los estudiantes de VHDL, y estoy seguro de que ha encendido un LED en algún momento.

Sin embargo, el parpadeo del LED se vuelve aún más impresionante si usa una onda sinusoidal para controlar el ciclo de trabajo. La siguiente animación Gif muestra nuestro módulo PWM pulsando el LED con una variación de intensidad sinusoidal a lo largo del tiempo.

Estoy seguro de que ha visto este tipo de efecto de "respiración" en los LED antes. Así es como se comporta el LED de notificaciones de mi teléfono móvil, y creo que se ve natural porque no hay cambios bruscos en la intensidad de la luz.

En mi próxima publicación de blog, le mostraré cómo crear un generador de onda sinusoidal utilizando RAM de bloque en FPGA. Y modificaremos el pwm_led módulo para pulsar el LED en el iCEstick con intensidad de onda sinusoidal.

Haga clic aquí para ir a la siguiente publicación del blog:

Cómo crear un efecto LED de respiración usando una onda sinusoidal almacenada en un bloque de RAM

Ver también:

Controlador servo RC usando PWM desde un pin FPGA

VHDL

- Controlador de potencia PWM

- Cómo crear una lista de cadenas en VHDL

- Cómo crear un banco de pruebas controlado por Tcl para un módulo de bloqueo de código VHDL

- Cómo detener la simulación en un banco de pruebas VHDL

- Cómo generar números aleatorios en VHDL

- Cómo crear un FIFO de búfer de anillo en VHDL

- Cómo crear un banco de pruebas de autocomprobación

- Cómo crear una lista enlazada en VHDL

- Cómo usar un procedimiento en un proceso en VHDL

- Cómo usar una función en VHDL

- ¿Cómo cargo un capacitor?