Cómo crear un vector de señal en VHDL:std_logic_vector

El std_logic_vector El tipo se puede utilizar para crear buses de señal en VHDL. El std_logic es el tipo más utilizado en VHDL y el std_logic_vector es la versión de matriz de la misma.

Mientras que el std_logic es excelente para modelar el valor que puede transportar un solo cable, no es muy práctico para implementar colecciones de cables que van hacia o desde componentes. El std_logic_vector es un tipo compuesto, lo que significa que es una colección de subelementos. Señales o variables del std_logic_vector type puede contener un número arbitrario de std_logic elementos.

Esta publicación de blog es parte de la serie Tutoriales básicos de VHDL.

La sintaxis para declarar std_logic_vector señales es:signal <name> : std_logic_vector(<lsb> to <msb>) := <initial_value>;

osignal <name> : std_logic_vector(<msb> downto <lsb>) := <initial_value>;

donde <name> es un nombre arbitrario para la señal y <initial_value> es un valor inicial opcional. El <lsb> es el índice del bit menos significativo, y <msb> es el índice del bit más significativo.

El to o downto especifica la dirección del rango del bus, básicamente su endianess. Aunque ambos funcionan igual de bien, es más común que el diseñador de VHDL declare vectores usando downto . Por tanto, te recomiendo que utilices siempre downto al declarar vectores de bits para evitar confusiones.

El código VHDL para declarar una señal vectorial que puede contener un byte:signal MySlv : std_logic_vector(7 downto 0);

El código VHDL para declarar una señal vectorial que puede contener un bit:signal MySlv : std_logic_vector(0 downto 0);

El código VHDL para declarar una señal vectorial que puede contener cero bits (un rango vacío ):signal MySlv : std_logic_vector(-1 downto 0);

Ejercicio

En este videotutorial aprenderemos a declarar std_logic_vector señales y darles valores iniciales. También aprendemos cómo iterar sobre los bits en un vector usando un For-Loop para crear un registro de desplazamiento :

El código final que creamos en este tutorial:

library ieee;

use ieee.std_logic_1164.all;

entity T11_StdLogicVectorTb is

end entity;

architecture sim of T11_StdLogicVectorTb is

signal Slv1 : std_logic_vector(7 downto 0);

signal Slv2 : std_logic_vector(7 downto 0) := (others => '0');

signal Slv3 : std_logic_vector(7 downto 0) := (others => '1');

signal Slv4 : std_logic_vector(7 downto 0) := x"AA";

signal Slv5 : std_logic_vector(0 to 7) := "10101010";

signal Slv6 : std_logic_vector(7 downto 0) := "00000001";

begin

-- Shift register

process is

begin

wait for 10 ns;

for i in Slv6'left downto Slv6'right + 1 loop

Slv6(i) <= Slv6(i-1);

end loop;

Slv6(Slv6'right) <= Slv6(Slv6'left);

end process;

end architecture;

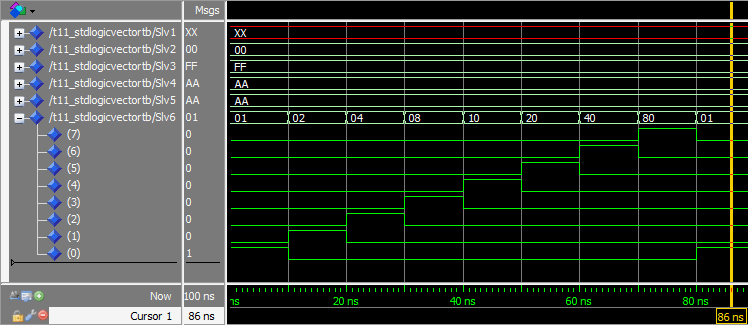

La ventana de forma de onda en ModelSim después de presionar Ejecutar y hacer zoom en la línea de tiempo:

Análisis

En este ejercicio declaramos seis std_logic_vector buses, cada uno con una longitud de ocho bits (un byte).

Señal Slv1 fue declarado sin un valor inicial. Se ve que el bus tiene el valor XX en la captura de pantalla de la forma de onda. Esto se debe a que el valor que se muestra en el bus está en hexadecimales y XX indica un valor no hexadecimal. Pero cuando expandimos el bus en la forma de onda, pudimos ver que los bits individuales eran en realidad U.

Señal Slv2 fue declarado utilizando un valor inicial de todos los 0. En lugar de especificar el valor exacto de cada bit, usamos (other => '0') en lugar del valor inicial. Esto se conoce como agregado asignación. La parte importante es que establecerá todos los bits en el vector a lo que especifique, sin importar cuánto tiempo sea.

Señal Slv3 se declaró usando una asignación agregada para dar a todos los bits el valor inicial de 1. Podemos ver FF mostrado en esta señal en la forma de onda, que es hexadecimal para ocho 1.

Señal Slv4 fue declarado con un valor inicial especificado en hexadecimal, AA. Cada dígito hexadecimal tiene una longitud de 4 bits, por lo tanto, debemos proporcionar dos dígitos (AA) para nuestro vector, que tiene una longitud de 8 bits.

Señal Slv5 declara exactamente el mismo valor inicial que Slv4 , pero ahora lo especificamos como el valor binario 10101010. Podemos ver en la forma de onda que ambas señales tienen el valor hexadecimal AA.

Señal Slv6 se declaró con un valor inicial de todos ceros, excepto el bit más a la derecha que era '1' . Utilizamos un proceso para crear un registro de desplazamiento de esta señal. El registro de desplazamiento, como su nombre lo indica, desplaza el contenido del vector un lugar hacia la izquierda cada 10 nanosegundos.

Nuestro proceso se despierta cada 10 ns, y For-Loop desplaza todos los bits del vector un lugar a la izquierda. El bit final se vuelve a desplazar al primer índice mediante el Slv6(Slv6'right) <= Slv6(Slv6'left); declaración. En la forma de onda podemos ver el '1' ondulación a través del vector.

Esta es una visualización de cómo el '1' se propaga a través de nuestro registro de desplazamiento:

Usando el 'left' y 'right atributos, hicimos nuestro código más genérico. Si cambiamos el ancho de Sig6 , el proceso seguirá funcionando. Es una buena práctica de diseño usar atributos donde sea posible en lugar de valores de codificación fija.

Quizás se pregunte si hay más atributos que puede usar, y los hay. No hablaré más sobre ellos en esta serie de tutoriales, porque los considero funciones VHDL avanzadas.

Para llevar

- Los vectores de N bits deben declararse usando

std_logic_vector(N-1 downto 0) - Se puede asignar un vector como un todo o se puede acceder a los bits dentro de él individualmente

- Todos los bits en un vector se pueden poner a cero usando la asignación agregada

(others => '0') - El código se puede hacer más genérico usando atributos como

'lefty'right

Realice el cuestionario básico de VHDL, parte 2 »

o

Pase al siguiente tutorial »

VHDL

- Ejemplos de conversiones VHDL

- Firmado vs. Sin firmar en VHDL

- Cómo crear una lista de cadenas en VHDL

- Cómo crear un banco de pruebas controlado por Tcl para un módulo de bloqueo de código VHDL

- Cómo detener la simulación en un banco de pruebas VHDL

- Cómo crear un controlador PWM en VHDL

- Cómo generar números aleatorios en VHDL

- Cómo crear un FIFO de búfer de anillo en VHDL

- Cómo crear un banco de pruebas de autocomprobación

- Cómo crear una lista enlazada en VHDL

- Cómo usar un procedimiento en un proceso en VHDL