Verilog - En pocas palabras

Todo el código de comportamiento está escrito dentro de module y endmodule . Por lo tanto, cualquiera que sea el diseño digital que pretenda crear, irá dentro de un module bloquear. Puede o no tener puertos definidos:permita que las señales ingresen al bloque como input o escapar del bloque como output .

Módulo

El módulo vacío en el siguiente ejemplo se llama testbench . Puede nombrarlo como desee, excepto que debe ser alfanumérico y puede contener '_'.

module testbench;

endmodule

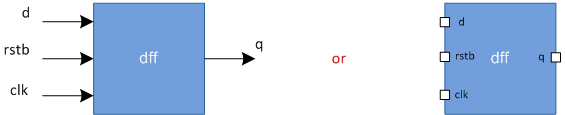

Veamos otro módulo. Tiene algunas señales (d, clk, rstb ) declaradas como entradas y q declarado como una salida.

module dff (input d,

clk,

rstb,

output q);

endmodule

Tipos de datos

Ahora que hemos visto cómo se ve un módulo, veamos qué se puede poner dentro de un módulo, mirando el módulo del banco de pruebas una vez más. Hay principalmente dos tipos de tipos de datos en verilog:

- registro

- alambre

reg tipo de datos se utiliza para retener valores como una variable, mientras que un wire es simplemente análogo a un cable eléctrico, que tiene que ser conducido continuamente. Por lo general, wire se utiliza para conectar varios módulos y otras señales.

module testbench;

reg d;

reg rst_b;

reg clk;

wire q;

endmodule

Tareas

Verilog tiene tres bloques básicos:

always @ (condición ) | siempre se ejecuta cuando se cumple la condición |

initial | se ejecutará una sola vez, cuando comience la simulación |

assign [LHS] =[RHS] | El valor de LHS se actualizará siempre que cambie RHS |

Hay algunas reglas a tener en cuenta al escribir Verilog:

regsolo se puede asignar a eninitialyalwaysbloqueswirese le puede asignar un valor solo a través deassigndeclaración- Si hay varias declaraciones en un inicial/siempre bloque, deben estar envueltos en

begin .. end

module testbench;

reg d;

reg rst_b;

reg clk;

wire q;

initial begin

d = 0;

rst_b = 0;

clk = 0;

#100 $finish;

end

always begin

#10 clk = ~clk;

end

endmodule

Nota lo siguiente del ejemplo que se muestra arriba:

- Dado que hay varias líneas para

initialbloquear, comenzar y fin se usan - Las señales d, rst_b y clk se asignan dentro de un bloque inicial, porque son del tipo

reg - El código dentro del bloque inicial se ejecutará en 0ns, es decir, al inicio de la simulación

- Dado que no hay ninguna condición para el

alwaysbloque, se ejecutará como un bucle infinito en C - # se utiliza para representar el tiempo de retardo. #10 le dice al simulador que avance el tiempo de simulación en 10 unidades.

clk = ~clk;cambiará el valor del reloj, y porque #10 se coloca antes de la declaración, el reloj se alternará después de cada 10 unidades de tiempo.$finishes la manera de terminar una simulación. En este caso, se ejecutará durante 100 unidades de tiempo y saldrá.

Verilog

- Tutorial de Verilog

- Concatenación Verilog

- Asignaciones de Verilog

- Bloqueo y no bloqueo de Verilog

- Funciones de Verilog

- Tarea Verilog

- Ámbito de referencia jerárquica de Verilog

- Generador de reloj Verilog

- Funciones matemáticas de Verilog

- Formato de hora de Verilog

- Alcance de la escala de tiempo de Verilog