Bloque inicial de Verilog

Un conjunto de declaraciones de Verilog generalmente se ejecutan secuencialmente en una simulación. Estas declaraciones se colocan dentro de un procedimiento bloquear. Existen principalmente dos tipos de procedimiento bloques en Verilog - inicial y siempre

Sintaxis

initial

[single statement]

initial begin

[multiple statements]

end

¿Para qué sirve el bloque inicial?

Un initial El bloque no es sintetizable y, por lo tanto, no se puede convertir en un esquema de hardware con elementos digitales. Por lo tanto, los bloques iniciales no sirven para mucho más que para ser utilizados en simulaciones. Estos bloques se utilizan principalmente para inicializar variables y controlar puertos de diseño con valores específicos.

¿Cuándo comienza y termina un bloque inicial?

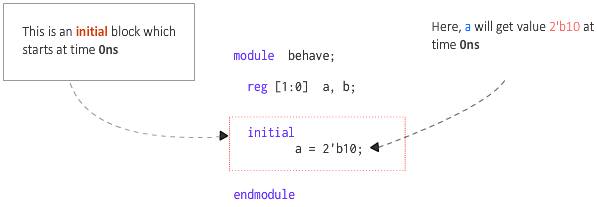

Un initial El bloque se inicia al comienzo de una simulación en la unidad de tiempo 0. Este bloque se ejecutará una sola vez durante toda la simulación. Ejecución de un initial bloque finaliza una vez que se ejecutan todas las declaraciones dentro del bloque.

La imagen que se muestra arriba tiene un module llamado comportarse que tiene dos señales internas llamadas a y b. El initial el bloque tiene solo una declaración y, por lo tanto, no es necesario colocar la declaración dentro de begin y end . Esta declaración asigna el valor 2'b10 a cuando el bloque inicial se inicia en el tiempo 0 unidades.

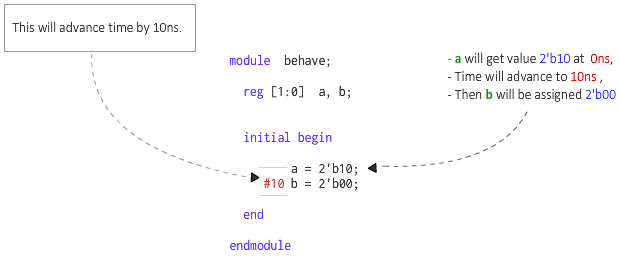

¿Qué sucede si hay un elemento de retraso?

El código que se muestra a continuación tiene una declaración adicional que asigna algún valor a la señal b. Sin embargo, esto sucede solo después de 10 unidades de tiempo desde la ejecución de la instrucción anterior. Esto significa que a a se le asigna primero el valor dado y luego, después de 10 unidades de tiempo, a b se le asigna 0.

¿Cuántos bloques iniciales se permiten en un módulo?

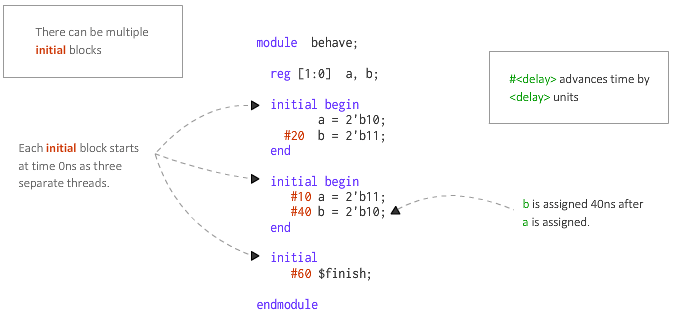

No hay límites para el número de initial bloques que se pueden definir dentro de un módulo.

El código que se muestra a continuación tiene tres initial todos los cuales se inician al mismo tiempo y se ejecutan en paralelo. Sin embargo, dependiendo de las declaraciones y los retrasos dentro de cada bloque inicial, el tiempo necesario para terminar el bloque puede variar.

En este ejemplo, el primer bloque tiene un retraso de 20 unidades, mientras que el segundo tiene un retraso total de 50 unidades (10 + 40) y el último bloque tiene un retraso de 60 unidades. Por lo tanto, la simulación tarda 60 unidades de tiempo en completarse, ya que hay al menos un bloque inicial que sigue ejecutándose hasta las 60 unidades de tiempo.

$finish es una tarea del sistema Verilog que le dice al simulador que finalice la simulación actual.

Si el último bloque tuviera un retraso de 30 unidades de tiempo como se muestra a continuación, la simulación habría terminado en 30 unidades de tiempo, matando así a todos los demás initial bloques que están activos en ese momento.

initial begin

#30 $finish;

end

Consulte el ejemplo de flash que se muestra a continuación para ver cómo un initial bloque se ejecuta en una simulación.

¡Haga clic aquí para ver una presentación de diapositivas con un ejemplo de simulación!

Verilog