contador de 4 bits

El contador de 4 bits comienza a incrementarse de 4'b0000 a 4'h1111 y luego vuelve a 4'b0000. Seguirá contando siempre que tenga un reloj en marcha y el reinicio se mantenga alto.

El rollover ocurre cuando se descarta la parte más significativa de la adición final. Cuando el contador tiene un valor máximo de 4'b1111 y recibe una solicitud de conteo más, el contador intenta llegar a 5'b10000, pero dado que solo admite 4 bits, el MSB se descartará y dará como resultado 0.

0000 0001 0010 ... 1110 1111 rolls over 0000 0001 ...

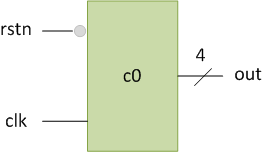

El diseño contiene dos entradas, una para el reloj y otra para un restablecimiento activo-bajo. Un restablecimiento activo bajo es aquel en el que el diseño se restablece cuando el valor del pin de restablecimiento es 0. Hay una salida de 4 bits llamada que esencialmente proporciona los valores del contador.

Diseño de contador electrónico

module counter ( input clk, // Declare input port for clock to allow counter to count up

input rstn, // Declare input port for reset to allow the counter to be reset to 0 when required

output reg[3:0] out); // Declare 4-bit output port to get the counter values

// This always block will be triggered at the rising edge of clk (0->1)

// Once inside this block, it checks if the reset is 0, if yes then change out to zero

// If reset is 1, then design should be allowed to count up, so increment counter

always @ (posedge clk) begin

if (! rstn)

out <= 0;

else

out <= out + 1;

end

endmodule

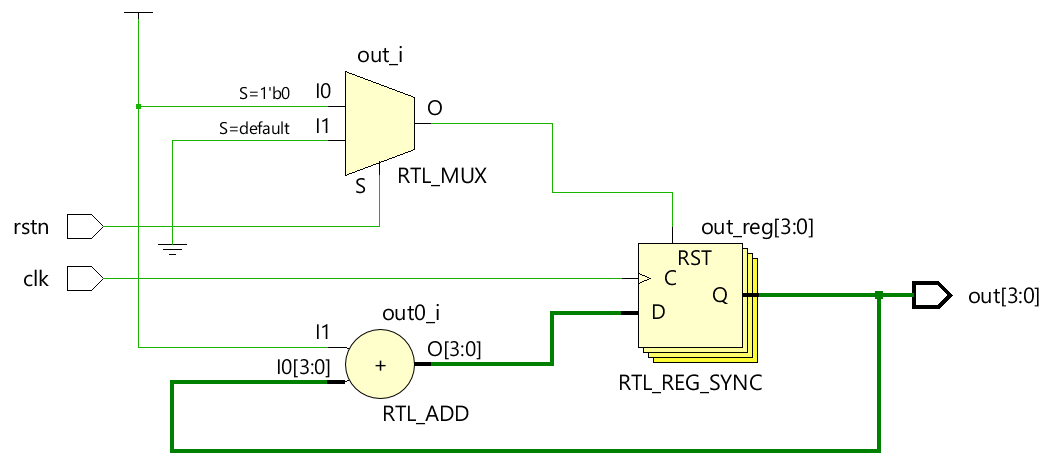

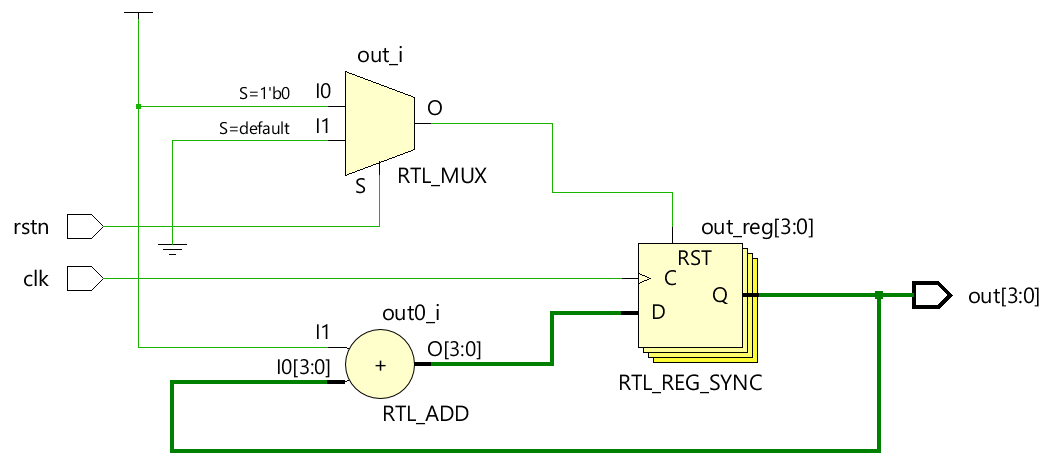

El module el contador tiene un reloj y restablecimiento activo-bajo (indicado por n ) como entradas y el valor del contador como salida de 4 bits. El always el bloque es siempre se ejecuta cada vez que el reloj pasa de 0 a 1, lo que significa un flanco ascendente o un flanco positivo. La salida se incrementa solo si el reinicio se mantiene alto o 1, logrado por el if-else bloquear. Si se encuentra que el restablecimiento es bajo en el borde positivo del reloj, la salida se restablece a un valor predeterminado de 4'b0000.

Banco de pruebas

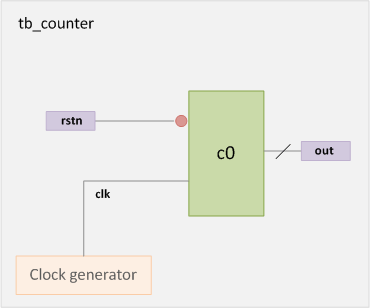

Podemos instanciar el diseño en nuestro módulo de banco de pruebas para verificar que el contador cuenta como se esperaba.

El módulo del banco de pruebas se llama tb_counter y los puertos no son necesarios ya que este es el módulo superior en la simulación. Sin embargo, necesitamos tener variables internas para generar, almacenar y controlar el reloj y reiniciar. Para ello, hemos declarado dos variables de tipo reg para reloj y reinicio. También necesitamos un wire escriba net para hacer la conexión con la salida del diseño; de lo contrario, se establecerá de forma predeterminada en una red escalar de 1 bit.

El reloj se genera a través de always bloque que dará un período de 10 unidades de tiempo. El initial El bloque se utiliza para establecer valores iniciales en nuestras variables internas y conducir el valor de reinicio al diseño. El diseño es instanciado en el banco de pruebas y conectado a nuestras variables internas, para que obtenga los valores cuando los saquemos del banco de pruebas. No tenemos ningún $display declaraciones en nuestro banco de pruebas y, por lo tanto, no veremos ningún mensaje en la consola.

module tb_counter;

reg clk; // Declare an internal TB variable called clk to drive clock to the design

reg rstn; // Declare an internal TB variable called rstn to drive active low reset to design

wire [3:0] out; // Declare a wire to connect to design output

// Instantiate counter design and connect with Testbench variables

counter c0 ( .clk (clk),

.rstn (rstn),

.out (out));

// Generate a clock that should be driven to design

// This clock will flip its value every 5ns -> time period = 10ns -> freq = 100 MHz

always #5 clk = ~clk;

// This initial block forms the stimulus of the testbench

initial begin

// 1. Initialize testbench variables to 0 at start of simulation

clk <= 0;

rstn <= 0;

// 2. Drive rest of the stimulus, reset is asserted in between

#20 rstn <= 1;

#80 rstn <= 0;

#50 rstn <= 1;

// 3. Finish the stimulus after 200ns

#20 $finish;

end

endmodule

Registro de simulación ncsim> run [0ns] clk=0 rstn=0 out=0xx [5ns] clk=1 rstn=0 out=0x0 [10ns] clk=0 rstn=0 out=0x0 [15ns] clk=1 rstn=0 out=0x0 [20ns] clk=0 rstn=1 out=0x0 [25ns] clk=1 rstn=1 out=0x1 [30ns] clk=0 rstn=1 out=0x1 [35ns] clk=1 rstn=1 out=0x2 [40ns] clk=0 rstn=1 out=0x2 [45ns] clk=1 rstn=1 out=0x3 [50ns] clk=0 rstn=1 out=0x3 [55ns] clk=1 rstn=1 out=0x4 [60ns] clk=0 rstn=1 out=0x4 [65ns] clk=1 rstn=1 out=0x5 [70ns] clk=0 rstn=1 out=0x5 [75ns] clk=1 rstn=1 out=0x6 [80ns] clk=0 rstn=1 out=0x6 [85ns] clk=1 rstn=1 out=0x7 [90ns] clk=0 rstn=1 out=0x7 [95ns] clk=1 rstn=1 out=0x8 [100ns] clk=0 rstn=0 out=0x8 [105ns] clk=1 rstn=0 out=0x0 [110ns] clk=0 rstn=0 out=0x0 [115ns] clk=1 rstn=0 out=0x0 [120ns] clk=0 rstn=0 out=0x0 [125ns] clk=1 rstn=0 out=0x0 [130ns] clk=0 rstn=0 out=0x0 [135ns] clk=1 rstn=0 out=0x0 [140ns] clk=0 rstn=0 out=0x0 [145ns] clk=1 rstn=0 out=0x0 [150ns] clk=0 rstn=1 out=0x0 [155ns] clk=1 rstn=1 out=0x1 [160ns] clk=0 rstn=1 out=0x1 [165ns] clk=1 rstn=1 out=0x2 Simulation complete via $finish(1) at time 170 NS + 0

Tenga en cuenta que el contador se restablece a 0 cuando el restablecimiento activo-bajo se convierte en 0, y cuando se desactiva el restablecimiento alrededor de los 150 ns, el contador comienza a contar desde la siguiente aparición del flanco positivo del reloj.

Esquema de hardware

Verilog

- Recargar, restablecer, reconfigurar

- Contador binario de 3 bits

- Contadores síncronos

- Módulo de contador

- Contadores de anillo

- Rampa digital ADC

- Convergencia TI / OT:una oportunidad para un restablecimiento cultural

- Contador de Python en colecciones con ejemplo

- Contador Verilog Mod-N

- Mostrador gris Verilog

- Errores de PID:Restablecer liquidación