Pestillo D

Un flip-flop captura datos en su entrada en el borde positivo o negativo de un reloj. Lo importante a tener en cuenta es que lo que suceda con los datos después del borde del reloj hasta el siguiente borde del reloj no se reflejará en la salida. Un pestillo por otro lado, no captura en el borde de un reloj, sino que la salida sigue a la entrada siempre que se afirme el pin de habilitación.

Diseño

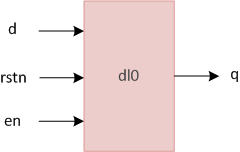

En este ejemplo, construiremos un pestillo que tiene tres entradas y una salida. La entrada d significa datos que pueden ser 0 o 1, rstn significa reinicio activo-bajo y en significa habilitar, que se utiliza para hacer que los datos de entrada se enganchen a la salida. Restablecer siendo activo-bajo simplemente significa que el elemento de diseño se restablecerá cuando esta entrada vaya a 0 o, en otras palabras, el restablecimiento está activo cuando su valor es bajo. El valor de la salida q es dictada por las entradas d , es y primero .

module d_latch ( input d, // 1-bit input pin for data

input en, // 1-bit input pin for enabling the latch

input rstn, // 1-bit input pin for active-low reset

output reg q); // 1-bit output pin for data output

// This always block is "always" triggered whenever en/rstn/d changes

// If reset is asserted then output will be zero

// Else as long as enable is high, output q follows input d

always @ (en or rstn or d)

if (!rstn)

q <= 0;

else

if (en)

q <= d;

endmodule

Tenga en cuenta que la lista de sensibilidad al always El bloque contiene todas las señales necesarias para actualizar la salida. Este bloque se activará cada vez que alguna de las señales en la lista de sensibilidad cambie su valor. También q obtendrá el valor de d solo cuando en es alto, y por lo tanto es un positivo pestillo.

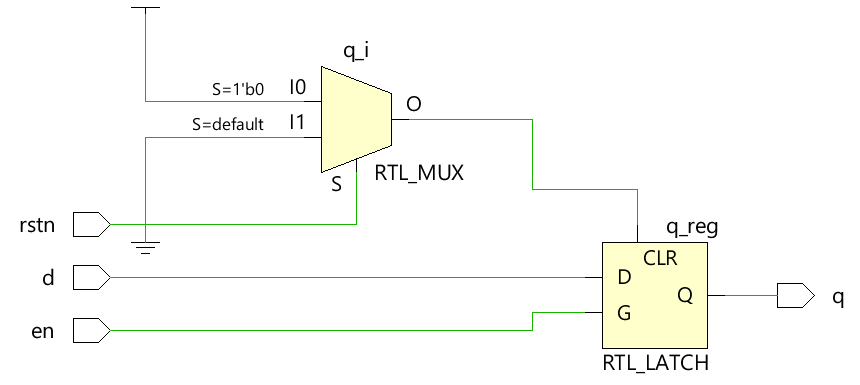

Esquema

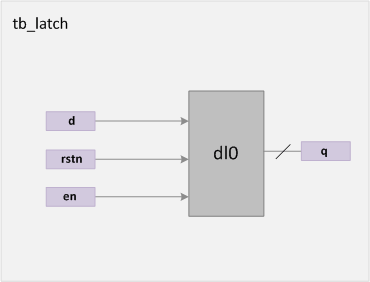

Banco de pruebas

module tb_latch;

// Declare variables that can be used to drive values to the design

reg d;

reg en;

reg rstn;

reg [2:0] delay;

reg [1:0] delay2;

integer i;

// Instantiate design and connect design ports with TB signals

d_latch dl0 ( .d (d),

.en (en),

.rstn (rstn),

.q (q));

// This initial block forms the stimulus to test the design

initial begin

$monitor ("[%0t] en=%0b d=%0b q=%0b", $time, en, d, q);

// 1. Initialize testbench variables

d <= 0;

en <= 0;

rstn <= 0;

// 2. Release reset

#10 rstn <= 1;

// 3. Randomly change d and enable

for (i = 0; i < 5; i=i+1) begin

delay = $random;

delay2 = $random;

#(delay2) en <= ~en;

#(delay) d <= i;

end

end

endmodule

Para hacer que nuestro banco de pruebas confirme y rechace las señales de una manera más aleatoria, hemos declarado un reg variable llamada retraso de tamaño 3 bits para que pueda tomar cualquier valor de 0 a 7. Entonces el retraso variable se utiliza para retrasar la asignación de d y es para obtener diferentes patrones en cada ciclo.

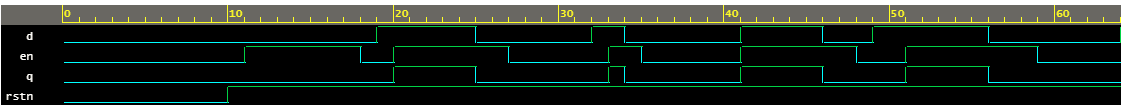

Salida

Registro de simulaciónncsim> run [0] en=0 d=0 q=0 [11] en=1 d=0 q=0 [18] en=0 d=0 q=0 [19] en=0 d=1 q=0 [20] en=1 d=1 q=1 [25] en=1 d=0 q=0 [27] en=0 d=0 q=0 [32] en=0 d=1 q=0 [33] en=1 d=1 q=1 [34] en=1 d=0 q=0 ncsim: *W,RNQUIE: Simulation is complete.

Haga clic en la imagen para agrandarla.

Verilog

- Amplificador de emisor común

- Amplificador operacional simple

- Seguidor de voltaje de precisión

- Amplificador no inversor

- Entrada y salida básica de C#

- Entrada/salida básica de C++

- C Entrada Salida (E/S)

- Entrada, salida e importación de Python

- Entrada y salida básica de Java

- Entrada/salida básica de C++:ejemplo de Cout, Cin, Cerr

- C - Entrada y Salida