Primitivas definidas por el usuario de Verilog

Primitivos estándar de Verilog como nand y not puede no ser siempre fácil o suficiente para representar una lógica compleja. Nuevos elementos primitivos llamados UDP o primitivas definidas por el usuario se puede definir para modelar lógica combinacional o secuencial.

Todos los UDP tienen exactamente una salida que puede ser 0, 1 o X y nunca Z (no compatible). Cualquier entrada que tenga el valor Z será tratada como X.

Símbolos UDP de Verilog

Las primitivas definidas por el usuario de Verilog se pueden escribir en el mismo nivel que módulo definiciones, pero nunca entre module y endmodule . Pueden tener muchos puertos de entrada pero siempre un puerto de salida, y los puertos bidireccionales no son válidos. Todas las señales de los puertos deben ser escalares, lo que significa que deben tener un ancho de 1 bit.

El comportamiento del hardware se describe como primitivo tabla de estado que enumera diferentes combinaciones posibles de entradas y su salida correspondiente dentro de table y endtable . Los valores de las señales de entrada y salida se indican mediante los siguientes símbolos.

| Símbolo | Comentarios |

|---|---|

| 0 | Lógica 0 |

| 1 | Lógica 1 |

| x | Desconocido, puede ser 0 ó 1 lógico. Puede usarse como entrada/salida o estado actual de UDP secuenciales |

| ? | Lógica 0, 1 o x. No puede ser salida de ningún UDP |

| - | Sin cambios, solo permitido en la salida de un UDP |

| ab | Cambio en el valor de a a b donde a o b es 0, 1 o x |

| * | Igual que ??, indica cualquier cambio en el valor de entrada |

| r | Igual que 01 -> flanco ascendente en la entrada |

| f | Igual que 10 -> flanco descendente en la entrada |

| p | Posible flanco positivo en la entrada; 0->1, 0->x o x->1 |

| n | Posible flanco descendente en la entrada; ya sea 1->0, x->0, 1->x |

Ejemplo de UDP combinado

// Output should always be the first signal in port list

primitive mux (out, sel, a, b);

output out;

input sel, a, b;

table

// sel a b out

0 1 ? : 1;

0 0 ? : 0;

1 ? 0 : 0;

1 ? 1 : 1;

x 0 0 : 0;

x 1 1 : 1;

endtable

endprimitive

Un ? indica que la señal puede ser 0, 1 o x y no importa a la hora de decidir la salida final.

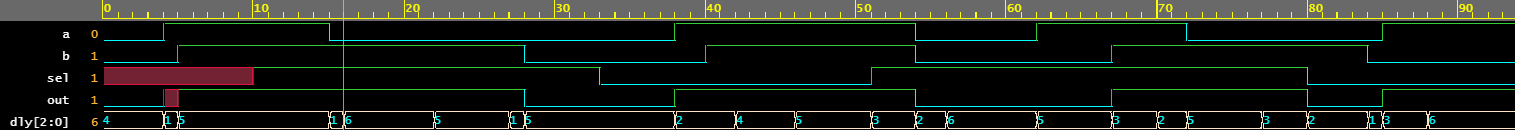

A continuación se muestra un módulo de banco de pruebas que instancia el UDP y le aplica estímulos de entrada.

module tb;

reg sel, a, b;

reg [2:0] dly;

wire out;

integer i;

// Instantiate the UDP - note that UDPs cannot

// be instantiated with port name connection

mux u_mux ( out, sel, a, b);

initial begin

a <= 0;

b <= 0;

$monitor("[T=%0t] a=%0b b=%0b sel=%0b out=%0b", $time, a, b, sel, out);

// Drive a, b, and sel after different random delays

for (i = 0; i < 10; i = i + 1) begin

dly = $random;

#(dly) a <= $random;

dly = $random;

#(dly) b <= $random;

dly = $random;

#(dly) sel <= $random;

end

end

endmodule

Registro de simulación

Registro de simulación xcelium> run [T=0] a=0 b=0 sel=x out=0 [T=4] a=1 b=0 sel=x out=x [T=5] a=1 b=1 sel=x out=1 [T=10] a=1 b=1 sel=1 out=1 [T=15] a=0 b=1 sel=1 out=1 [T=28] a=0 b=0 sel=1 out=0 [T=33] a=0 b=0 sel=0 out=0 [T=38] a=1 b=0 sel=0 out=1 [T=40] a=1 b=1 sel=0 out=1 [T=51] a=1 b=1 sel=1 out=1 [T=54] a=0 b=0 sel=1 out=0 [T=62] a=1 b=0 sel=1 out=0 [T=67] a=1 b=1 sel=1 out=1 [T=72] a=0 b=1 sel=1 out=1 [T=80] a=0 b=1 sel=0 out=0 [T=84] a=0 b=0 sel=0 out=0 [T=85] a=1 b=0 sel=0 out=1 xmsim: *W,RNQUIE: Simulation is complete.

Ejemplo de UDP secuencial

La lógica secuencial puede ser sensible al nivel o sensible al borde y, por lo tanto, hay dos tipos de UDP secuenciales. El puerto de salida también debe declararse como reg escriba dentro de la definición UDP y se puede inicializar opcionalmente dentro de un initial declaración.

Los UDP secuenciales tienen un campo adicional entre el campo de entrada y salida que está delimitado por un : que representa el estado actual.

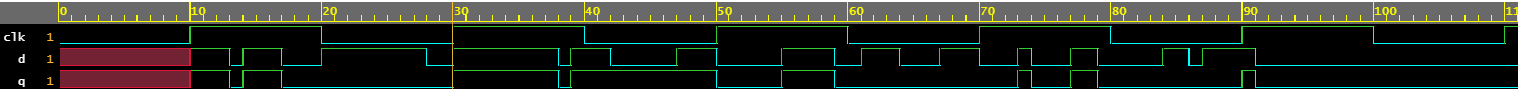

UDP sensibles al nivel

primitive d_latch (q, clk, d);

output q;

input clk, d;

reg q;

table

// clk d q q+

1 1 : ? : 1;

1 0 : ? : 0;

0 ? : ? : -;

endtable

endprimitive

En la tabla anterior, un guión - en la última fila de la tabla indica que no hay cambio en el valor de q+.

module tb;

reg clk, d;

reg [1:0] dly;

wire q;

integer i;

d_latch u_latch (q, clk, d);

always #10 clk = ~clk;

initial begin

clk = 0;

$monitor ("[T=%0t] clk=%0b d=%0b q=%0b", $time, clk, d, q);

#10; // To see the effect of X

for (i = 0; i < 50; i = i+1) begin

dly = $random;

#(dly) d <= $random;

end

#20 $finish;

end

endmodule

Registro de simulación

Registro de simulación xcelium> run [T=0] clk=0 d=x q=x [T=10] clk=1 d=1 q=1 [T=13] clk=1 d=0 q=0 [T=14] clk=1 d=1 q=1 [T=17] clk=1 d=0 q=0 [T=20] clk=0 d=1 q=0 [T=28] clk=0 d=0 q=0 [T=30] clk=1 d=1 q=1 [T=38] clk=1 d=0 q=0 [T=39] clk=1 d=1 q=1 [T=40] clk=0 d=1 q=1 [T=42] clk=0 d=0 q=1 [T=47] clk=0 d=1 q=1 [T=50] clk=1 d=0 q=0 [T=55] clk=1 d=1 q=1 [T=59] clk=1 d=0 q=0 [T=60] clk=0 d=0 q=0 [T=61] clk=0 d=1 q=0 [T=64] clk=0 d=0 q=0 [T=67] clk=0 d=1 q=0 [T=70] clk=1 d=0 q=0 [T=73] clk=1 d=1 q=1 [T=74] clk=1 d=0 q=0 [T=77] clk=1 d=1 q=1 [T=79] clk=1 d=0 q=0 [T=80] clk=0 d=0 q=0 [T=84] clk=0 d=1 q=0 [T=86] clk=0 d=0 q=0 [T=87] clk=0 d=1 q=0 [T=90] clk=1 d=1 q=1 [T=91] clk=1 d=0 q=0 [T=100] clk=0 d=0 q=0 [T=110] clk=1 d=0 q=0 Simulation complete via $finish(1) at time 111 NS + 0

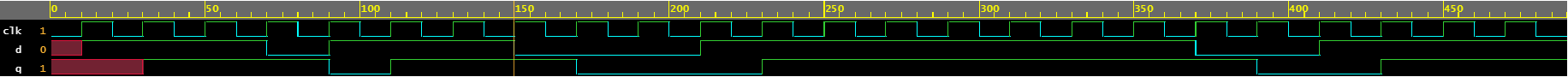

UDP sensibles al borde

Un flip-flop D se modela como una primitiva definida por el usuario de Verilog en el ejemplo que se muestra a continuación. Tenga en cuenta que el flanco ascendente del reloj se especifica mediante 01 o 0?

primitive d_flop (q, clk, d);

output q;

input clk, d;

reg q;

table

// clk d q q+

// obtain output on rising edge of clk

(01) 0 : ? : 0;

(01) 1 : ? : 1;

(0?) 1 : 1 : 1;

(0?) 0 : 0 : 0;

// ignore negative edge of clk

(?0) ? : ? : -;

// ignore data changes on steady clk

? (??): ? : -;

endtable

endprimitive

En el banco de pruebas, el UDP se instancia y se controla con valores de entrada d aleatorios después de un número aleatorio de relojes.

module tb;

reg clk, d;

reg [1:0] dly;

wire q;

integer i;

d_flop u_flop (q, clk, d);

always #10 clk = ~clk;

initial begin

clk = 0;

$monitor ("[T=%0t] clk=%0b d=%0b q=%0b", $time, clk, d, q);

#10; // To see the effect of X

for (i = 0; i < 20; i = i+1) begin

dly = $random;

repeat(dly) @(posedge clk);

d <= $random;

end

#20 $finish;

end

endmodule

En la imagen se puede ver que la salida q sigue a la entrada d después de 1 retraso de reloj, que es el comportamiento deseado para un flip-flop D.

Registro de simulación

Registro de simulación xcelium> run [T=0] clk=0 d=x q=x [T=10] clk=1 d=1 q=x [T=20] clk=0 d=1 q=x [T=30] clk=1 d=1 q=1 [T=40] clk=0 d=1 q=1 [T=50] clk=1 d=1 q=1 [T=60] clk=0 d=1 q=1 [T=70] clk=1 d=0 q=1 [T=80] clk=0 d=0 q=1 [T=90] clk=1 d=1 q=0 [T=100] clk=0 d=1 q=0 [T=110] clk=1 d=1 q=1 [T=120] clk=0 d=1 q=1 [T=130] clk=1 d=1 q=1 [T=140] clk=0 d=1 q=1 [T=150] clk=1 d=0 q=1 [T=160] clk=0 d=0 q=1 [T=170] clk=1 d=0 q=0 [T=180] clk=0 d=0 q=0 [T=190] clk=1 d=0 q=0 [T=200] clk=0 d=0 q=0 [T=210] clk=1 d=1 q=0 [T=220] clk=0 d=1 q=0 [T=230] clk=1 d=1 q=1 [T=240] clk=0 d=1 q=1 [T=250] clk=1 d=1 q=1 [T=260] clk=0 d=1 q=1 [T=270] clk=1 d=1 q=1 [T=280] clk=0 d=1 q=1 [T=290] clk=1 d=1 q=1 [T=300] clk=0 d=1 q=1 [T=310] clk=1 d=1 q=1 [T=320] clk=0 d=1 q=1 [T=330] clk=1 d=1 q=1 [T=340] clk=0 d=1 q=1 [T=350] clk=1 d=1 q=1 [T=360] clk=0 d=1 q=1 [T=370] clk=1 d=0 q=1 [T=380] clk=0 d=0 q=1 [T=390] clk=1 d=0 q=0 [T=400] clk=0 d=0 q=0 [T=410] clk=1 d=1 q=0 [T=420] clk=0 d=1 q=0 [T=430] clk=1 d=1 q=1 [T=440] clk=0 d=1 q=1 [T=450] clk=1 d=1 q=1 [T=460] clk=0 d=1 q=1 [T=470] clk=1 d=1 q=1 [T=480] clk=0 d=1 q=1 Simulation complete via $finish(1) at time 490 NS + 0

Verilog

- Tutorial de Verilog

- Concatenación Verilog

- Asignaciones de Verilog

- Bloqueo y no bloqueo de Verilog

- Funciones de Verilog

- Tarea Verilog

- Generador de reloj Verilog

- Funciones matemáticas de Verilog

- Formato de hora de Verilog

- Alcance de la escala de tiempo de Verilog

- Operaciones de E/S de archivos de Verilog