Puertos Verilog

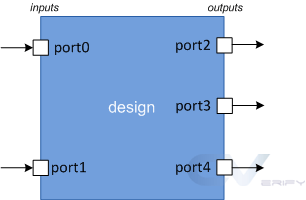

Los puertos son un conjunto de señales que actúan como entradas y salidas de un módulo en particular y son la forma principal de comunicarse con él. Piense en un módulo como un chip fabricado colocado en una PCB y se vuelve bastante obvio que la única forma de comunicarse con el chip es a través de sus pines. Los puertos son como pines y el diseño los utiliza para enviar y recibir señales del mundo exterior.

Tipos de Puertos

| Puerto | Descripción |

|---|---|

| Entrada | El módulo de diseño solo puede recibir valores del exterior usando su input puertos |

| Salida | El módulo de diseño solo puede enviar valores al exterior usando su output puertos |

| Entrada | El módulo de diseño puede enviar o recibir valores usando su inout puertos |

Los puertos se consideran por defecto como redes de tipo wire .

Sintaxis

Puertos declarados como inout puede actuar como entrada y salida.

input [net_type] [range] list_of_names; // Input port

inout [net_type] [range] list_of_names; // Input & Output port

output [net_type] [range] list_of_names; // Output port driven by a wire

output [var_type] [range] list_of_names; // Output port driven by a variable

Ejemplo

En el código que se muestra a continuación, hay tres input puertos, uno output puerto y uno inout puerto.

module my_design ( input wire clk,

input en,

input rw,

inout [15:0] data,

output int );

// Design behavior as Verilog code

endmodule

Es ilegal usar el mismo nombre para múltiples puertos.

input aport; // First declaration - valid

input aport; // Error - already declared

output aport; // Error - already declared

Puertos firmados

El signed El atributo se puede adjuntar a una declaración de puerto o una declaración de red/reg o ambas. Las redes implícitas están por defecto sin firmar .

module ( input a,

b,

output c);

// ports a, b, and c are by default unsigned

endmodule

Si la declaración net/reg tiene un signed atributo, entonces el otro también se considerará firmado.

module ( input signed a, b,

output c);

wire a, b; // a, b are signed from port declaration

reg signed c; // c is signed from reg declaration

endmodule

Variaciones de puerto

Verilog 1995

Verilog ha sido objeto de algunas revisiones y la versión original de IEEE en 1995 tenía la siguiente forma de declaración de puerto. Aquí, la declaración del módulo tenía que enumerar primero los nombres de los puertos entre corchetes y luego la dirección de esos puertos definidos más adelante dentro del cuerpo del módulo.

module test (a, b, c);

input [7:0] a; // inputs "a" and "b" are wires

input [7:0] b;

output [7:0] c; // output "c" by default is a wire

// Still, you can declare them again as wires to avoid confusion

wire [7:0] a;

wire [7:0] b;

wire [7:0] c;

endmodule

module test (a, b, c);

input [7:0] a, b;

output [7:0] c; // By default c is of type wire

// port "c" is changed to a reg type

reg [7:0] c;

endmodule

Verilog 2001 en adelante

La nomenclatura de puertos de estilo ANSI-C se introdujo en 2001 y permitió especificar el tipo dentro de la lista de puertos.

module test ( input [7:0] a,

b, // "b" is considered an 8-bit input

output [7:0] c);

// Design content

endmodule

module test ( input wire [7:0] a,

input wire [7:0] b,

output reg [7:0] c);

// Design content

endmodule

Si una declaración de puerto incluye un tipo de red o variable, se considera que ese puerto está completamente declarado. Es ilegal volver a declarar el mismo puerto en una declaración de tipo neto o variable.

module test ( input [7:0] a, // a, e are implicitly declared of type wire

output reg [7:0] e );

wire signed [7:0] a; // illegal - declaration of a is already complete -> simulator dependent

wire [7:0] e; // illegal - declaration of e is already complete

// Rest of the design code

endmodule

Si la declaración del puerto no incluye un tipo de red o variable, entonces el puerto se puede declarar en una declaración de tipo de red o variable nuevamente.

module test ( input [7:0] a,

output [7:0] e);

reg [7:0] e; // Okay - net_type was not declared before

// Rest of the design code

endmodule

Verilog

- Tutorial de Verilog

- Concatenación Verilog

- Asignaciones de Verilog

- Bloqueo y no bloqueo de Verilog

- Funciones de Verilog

- Tarea Verilog

- Generador de reloj Verilog

- Funciones matemáticas de Verilog

- Formato de hora de Verilog

- Alcance de la escala de tiempo de Verilog

- Operaciones de E/S de archivos de Verilog