Todo el código de comportamiento está escrito dentro de module y endmodule . Por lo tanto, cualquiera que sea el diseño digital que pretenda crear, irá dentro de un module bloquear. Puede o no tener puertos definidos:permita que las señales ingresen al bloque como input o escapar del bloque como out

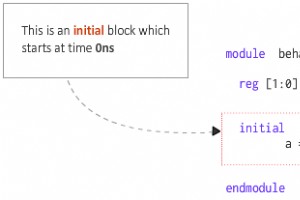

Un conjunto de declaraciones de Verilog generalmente se ejecutan secuencialmente en una simulación. Estas declaraciones se colocan dentro de un procedimiento bloquear. Existen principalmente dos tipos de procedimiento bloques en Verilog - inicial y siempre Sintaxis initial [single statemen

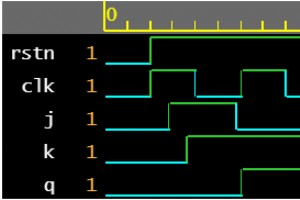

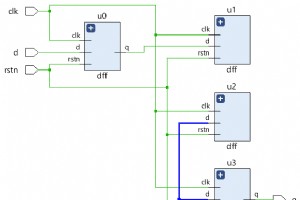

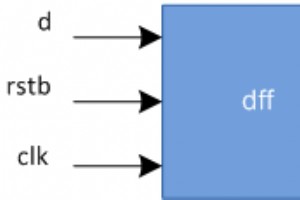

Un artículo anterior mostró diferentes ejemplos del uso de un always bloque para implementar la lógica combinacional. Un always bloque también se utiliza principalmente para implementar secuencial lógica que tiene elementos de memoria como flip flops que pueden contener valores. Chanclas JK Un flip

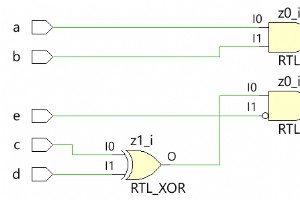

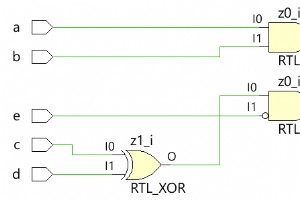

El bloque verilog always puede usarse tanto para lógica secuencial como combinacional. Se mostraron algunos ejemplos de diseño usando un assign declaración en un artículo anterior. El mismo conjunto de diseños se explorará a continuación usando un always bloquear. Ejemplo #1:lógica combinacional sim

Un always bloque es uno de los procedimiento bloques en Verilog. Las declaraciones dentro de un bloque siempre se ejecutan secuencialmente. Sintaxis always @ (event) [statement] always @ (event) begin [multiple statements] end El always bloque se ejecuta en algún evento en particular. E

Los cables Verilog de varios bits y las variables se pueden agrupar para formar un cable o variable multired más grande mediante concatenación operadores { y } separado por comas. También se permite la concatenación para tener expresiones y constantes de tamaño como operandos además de cables y vari

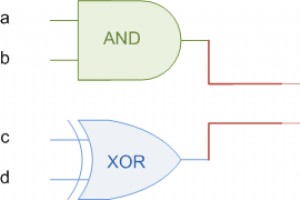

Los datos que no se pueden procesar son bastante inútiles, siempre se requerirá alguna forma de cálculo en los circuitos digitales y los sistemas informáticos. Veamos algunos de los operadores en Verilog que permitirían que las herramientas de síntesis realicen elementos de hardware apropiados. Oper

La declaración de asignación de verilog generalmente se usa para impulsar continuamente una señal de wire tipo de datos y se sintetiza como lógica combinacional. Aquí hay algunos ejemplos de diseño más usando el assign declaración. Ejemplo #1:lógica combinacional simple El código que se muestra a c

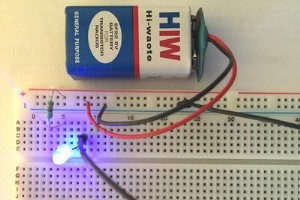

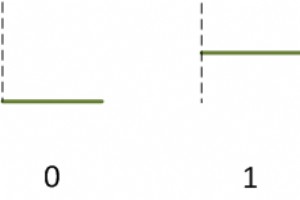

Señales de tipo wire o un tipo de datos similar a un cable requiere la asignación continua de un valor. Por ejemplo, considere un cable eléctrico que se usa para conectar piezas en una placa de pruebas. Mientras la batería de +5 V se aplique a un extremo del cable, el componente conectado al otro ex

Como vimos en un artículo anterior, los diseños más grandes y complejos se construyen integrando múltiples módulos de manera jerárquica. Los módulos pueden ser instanciados dentro de otros módulos y puertos de estas instancias se puede conectar con otras señales dentro del módulo principal. Estas c

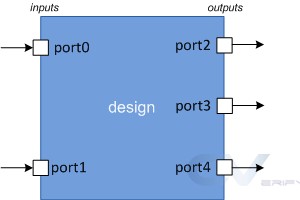

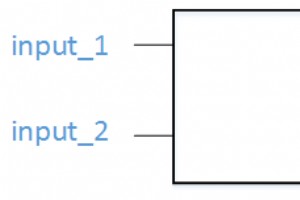

Los puertos son un conjunto de señales que actúan como entradas y salidas de un módulo en particular y son la forma principal de comunicarse con él. Piense en un módulo como un chip fabricado colocado en una PCB y se vuelve bastante obvio que la única forma de comunicarse con el chip es a través de

Un module es un bloque de código Verilog que implementa una cierta funcionalidad. Los módulos pueden integrarse dentro de otros módulos y un módulo de nivel superior puede comunicarse con sus módulos de nivel inferior utilizando sus puertos de entrada y salida. Sintaxis Un módulo debe estar encerra

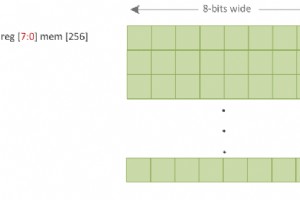

Una matriz la declaración de una red o variable puede ser escalar o vectorial. Se puede crear cualquier cantidad de dimensiones especificando un rango de direcciones después del nombre del identificador y se denomina matriz multidimensional. Las matrices están permitidas en Verilog para reg , wire ,

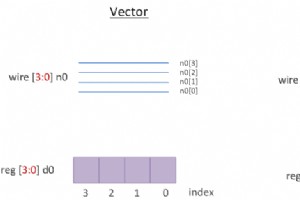

Verilog necesita representar bits individuales así como grupos de bits. Por ejemplo, un elemento secuencial de un solo bit es un flip-flop. Sin embargo, un elemento secuencial de 16 bits es un registro que puede contener 16 bits. Para este propósito, Verilog tiene scalar y vectores redes y variables

La intención principal de los tipos de datos en el lenguaje Verilog es representar elementos de almacenamiento de datos como bits en un flip-flop y elementos de transmisión como cables que se conectan entre puertas lógicas y estructuras secuenciales. ¿Qué valores tienen las variables? Casi todos l

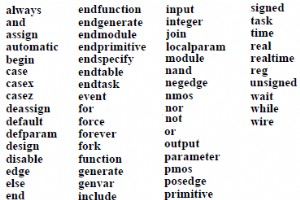

Las convenciones léxicas en Verilog son similares a las de C en el sentido de que contiene un flujo de tokens. Un token léxico puede constar de uno o más caracteres y los tokens pueden ser comentarios, palabras clave, números, cadenas o espacios en blanco. Todas las líneas deben terminar con un punt

Antes de ver más detalles del lenguaje Verilog, sería bueno comprender las diferentes capas de abstracción en el diseño de chips. La capa superior es la arquitectura a nivel del sistema que define los diversos subbloques y los agrupa en función de la funcionalidad. Por ejemplo, un clúster de proces

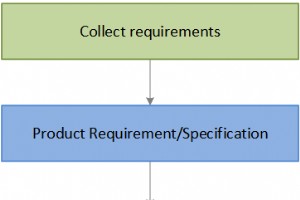

Un flujo de diseño típico sigue una estructura que se muestra a continuación y se puede dividir en varios pasos. Algunas de estas fases ocurren en paralelo y otras secuencialmente. Echaremos un vistazo a cómo se ve un ciclo de diseño de proyecto típico en la industria actual. Requisitos Un client

En los primeros días de los circuitos integrados, los ingenieros tenían que sentarse y dibujar físicamente los transistores y sus conexiones en papel para diseñarlos de manera que pudieran fabricarse en silicio. Los circuitos más grandes y complejos exigieron más ingenieros, tiempo y otros recursos

Verilog es un tipo de lenguaje de descripción de hardware (HDL). Verilog es uno de los dos lenguajes utilizados por la educación y las empresas para diseñar FPGA y ASIC. Si no está familiarizado con el funcionamiento de los FPGA y ASIC, debe leer esta página para obtener una introducción a los FPGA

Verilog