Las funciones matemáticas de Verilog se pueden usar en lugar de expresiones constantes y admiten tanto integer y real matemáticas. Funciones matemáticas enteras La función $clog2 devuelve el techo de log2 del argumento dado. Esto se usa típicamente para calcular el ancho mínimo requerido para dire

Las tareas del sistema de visualización se utilizan principalmente para mostrar mensajes informativos y de depuración para rastrear el flujo de simulación de los archivos de registro y también ayudan a depurar más rápido. Existen diferentes grupos de tareas de visualización y formatos en los que se

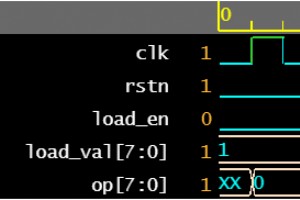

Los relojes son fundamentales para construir circuitos digitales, ya que permiten sincronizar diferentes bloques entre sí. Propiedades de un reloj Las propiedades clave de un reloj digital son su frecuencia que determina el período de reloj , su ciclo de trabajo y la fase del reloj en relación con

El diseño y el banco de pruebas de Verilog suelen tener muchas líneas de código que comprenden always o initial bloques, asignaciones continuas y otras declaraciones de procedimiento que se activan en diferentes momentos en el curso de una simulación. Cada cambio en el valor de una señal en el mode

La simulación de Verilog depende de cómo se defina el tiempo porque el simulador necesita saber qué significa #1 en términos de tiempo. El `timescale La directiva del compilador especifica la unidad de tiempo y la precisión de los módulos que la siguen. Sintaxis `timescale <time_unit>/<

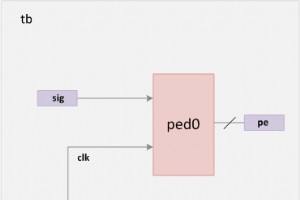

Verilog es un lenguaje de descripción de hardware y no es necesario que los diseñadores simulen sus diseños RTL para poder convertirlos en puertas lógicas. Entonces, ¿cuál es la necesidad de simular? La simulación es una técnica de aplicar diferentes estímulos de entrada al diseño en diferentes m

Primitivos estándar de Verilog como nand y not puede no ser siempre fácil o suficiente para representar una lógica compleja. Nuevos elementos primitivos llamados UDP o primitivas definidas por el usuario se puede definir para modelar lógica combinacional o secuencial. Todos los UDP tienen exactamen

Verilog también brinda soporte para el modelado a nivel de transistores, aunque los diseñadores rara vez lo usan en la actualidad, ya que la complejidad de los circuitos les ha obligado a moverse a niveles más altos de abstracción en lugar de usar el modelado a nivel de interruptor. NMOS/PMOS m

Los elementos digitales son entidades binarias y solo pueden contener cualquiera de los dos valores:0 y 1. Sin embargo, la transición de 0 a 1 y de 1 a 0 tiene un retraso de transición, al igual que cada elemento de puerta para propagar el valor desde la entrada hasta su salida. Por ejemplo, una p

Algunas de las principales primitivas incorporadas se discutieron en el artículo anterior y sería bueno ver algunos ejemplos prácticos del uso de and simple , nor y not puertas. Tenga en cuenta que para escribir el código Verilog usando puertas, es necesario que sepa cómo conectar los elementos. Es

La mayoría de los diseños digitales se realizan en un nivel más alto de abstracción como RTL, aunque a veces se vuelve intuitivo construir circuitos deterministas más pequeños en un nivel más bajo mediante el uso de elementos combinacionales como y y o . El modelado realizado en este nivel generalme

La mayoría de los lenguajes de programación tienen un rasgo característico llamado alcance que define la visibilidad de ciertas secciones de código para variables y métodos. El ámbito define un espacio de nombres para evitar la colisión entre diferentes nombres de objetos dentro del mismo espacio de

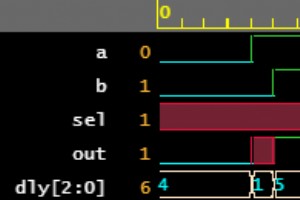

Las declaraciones de retraso de Verilog pueden tener retrasos especificados en el lado izquierdo o en el lado derecho del operador de asignación. Retrasos entre tareas // Delay is specified on the left side #<delay> <LHS> = <RHS> Una inter-tarea declaración de retraso tiene

Hay dos tipos de controles de tiempo en Verilog:delay y evento expresiones El retraso El control es solo una forma de agregar un retraso entre el momento en que el simulador encuentra la declaración y cuando realmente la ejecuta. La expresión de evento permite retrasar la declaración hasta que ocurr

Verilog admite algunas directivas del compilador que esencialmente le indican al compilador que trate el código de cierta manera. Por ejemplo, una parte del código puede representar una implementación de una función determinada y debe haber alguna forma de no incluir el código en el diseño si la fun

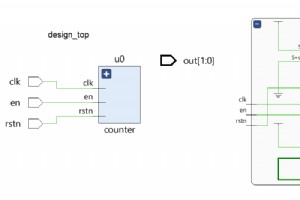

Los parámetros son construcciones de Verilog que permiten reutilizar un módulo con una especificación diferente. Por ejemplo, se puede parametrizar un sumador de 4 bits para aceptar un valor para el número de bits y se pueden pasar nuevos valores de parámetros durante la instanciación del módulo. En

Un function está destinado a realizar algún procesamiento en la entrada y devolver un valor único, mientras que un task es más general y puede calcular múltiples valores de resultados y devolverlos usando salida y dentro-fuera argumentos de tipo. Las tareas pueden contener elementos que requieren mu

A menudo, encontramos que ciertos fragmentos de código son repetitivos y se llaman varias veces dentro del RTL. En su mayoría, no consumen tiempo de simulación y pueden implicar cálculos complejos que deben realizarse con diferentes valores de datos. En tales casos, podemos declarar un function y co

El case La instrucción comprueba si la expresión dada coincide con una de las otras expresiones de la lista y se bifurca en consecuencia. Normalmente se utiliza para implementar un multiplexor. La construcción if-else puede no ser adecuada si hay muchas condiciones que verificar y se sintetizaría en

Un for loop es el loop más utilizado en el software, pero se usa principalmente para replicar lógica de hardware en Verilog. La idea detrás de un for loop es iterar un conjunto de declaraciones dadas dentro del ciclo siempre que la condición dada sea verdadera. Esto es muy similar al while loop, per

Verilog