Restablecimiento asíncrono de flip-flop D

Una chancleta D es un elemento secuencial que sigue al pin de entrada d en el borde dado de un reloj.

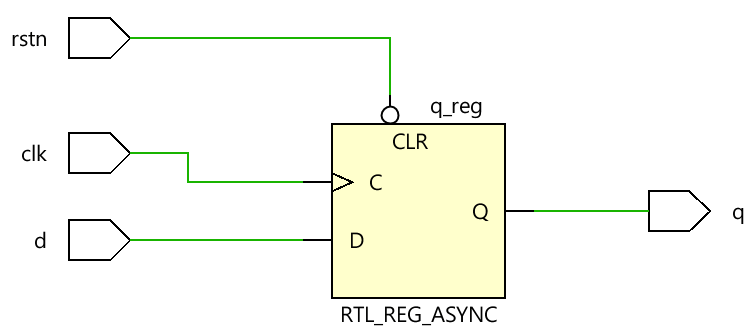

Diseño n.º 1:con reinicio asíncrono activo-bajo

module dff ( input d,

input rstn,

input clk,

output reg q);

always @ (posedge clk or negedge rstn)

if (!rstn)

q <= 0;

else

q <= d;

endmodule

Esquema de hardware

Banco de pruebas

module tb_dff;

reg clk;

reg d;

reg rstn;

reg [2:0] delay;

dff dff0 ( .d(d),

.rsnt (rstn),

.clk (clk),

.q (q));

// Generate clock

always #10 clk = ~clk;

// Testcase

initial begin

clk <= 0;

d <= 0;

rstn <= 0;

#15 d <= 1;

#10 rstn <= 1;

for (int i = 0; i < 5; i=i+1) begin

delay = $random;

#(delay) d <= i;

end

end

endmodule

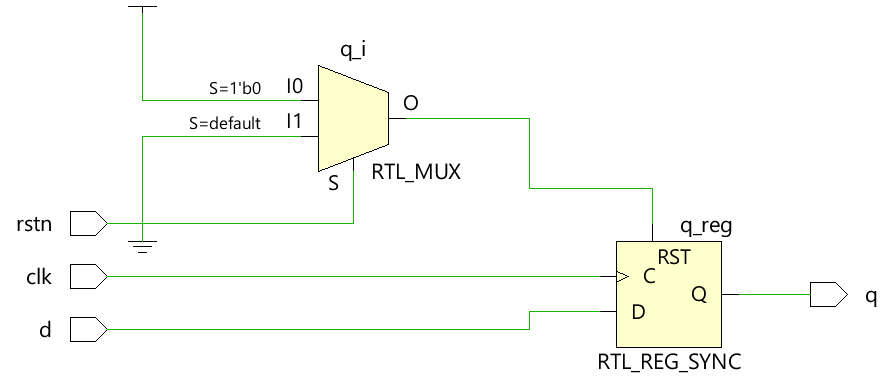

Diseño n.º 1:con sincronización activa-reinicio bajo

module dff ( input d,

input rstn,

input clk,

output reg q);

always @ (posedge clk)

if (!rstn)

q <= 0;

else

q <= d;

endmodule

Esquema de hardware

Banco de pruebas

module tb_dff;

reg clk;

reg d;

reg rstn;

reg [2:0] delay;

dff dff0 ( .d(d),

.rsnt (rstn),

.clk (clk),

.q (q));

// Generate clock

always #10 clk = ~clk;

// Testcase

initial begin

clk <= 0;

d <= 0;

rstn <= 0;

#15 d <= 1;

#10 rstn <= 1;

for (int i = 0; i < 5; i=i+1) begin

delay = $random;

#(delay) d <= i;

end

end

endmodule

Verilog

- Introducción a Verilog

- Recargar, restablecer, reconfigurar

- Flip-Flop S-R de puerta NAND

- Convergencia TI / OT:una oportunidad para un restablecimiento cultural

- Tutorial de Verilog

- contador de 4 bits

- Contador Verilog Mod-N

- Mostrador gris Verilog

- Errores de PID:Restablecer liquidación

- 74LS74:Una guía completa del flip-flop dual

- ¿Qué es el botón RESET en el panel del operador CNC