Tipos de datos de Verilog

La intención principal de los tipos de datos en el lenguaje Verilog es representar elementos de almacenamiento de datos como bits en un flip-flop y elementos de transmisión como cables que se conectan entre puertas lógicas y estructuras secuenciales.

¿Qué valores tienen las variables?

Casi todos los tipos de datos solo pueden tener uno de los cuatro valores diferentes que se indican a continuación, excepto real y event tipos de datos.

| 0 | representa un cero lógico o una condición falsa |

| 1 | representa uno lógico o una condición verdadera |

| x | representa un valor lógico desconocido (puede ser cero o uno) |

| z | representa un estado de alta impedancia |

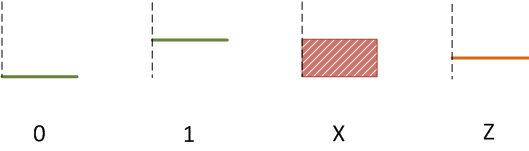

La siguiente imagen muestra cómo se representan estos valores en diagramas de tiempo y formas de onda de simulación. La mayoría de los simuladores usan esta convención donde rojo significa X y naranja en el medio significa alta impedancia o Z .

¿Qué implica el conjunto de valores de verilog?

Dado que Verilog se usa esencialmente para describir elementos de hardware como flip-flops y lógica combinacional como NAND y NOR, tiene que modelar el sistema de valores que se encuentra en el hardware. Un uno lógico representaría la tensión de alimentación Vdd que puede oscilar entre 0,8 V y más de 3 V según el nodo de tecnología de fabricación. Un cero lógico representaría tierra y por lo tanto un valor de 0V.

X o x significa que el valor es simplemente desconocido en ese momento, y podría ser 0 o 1. Esto es bastante diferente de la forma en que X se trata en lógica booleana, donde significa "no me importa".

Como con cualquier circuito eléctrico incompleto, el cable que no está conectado a nada tendrá una alta impedancia en ese nodo y está representado por Z o z . Incluso en verilog, cualquier cable desconectado generará una alta impedancia.

Redes y Variables

Redes y variables son los dos grupos principales de tipos de datos que representan diferentes estructuras de hardware y difieren en la forma en que se asignan y retienen valores.

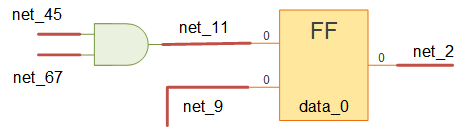

Redes

Redes se utilizan para conectarse entre entidades de hardware como puertas lógicas y, por lo tanto, no almacenan ningún valor por sí mismas. En la imagen que se muestra a continuación, se usa una red llamada net_11 para conectar entre la salida de la compuerta AND y la primera entrada del flip-flop llamada data_0. De manera similar, las dos entradas de la puerta AND están conectadas a las redes net_45 y net_67.

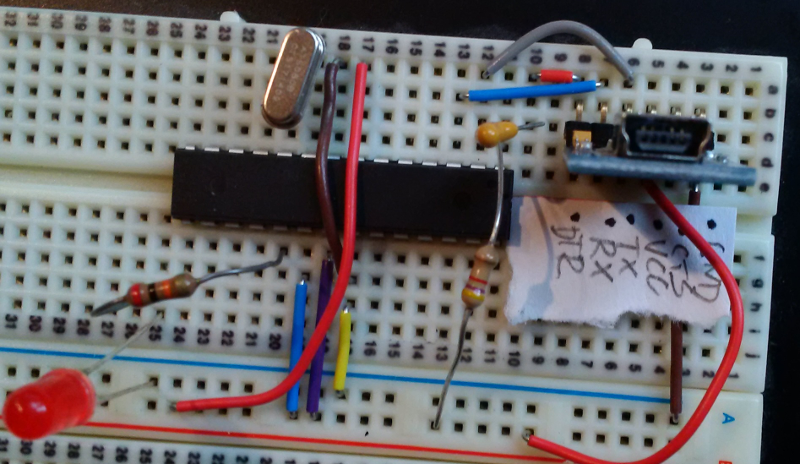

Existen diferentes tipos de redes, cada una con diferentes características, pero la red más popular y ampliamente utilizada en diseños digitales es de tipo wire . Un wire es un tipo de datos de Verilog que se utiliza para conectar elementos y redes que son impulsadas por una sola puerta o asignación continua. El wire es similar al cable eléctrico que se usa para conectar dos componentes en una placa de pruebas.

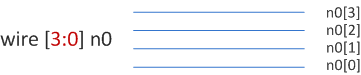

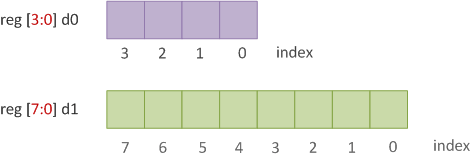

Cuando hay un requisito para varias redes, se pueden agrupar para formar un único wire . En la imagen que se muestra a continuación, tenemos un cable de 4 bits que puede enviar 4 valores separados en cada uno de los cables. Tales entidades con un ancho superior a 1 se denominan vectores, como veremos en el próximo artículo.

wire [3:0] n0; // 4-bit wire -> this is a vector

Es ilegal volver a declarar un nombre ya declarado por una red, parámetro o variable como se muestra en el código a continuación.

module design;

wire abc;

wire a;

wire b;

wire c;

wire abc; // Error: Identifier "abc" previously declared

assign abc = a & b | c;

endmodule

Variables

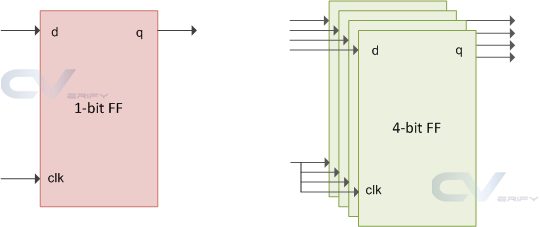

Una variable, por otro lado, es una abstracción de un elemento de almacenamiento de datos y puede contener valores. Un flip-flop es un buen ejemplo de un elemento de almacenamiento.

Tipo de datos de Verilog reg se puede usar para modelar registros de hardware ya que puede contener valores entre asignaciones. Tenga en cuenta que un reg no siempre tiene que representar un flip-flop porque también se puede usar para representar la lógica combinacional.

En la imagen que se muestra a la izquierda, tenemos un flip-flop que puede almacenar 1 bit y el flip-flop de la derecha puede almacenar 4 bits.

Otros tipos de datos

entero

Un integer es una variable de uso general de 32 bits de ancho que se puede utilizar para otros fines al modelar hardware y almacenar valores enteros.

integer count; // Count is an integer value > 0

tiempo

Un time La variable no tiene signo, tiene 64 bits de ancho y se puede usar para almacenar cantidades de tiempo de simulación con fines de depuración. Un realtime La variable simplemente almacena el tiempo como una cantidad de punto flotante.

time end_time; // end_time can be stored a time value like 50ns

realtime rtime; // rtime = 40.25ps

real

Un real variable puede almacenar valores de punto flotante y se puede asignar de la misma manera que integer y reg .

real float; // float = 12.344 - can store floating numbers

Ejemplo

module testbench;

integer int_a; // Integer variable

real real_b; // Real variable

time time_c; // Time variable

initial begin

int_a = 32'hcafe_1234; // Assign an integer value

real_b = 0.1234567; // Assign a floating point value

#20; // Advance simulation time by 20 units

time_c = $time; // Assign current simulation time

// Now print all variables using $display system task

$display ("int_a = 0x%0h", int_a);

$display ("real_b = %0.5f", real_b);

$display ("time_c = %0t", time_c);

end

endmodule

Registro de simulación ncsim> run int_a = 0xcafe1234 real_b = 0.12346 time_c = 20 ncsim: *W,RNQUIE: Simulation is complete.

Cadenas Verilog

Las cadenas se almacenan en reg , y el ancho del reg La variable tiene que ser lo suficientemente grande para contener la cadena. Cada carácter de una cadena representa un valor ASCII y requiere 1 byte. Si el tamaño de la variable es más pequeño que la cadena, Verilog trunca los bits más a la izquierda de la cadena. Si el tamaño de la variable es mayor que la cadena, Verilog agrega ceros a la izquierda de la cadena.

// "Hello World" requires 11 bytes

reg [8*11:1] str = "Hello World"; // Variable can store 11 bytes, str = "Hello World"

reg [8*5:1] str = "Hello World"; // Variable stores only 5 bytes (rest is truncated), str = "World"

reg [8*20:1] str = "Hello World"; // Variable can store 20 bytes (rest is padded with zeros), str = " Hello World"

Aquí hay un ejemplo completo que muestra cómo se pueden simular las tres variables dadas anteriormente.

module testbench;

reg [8*11:1] str1;

reg [8*5:1] str2;

reg [8*20:1] str3;

initial begin

str1 = "Hello World";

str2 = "Hello World";

str3 = "Hello World";

$display ("str1 = %s", str1);

$display ("str2 = %s", str2);

$display ("str3 = %s", str3);

end

endmodule

Tenga en cuenta que str1 tiene el tamaño correcto para almacenar los 11 bytes de la cadena "Hello World" y, por lo tanto, se imprime toda la cadena. Sin embargo, str2 puede almacenar solo 5 bytes y, por lo tanto, los 6 bytes superiores se truncan y terminan almacenando solo "Mundo". La tercera variable str3 tiene más de 11 bytes y rellena los espacios vacíos a la izquierda y, por lo tanto, el valor almacenado en ella se convierte en "Hola mundo".

Registro de simulaciónncsim> run str1 = Hello World str2 = World str3 = Hello World ncsim: *W,RNQUIE: Simulation is complete.

Verilog

- Variables de C# y tipos de datos (primitivos)

- Tipos de datos de C++

- Tipos de datos C

- Tipos de datos de Python

- Tipos de datos Java (primitivos)

- 5 tipos diferentes de centros de datos [con ejemplos]

- 8 tipos diferentes de computación en la nube en 2021

- 8 tipos diferentes de violaciones de datos con ejemplos

- Tutorial de Verilog

- Concatenación Verilog

- C - Tipos de datos