Declaraciones de bloques de Verilog

Hay formas de agrupar un conjunto de declaraciones que son sintácticamente equivalentes a una sola declaración y se conocen como declaraciones en bloque. . Hay dos tipos de sentencias de bloque:secuenciales y paralelas.

Secuencial

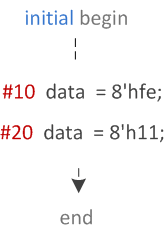

Las declaraciones se envuelven usando begin y end palabras clave y se ejecutarán secuencialmente en el orden dado, uno tras otro. Los valores de retraso se tratan en relación con el tiempo de ejecución de la instrucción anterior. Después de ejecutar todas las declaraciones dentro del bloque, el control se puede pasar a otra parte.

module design0;

bit [31:0] data;

// "initial" block starts at time 0

initial begin

// After 10 time units, data becomes 0xfe

#10 data = 8'hfe;

$display ("[Time=%0t] data=0x%0h", $time, data);

// After 20 time units, data becomes 0x11

#20 data = 8'h11;

$display ("[Time=%0t] data=0x%0h", $time, data);

end

endmodule

En el ejemplo anterior, la primera declaración en el begin-end bloque se ejecutará a las 10 unidades de tiempo, y la segunda declaración a las 30 unidades de tiempo debido a la naturaleza relativa. Son 20 unidades de tiempo después de la ejecución de la instrucción anterior.

ncsim> run [Time=10] data=0xfe [Time=30] data=0x11 ncsim: *W,RNQUIE: Simulation is complete.

Paralelo

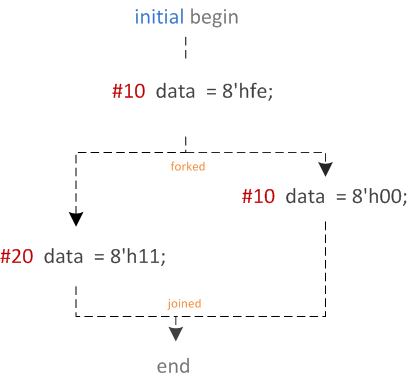

Un paralelo El bloque puede ejecutar declaraciones simultáneamente y el control de retardo se puede usar para proporcionar un orden de tiempo de las asignaciones. Las declaraciones se lanzan en paralelo envolviéndolas dentro del fork y join palabras clave.

initial begin

#10 data = 8'hfe;

fork

#20 data = 8'h11;

#10 data = 8'h00;

join

end

En el ejemplo anterior, fork-join el bloque se lanzará después de ejecutar la declaración en 10 unidades de tiempo. Las declaraciones dentro de este bloque se ejecutarán en paralelo y la primera declaración que se lanzará será aquella en la que a los datos se les asigne un valor de 8'h00, ya que el retraso es de 10 unidades de tiempo después del lanzamiento del fork-join. Después de 10 unidades de tiempo más, se lanzará la primera instrucción y los datos obtendrán el valor 8'h11.

initial begin

#10 data = 8'hfe;

fork

#10 data = 8'h11;

begin

#20 data = 8'h00;

#30 data = 8'haa;

end

join

end

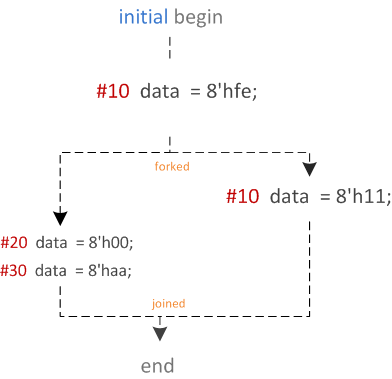

Hay un begin-end block en el ejemplo anterior, y todas las declaraciones dentro del bloque de inicio-fin se ejecutarán secuencialmente, pero el bloque en sí se iniciará en paralelo junto con las otras declaraciones. Entonces, los datos obtendrán 8'h11 en 20 unidades de tiempo, 8'h00 en 30 unidades de tiempo y 8'haa en 60 unidades de tiempo.

Denominación de bloques

Tanto los bloques secuenciales como los paralelos se pueden nombrar agregando : name_of_block después de las palabras clave begin y fork . Al hacerlo, se puede hacer referencia al bloque en un disable declaración.

begin : name_seq

[statements]

end

fork : name_fork

[statements]

join

Verilog

- ¿Cómo la automatización de la preparación de datos acelera el tiempo para obtener información?

- Tutorial de Verilog

- Concatenación Verilog

- Verilog - En pocas palabras

- Asignaciones de Verilog

- Bloqueo y no bloqueo de Verilog

- Bloques de control Verilog

- Funciones de Verilog

- Semántica de programación de Verilog

- Es hora de hacer avanzar sus sistemas de planificación, datos y S&OP

- La mejor forma de usar datos telemáticos