Declaración de asignación de Verilog

Señales de tipo wire o un tipo de datos similar a un cable requiere la asignación continua de un valor. Por ejemplo, considere un cable eléctrico que se usa para conectar piezas en una placa de pruebas. Mientras la batería de +5 V se aplique a un extremo del cable, el componente conectado al otro extremo del cable obtendrá el voltaje requerido.

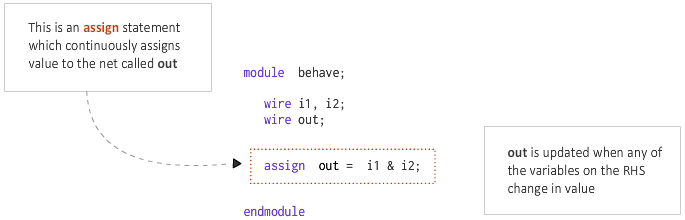

En Verilog, este concepto se realiza mediante el assign declaración donde cualquier wire u otros tipos de datos similares a cables pueden controlarse continuamente con un valor. El valor puede ser una constante o una expresión compuesta por un grupo de señales.

Asignar sintaxis

La sintaxis de asignación comienza con la palabra clave assign seguido del nombre de la señal, que puede ser una sola señal o una concatenación de diferentes redes de señales. La fuerza impulsora y retraso son opcionales y se utilizan principalmente para el modelado de flujo de datos que para sintetizar en hardware real. La expresión o señal del lado derecho se evalúa y asigna a la red o expresión de redes del lado izquierdo.

assign <net_expression> = [drive_strength] [delay] <expression of different signals or constant value>

Los valores de retraso son útiles para especificar retrasos para las puertas y se usan para modelar el comportamiento de tiempo en hardware real porque el valor dicta cuándo se debe asignar a la red el valor evaluado.

Reglas

Hay algunas reglas que deben seguirse al usar un assign declaración:

- LHS siempre debe ser una red escalar o vectorial o una concatenación de redes escalares o vectoriales y nunca un registro escalar o vectorial.

- RHS puede contener registros escalares o vectoriales y llamadas a funciones.

- Siempre que cualquier operando en el RHS cambie de valor, LHS se actualizará con el nuevo valor.

assignlas instrucciones también se denominan asignaciones continuas y siempre están activas

Ejemplo #1

En el siguiente ejemplo, una red llamada es impulsada continuamente por una expresión de señales. i1 e i2 con el AND lógico & formar la expresión.

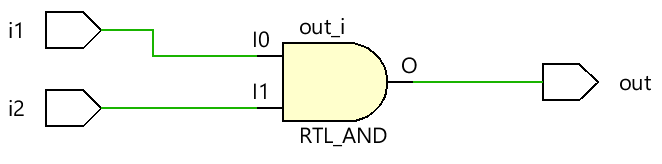

Si, en cambio, los cables se convierten en puertos y se sintetizan, obtendremos un esquema RTL como el que se muestra a continuación después de la síntesis.

La instrucción de asignación continua se puede utilizar para representar puertas combinacionales en Verilog.

Ejemplo #2

El módulo que se muestra a continuación toma dos entradas y usa un assign declaración para impulsar la salida z utilizando selección parcial y concatenaciones de bits múltiples. Trate cada caso como el único código en el módulo, de lo contrario, muchos assign declaraciones en la misma señal definitivamente harán que la salida se convierta en X.

module xyz (input [3:0] x, // x is a 4-bit vector net

input y, // y is a scalar net (1-bit)

output [4:0] z ); // z is a 5-bit vector net

wire [1:0] a;

wire b;

// Assume one of the following assignments are chosen in real design

// If x='hC and y='h1 let us see the value of z

// Case #1: 4-bits of x and 1 bit of y is concatenated to get a 5-bit net

// and is assigned to the 5-bit nets of z. So value of z='b11001 or z='h19

assign z = {x, y};

// Case #2: 4-bits of x and 1 bit of y is concatenated to get a 5-bit net

// and is assigned to selected 3-bits of net z. Remaining 2 bits of z remains

// undriven and will be high-imp. So value of z='bZ001Z

assign z[3:1] = {x, y};

// Case #3: The same statement is used but now bit4 of z is driven with a constant

// value of 1. Now z = 'b1001Z because only bit0 remains undriven

assign z[3:1] = {x, y};

assign z[4] = 1;

// Case #4: Assume bit3 is driven instead, but now there are two drivers for bit3,

// and both are driving the same value of 0. So there should be no contention and

// value of z = 'bZ001Z

assign z[3:1] = {x, y};

assign z[3] = 0;

// Case #5: Assume bit3 is instead driven with value 1, so now there are two drivers

// with different values, where the first line is driven with the value of X which

// at the time is 0 and the second assignment where it is driven with value 1, so

// now it becomes unknown which will win. So z='bZX01Z

assign z[3:1] = {x, y};

assign z[3] = 1;

// Case #6: Partial selection of operands on RHS is also possible and say only 2-bits

// are chosen from x, then z = 'b00001 because z[4:3] will be driven with 0

assign z = {x[1:0], y};

// Case #7: Say we explicitly assign only 3-bits of z and leave remaining unconnected

// then z = 'bZZ001

assign z[2:0] = {x[1:0], y};

// Case #8: Same variable can be used multiple times as well and z = 'b00111

// 3{y} is the same as {y, y, y}

assign z = {3{y}};

// Case #9: LHS can also be concatenated: a is 2-bit vector and b is scalar

// RHS is evaluated to 11001 and LHS is 3-bit wide so first 3 bits from LSB of RHS

// will be assigned to LHS. So a = 'b00 and b ='b1

assign {a, b} = {x, y};

// Case #10: If we reverse order on LHS keeping RHS same, we get a = 'b01 and b='b0

assign {a, b} = {x, y};

endmodule

Asignar variables de registro

Es ilegal conducir o asignar reg escriba variables con un assign declaración. Esto se debe a que un reg variable es capaz de almacenar datos y no requiere ser accionada continuamente. reg las señales solo se pueden controlar en bloques de procedimiento como initial y always .

Asignación continua implícita

Cuando un assign declaración se utiliza para asignar la red dada con algún valor, se llama explícito asignación. Verilog también permite realizar una asignación cuando se declara la red y se llama implícito asignación.

wire [1:0] a;

assign a = x & y; // Explicit assignment

wire [1:0] a = x & y; // Implicit assignment

Diseño Lógico Combinacional

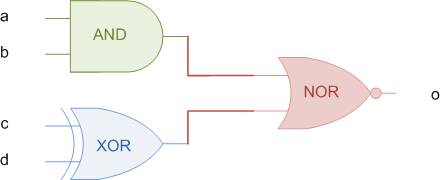

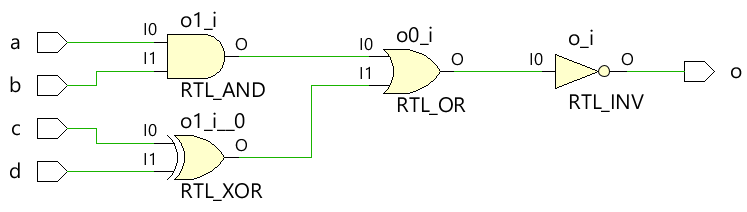

Considere el siguiente circuito digital hecho de puertas combinacionales y el código Verilog correspondiente.

La lógica combinacional requiere que las entradas se controlen continuamente para mantener la salida, a diferencia de los elementos secuenciales como los flip flops, donde el valor se captura y almacena en el borde de un reloj. Entonces un assign declaración se ajusta al propósito del pozo porque la salida o se actualiza cada vez que cambia cualquiera de las entradas en el lado derecho.

// This module takes four inputs and performs a boolean

// operation and assigns output to o. The combinational

// logic is realized using assign statement.

module combo ( input a, b, c, d,

output o);

assign o = ~((a & b) | c ^ d);

endmodule

Esquema de hardware

Después de la elaboración y síntesis del diseño, podemos ver un circuito combinacional que se comportaría de la misma manera que el modelado por el assign declaración.

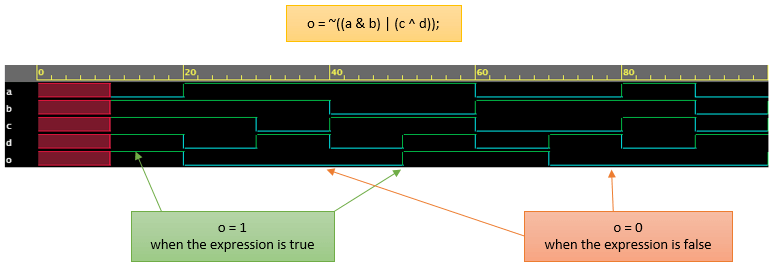

Vea que la señal o se convierte en 1 cada vez que la expresión combinacional en el RHS se vuelve verdadera. De manera similar, o se convierte en 0 cuando RHS es falso. La salida o es X de 0ns a 10ns porque las entradas son X durante el mismo tiempo.

¡Haga clic aquí para ver una presentación de diapositivas con un ejemplo de simulación!

Verilog