Efectos de las variaciones de grabado en la formación de canales Ge / Si y el rendimiento del dispositivo

Resumen

Durante la formación de estructuras de aletas de Ge en un sustrato de silicio sobre aislante (SOI), descubrimos que el proceso de grabado en seco debe controlarse cuidadosamente. De lo contrario, puede provocar un sobregrabado de Ge o la formación de un perfil de aleta de Ge no deseado. Si el proceso de grabado no está bien controlado, la estructura superior de Ge / SOI se graba y solo queda la capa de aleta de Si. En este caso, el dispositivo presenta características anormales. El proceso de grabado está emergiendo como un paso crítico en el escalado y empaquetado de dispositivos y afecta los intentos de aumentar la densidad de empaque y mejorar el rendimiento del dispositivo. Por tanto, se sugiere que la optimización del funcionamiento del reactor de plasma se realice mediante simulaciones, con el fin de no solo ajustar los parámetros del proceso utilizados sino también modificar el hardware empleado. Vamos a desarrollar dispositivos sin empalmes Ge empleando parámetros de fabricación actualizados. Además, queremos eliminar las dislocaciones desajustadas en la interfaz o reducir las dislocaciones de roscado aplicando un proceso de recocido térmico cíclico para cumplir con el objetivo de obtener una estructura suspendida de capas epitaxiales de Ge con alta calidad.

Antecedentes

Una forma de aumentar la velocidad de respuesta de los dispositivos semiconductores y reducir su consumo de energía es utilizar un semiconductor con una alta movilidad de portadora. Ejemplos de tales materiales incluyen Ge, así como sus aleaciones y compuestos. Sin embargo, cuando se forma una estructura apilando una capa de un material semiconductor sobre un sustrato de un semiconductor diferente, pueden surgir problemas. Por ejemplo, la diferencia en los tamaños de la red del sustrato semiconductor y la capa superpuesta de un material semiconductor diferente puede causar dislocaciones, que pueden tener un efecto adverso en el rendimiento del dispositivo. Convencionalmente, para fabricar dispositivos semiconductores basados en Ge que incluyen un sustrato de Si, se forma una capa amortiguadora o capa de sacrificio más gruesa (por ejemplo, una capa amortiguadora Si / Ge) sobre el sustrato de silicio. Posteriormente, se hace crecer una capa epitaxial de Ge sobre la capa tampón de Si / Ge. A continuación, los procesos de grabado anisotrópico e isotrópico se realizan secuencialmente para eliminar una parte de la capa tampón y retener la capa epitaxial de Ge. Los dispositivos VLSI deben mostrar una alta corriente de accionamiento, baja corriente de fuga en estado apagado y bajo voltaje de suministro para garantizar un alto rendimiento, incluido un bajo consumo de energía en espera y una disipación de energía dinámica reducida. Actualmente, la movilidad mejorada por deformación, la puerta de metal de alta k y la arquitectura de dispositivo tridimensional (3D) en el nodo de 22 nm [1] son algunas de las tecnologías que se utilizan para el escalado continuo de semiconductores de óxido de metal complementario ( CMOS) dispositivos con canal Si. Además de características como la alta movilidad, se necesitan nuevas arquitecturas de dispositivos como las de gate-all-around (GAA) [2] y transistores de efecto de campo de cuerpo ultradelgado (FET) [3] para mejorar el control electrostático en el subwoofer. -Nodos de 10 nm. Se han demostrado pFET GAA [4] y nFET [5] basados en Ge con funcionamiento en modo de inversión (INV). Sin embargo, la formación de uniones en los dispositivos Ge INV es un problema crítico debido a la baja solubilidad del dopante, la rápida difusión del dopante y el bajo presupuesto térmico. Para resolver estos problemas, se han sugerido como alternativas los dispositivos sin unión (JL) [6] que utilizan un canal con dopado pesado con el mismo tipo de portadora que el de las regiones de fuente / drenaje (S / D). Sin embargo, el escalado rápido de transistores requiere el desarrollo de dispositivos nuevos y más efectivos que puedan ponerse al día con los transistores modernos. En los últimos años, se ha descubierto que los JL-FET son prometedores como transistores de próxima generación. El JL-FET es básicamente una resistencia en la que la puerta puede controlar la densidad de la portadora móvil. En el estado ON, existe una gran corriente corporal, debido a la concentración de dopaje relativamente alta en la región del canal; la corriente de acumulación de superficie se agrega a esta corriente El nivel de dopaje en el JL-FET debe ser alto para lograr un impulso de corriente adecuado, mientras que la sección transversal del dispositivo debe ser lo suficientemente pequeña como para que el dispositivo se pueda apagar . Sin embargo, en el caso de JL-FET altamente dopados, las portadoras sufren una importante dispersión de impurezas, debido a la cual la corriente de excitación se degrada significativamente [7]. Además, los JL-FET tienen la ventaja de ser simples de fabricar y tienen una alta movilidad de carga y una baja capacitancia de puerta, en contraste con los dispositivos INV [8,9,10,11,12]. Recientemente, se demostraron pMOSFET de doble puerta [13] y tri-puerta atada al cuerpo [14] Ge JL-FET en sustratos de germanio sobre aislante y Si a granel, respectivamente.

A medida que los dispositivos microelectrónicos continúan reduciéndose y los requisitos del proceso se vuelven cada vez más estrictos, el modelado y la simulación de plasma se vuelven cada vez más atractivos como herramienta para el diseño, control y optimización de reactores de plasma [15]. Se utilizan varias técnicas para simular el comportamiento de los procesos del plasma en función de la disparidad en la duración y las escalas de tiempo. Una de las técnicas de simulación, la dinámica de fluidos computacional (CFD), se usa ampliamente para predecir los campos de flujo para características de diseño de ingeniería y para extrapolar limitaciones experimentales. Su modelado se ha aplicado para investigar los fenómenos de mezcla de flujo [16], pero es un estudio poco común en el proceso de grabado. Por lo tanto, este estudio propuso caracterizar en detalle el campo de flujo térmico de los reactores de plasma para el proceso de grabado, y luego deducir parámetros numéricos que pueden ser beneficiosos para los experimentos.

En este trabajo, se realizó un grabado para formar capas epitaxiales de Ge suspendidas sobre Si, así como otros semiconductores de aleación para la integración del dispositivo. Los resultados simulados serán validados por experimentos; por lo tanto, las condiciones iniciales y de contorno, así como los parámetros del modelo numérico, se modificarán para mejorar la confiabilidad de los datos. Anticipamos que los parámetros óptimos pueden obtenerse mediante experimentos y simulaciones para mejorar las técnicas de grabado y cumplir con este desarrollo de transistor al realizar un proceso de fabricación de mayor calidad y un menor costo de producción.

Métodos / Experimental

Los sustratos de partida fueron obleas SOI con una capa superior de silicio de 70 nm (tipo p, 9-18 Ω cm). Las obleas se limpiaron utilizando los procesos RCA estándar limpio 1 (SC-1) y RCA estándar limpio 2 (SC-2), con el fin de eliminar cualquier materia orgánica, metales no deseados y partículas presentes. A continuación, se enjuagó con agua desionizada y se secó en N 2 . La película de Ge se depositó en un reactor epitaxial de deposición de vapor químico a baja presión (Epsilon 2000, ASM) usando GeH 4 al 10% como precursor. Se utilizó hidrógeno como gas portador. Antes de la deposición de la película de Ge, se realizó un pretratamiento in situ a base de HCl a 850 ° C y 10 Torr para preparar la superficie de la oblea. Luego, la temperatura del sustrato se cambió a 400 ° C para hacer crecer una película de Ge en la oblea SOI usando 10% de GeH 4 . Los espesores de las películas de Ge depositadas se determinaron mediante microscopía electrónica de transmisión (TEM, emisión térmica tipo Schottky, 0,5-200 kV). Las cristalinidades de las películas de Ge se examinaron mediante análisis de difracción de rayos X (XRD) (D8A, Bruker, radiación CuKα, λ =1.5408 Å, 20-70 °). Además, se realizaron exploraciones Ω – 2θ alrededor del pico de difracción (004) utilizando un sistema X’Pert MRD (PANalytical). Se usó un colimador de cristales cortados en canal de Ge {400} doble para seleccionar la radiación CuKα1. Durante las mediciones estándar de XRD, la muestra se fijó en una posición horizontal y la fuente y el brazo detector del difractómetro se movieron en el modo θ – θ. El mapeo del espacio recíproco se realizó en el modo de resolución media utilizando el colimador de cristal mencionado anteriormente; Había hendiduras de 0,4 mm de ancho en el brazo detector frente al contador de centelleo. Los espesores de las capas de Ge se determinaron mediante medidas de elipsometría (M2000, J. A. Woollam Co., λ =193-1690 nm). La aleta se formó mediante grabado con plasma anisotrópico utilizando Cl 2 / Gas HBr. Después de la formación del ZrO 2 / Puerta TiN, los S / D se implantaron con B (1 × 10 15 cm −2 , 15 keV) y se activa mediante un recocido térmico rápido a 550 ° C durante 30 s.

Grabado en seco altamente selectivo del mecanismo de germanio

Las reacciones de electrones y neutrales son isotrópicas, mientras que las reacciones de iones son altamente direccionales y varían con el sesgo aplicado. Ajustando la potencia de polarización, los iones se pueden acelerar a lo largo de la dirección deseada para ayudar a la reacción de grabado. En general, se acepta que el Br no reacciona espontáneamente con el Si y que se necesitan iones energéticos para que se produzca la reacción. Los átomos de Br y Cl asistidos por iones pueden reaccionar con átomos de Ge o Si de forma espontánea bajo activación para formar los productos volátiles GeBr 4 , GeCl 4 , SiBr 4 y SiCl 4 , que se desorben de la superficie del sustrato y se pueden bombear. Se ha demostrado que esta reacción química asistida por iones de Si con Br es altamente anisotrópica. Se obtuvieron tasas de grabado vertical más altas usando HBr para variaciones de potencia de sesgo, lo que confirma que la adición de HBr en Cl 2 puede mejorar la velocidad de grabado [17]. Dado que el plasma basado en Cl y Br graba Ge y Si mediante un mecanismo asistido por iones, la energía de iones como Br + , Br 2+ , HBr + , Cl + y Cl2 + se puede controlar presionando el soporte del sustrato. No hay un cambio pronunciado en la tasa de grabado lateral al variar la potencia de polarización tanto para el grabado en la superficie superior como en el área de cuello. Se encontraron cortes en las estructuras de las aletas grabadas con mezclas de HBr, en el área del cuello, ya que el ataque lateral fue mejorado por los defectos a lo largo de la interfaz Ge / Si. Y también la máscara influye potencialmente en la evolución de la forma debido al impacto de la pared lateral por el flujo de iones. Este fenómeno se amplifica a medida que el perfil se vuelve más profundo y a medida que aumenta el componente de velocidad del ión lateral. Debido a la alta dependencia angular del proceso de grabado con plasma de HBr [18], por lo tanto, se puede concluir que la estructura cristalina es relativamente más débil en la interfaz Ge / Si debido a los átomos parcialmente unidos de las dislocaciones de desajuste y la relativamente débil Enlaces Ge-Ge y Ge-Si. Ajustando la proporción de HBr / Cl 2 y potencia de polarización, se pueden obtener diferentes tipos de estructuras en forma de aletas durante la fabricación del dispositivo Ge. Las propiedades de grabado de Ge y Si son muy similares. Los gases que atacan el Si generalmente atacan el Ge a una velocidad mayor. Se ha demostrado que las resistencias de los enlaces Ge y Si son Ge-Ge =263,6 ± 7,1 kJ mol −1 y Si-Si =325 ± 7 kJ mol −1 [2]. Se aplicaron diferentes poderes de polarización para ajustar la tasa de grabado vertical mediante la aceleración direccional de los iones. Las imágenes se registraron después del proceso de apilado de puertas. La tasa de grabado vertical se calculó a partir de la altura de la película con respecto al sustrato de óxido. Las tasas de grabado lateral se determinaron a partir de dos partes de la aleta:el grabado lateral en la superficie superior de la aleta y el grabado en el área de formación del cuello cerca de la interfaz Ge / Si. En resumen, se descubrió experimentalmente que el poder de sesgo es el parámetro más crítico en el proceso de grabado y, por lo tanto, afecta las características del dispositivo en consecuencia.

En este estudio, todos los procesos de grabado se realizaron en un reactor TCP 9600 de Lam Research. Este es un reactor de plasma acoplado por transformador que permite un control separado de la potencia de la bobina (electrodo superior) y la polarización del sustrato (electrodo inferior). Se incorporó refrigeración por la parte trasera con helio para permitir que la temperatura del sustrato se controle de forma más eficaz. Las muestras se montaron en un tubo de 6 pulgadas. Oblea portadora de Si con grasa de vacío antes de introducirla en la cámara de grabado. HBr / Cl 2 Se aprovechó la química para el proceso de grabado anisotrópico. La presión del proceso se controló a 10 mTorr. La configuración y las condiciones experimentales detalladas se ilustran en el estudio de Hsu et al. [4].

Modelo físico

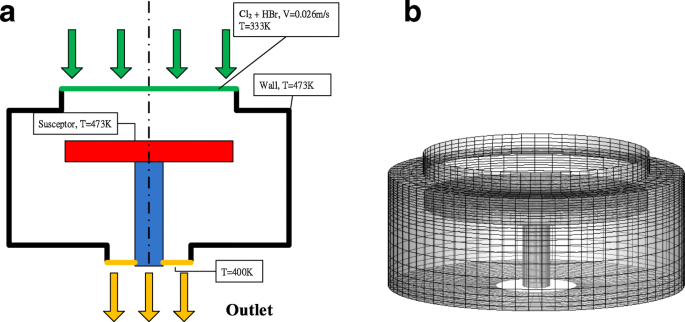

El CFD se utiliza para acceder a la información interna dentro del reactor y el flujo se considera laminar con la condición de límite de deslizamiento debido a un mayor número de Knudsen en la cámara (Fig. 1). En la presente simulación, el flujo térmico del plasma se considera una mezcla en las ecuaciones de cantidad de movimiento; El transporte de partículas se considera en las ecuaciones que gobiernan las especies y las reacciones químicas están involucradas en la pared del susceptor. Un caso modelo para simulación se ilustra en la Fig. 3. El gas de entrada es una mezcla de cloro (Cl 2 ) y bromuro de hidrógeno (HBR). La veloci de manera uniforme, repetible, y finalmente para ser descargado del reactor. Después de construir el modelado sólido por el software CAD, el sistema de malla se construyó en cuadrículas estructuradas con 50, 000 nodos como se muestra en la Fig. 3. La ecuación de conservación transitoria para el transporte de una cantidad escalar ϕ se demuestra mediante la siguiente ecuación escrita en integral formulario para un volumen de control arbitrario V de la siguiente manera [19]:

Modelo físico para simulación numérica de reactor de plasma. un El esquema de la cámara del reactor con condiciones de contorno prescritas. b Sistema de malla para simulaciones numéricas

$$ \ frac {d} {dt} \ underset {V} {\ oint} \ rho \ varphi \; dV + \ oint \ kern0.27em \ rho \ varphi \ overset {\ rightharpoonup} {v} \ cdot \ mathrm { d} \ overrightarrow {\ mathrm {A}} =\ oint \ Gamma \ mathrm {\ nabla} \ varphi \ cdot \ mathrm {d} \ overrightarrow {\ mathrm {A}} + {\ int} _ {\ mathrm { V}} {\ mathrm {S}} _ {\ varphi} \ mathrm {dV} $$ (1 *)donde ρ indica densidad; \ (\ overset {\ rightharpoonup} {v} \) es un vector de velocidad; \ (\ overset {\ rightharpoonup} {A} \) es el vector de área de superficie; V es volumen; Γ es el coeficiente de difusión para ϕ y S ϕ es el término fuente de ϕ por unidad de volumen. El símbolo ϕ se puede reemplazar por 1 para la ecuación de continuidad, u , v y w son las ecuaciones de momento en las direcciones X, Y y Z, y Ci para las ecuaciones de transporte de especies en la cámara del reactor, respectivamente. Eq. (1 *) se puede expresar en coordenadas generalizadas utilizando el método de volumen finito para la simulación. Después de combinar las condiciones de contorno, la ecuación. (1 *) se puede linealizar y expresar en el dominio computacional como un conjunto de ecuaciones algebraicas, que se pueden resolver mediante el algoritmo SIMPLE utilizando la técnica CFD [19]. Observó que la mayoría de los dispositivos de fabricación de semiconductores funcionan muy por debajo de la presión atmosférica. A presiones tan bajas, el flujo de fluido está en el régimen de deslizamiento y las condiciones de límite de no deslizamiento normalmente utilizadas para la velocidad y la temperatura ya no son válidas. El actual flujo de plasma a muy baja presión se encuentra en el régimen de deslizamiento, que se encuentra entre el flujo molecular libre y el régimen continuo [20]. Por lo tanto, las condiciones de límite de deslizamiento para la velocidad y la temperatura para modelar el flujo de fluido se imponen en nuestras simulaciones numéricas.

Los materiales semiconductores Si (s) y Ge (s) se graban en la superficie del susceptor calentada gobernada por las siguientes reacciones superficiales:

$$ {\ mathrm {Cl}} _ 2+ \ mathrm {Si} ={\ mathrm {SiCl}} _ 4 $$ (2 * .1) $$ 4 \ mathrm {HBr} + \ mathrm {Si} ={\ mathrm {SiBr}} _ 4 + 2 {\ mathrm {H}} _ 2 $$ (2 * .2) $$ 2 {\ mathrm {Cl}} _ 2+ \ mathrm {Ge} ={\ mathrm {GeCl}} _ 4 $$ (2 * .3) $$ 4 \ mathrm {HBr} + \ mathrm {Ge} ={\ mathrm {GeBr}} _ 4 + 2 {\ mathrm {H}} _ 2 $$ (2 * .4)Las reacciones químicas son similares para el grabado de Si en la Ec. (2 * .1) y Eq. (2 * .2), o grabado con Ge en la Ec. (2 * .3) y Eq. (2 * .4). Por lo tanto, el proceso de grabado de Si mediante la mezcla de cloro y bromuro de hidrógeno se demuestra en las siguientes simulaciones.

Resultados y discusión

Caracterización del material

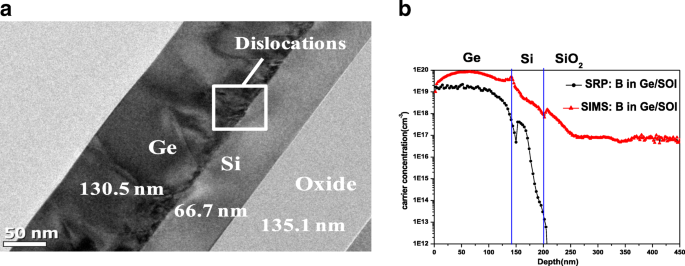

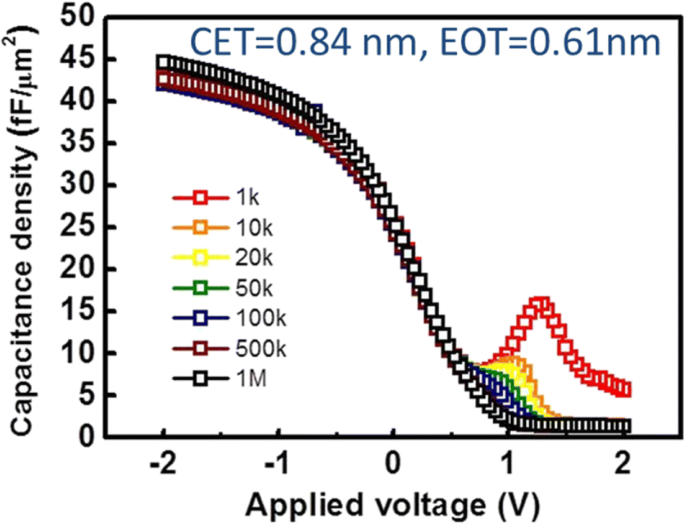

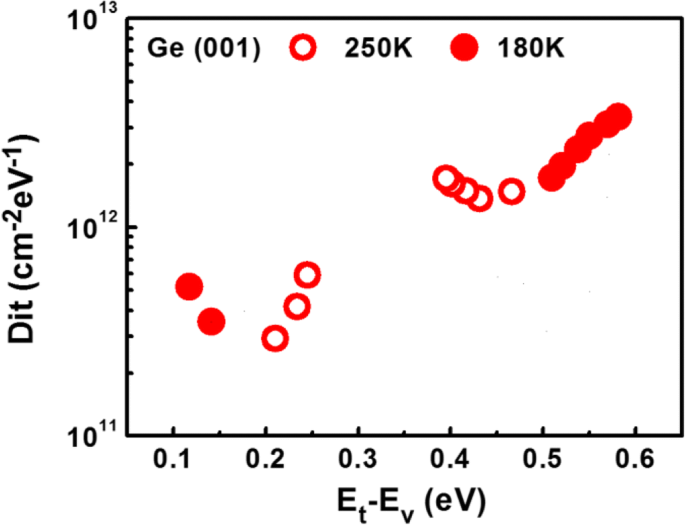

Las imágenes TEM de sección transversal de la capa de Ge formada sobre el sustrato SOI se muestran en la Fig. 2a. Como puede verse, las dislocaciones de desajuste están presentes en la interfaz Ge / Si; éstos, a su vez, dan como resultado dislocaciones enhebradas a través de la película de Ge epitaxial. Se cree que estas dislocaciones de roscado se adaptan al desajuste térmico entre Ge y Si. La mayoría de las dislocaciones de subprocesos terminaron dentro de los 80 nm desde la interfaz; sin embargo, muchos también se propagaron a la superficie de la película. La película epitaxial de Ge sobre el sustrato SOI se implantó con boro y posteriormente se activó, con el fin de examinar la distribución del dopante y el nivel de activación. Para la parte superior de 130 nm de la capa de Ge, la tasa de activación del boro fue ∼ 85%, como se muestra en los perfiles PCOR-SIMS y de perfil de resistencia a la propagación (SRP). (ver Fig. 2b). La concentración de huecos se redujo significativamente en el caso del fondo de la capa de Ge cerca de la interfaz Ge / Si, debido a la presencia de defectos y debido a los límites de medición de SRP. En el caso de los dispositivos fabricados, el Ge defectuoso cerca de la interfaz Ge / Si se eliminó mediante grabado selectivo; por lo tanto, las mediciones de PCOR-SIMS y SRP realizadas en el canal deben ser precisas. El nivel máximo de activación de ~ 3 × 10 19 cm −3 es completamente consistente con el límite de activación convencional. Tenga en cuenta que debido a la activación a baja temperatura (550 ° C) realizada durante la implantación de boro, el S / D cerca del canal de Si parásito fue altamente resistivo (Fig. 2); esto impidió la conducción parasitaria de Si. La Figura 3 muestra las características de capacitancia-voltaje (CV) del TiN / ZrO 2 / Condensadores semiconductores-aislantes metálicos (MISCAPs). Para evitar la formación de una GeO x inestable capa durante la deposición dieléctrica de alto k y el proceso de recocido posterior a la deposición, el material a base de nitruro Ge 3 N 4 y no GeO 2 se insertó como la capa de interfaz en la superficie Ge (001) a través de un NH 3 / H 2 tratamiento con plasma remoto. El ZrO 2 La capa se depositó a 250 ° C durante 20 ciclos mediante deposición de la capa atómica. Las curvas CV medidas no indican dispersión de frecuencia o estiramiento de 1 KHz a 1 MHz y son consistentes. La pérdida, que crea niveles de trampa cerca del ZrO 2 / Ge interfaz, desplaza la energía de activación térmica para la generación de portadores minoritarios de la correspondiente a la energía de banda prohibida p-Ge a la energía de banda intermedia. El espesor de óxido equivalente (EOT) es de 0,6 nm y la D eso (Densidad de interfaz-trampa) es ~ 3 × 10 12 cm 2 eV −1 cerca del espacio medio, medido por el método de conductancia a baja temperatura (ver el recuadro de la Fig. 4).

un La imagen TEM del Ge de tipo p en el sustrato SOI. b Los perfiles SIMS y SRP de la capa de epi-Ge dopada con boro in situ en SOI. La concentración del agujero es baja en el fondo defectuoso Ge cerca de la interfaz Ge / Si

Características C-V del TiN / ZrO 2 / Ge MISCAPs con EOT ~ 0.6 nm

Dit medido por el método de conductancia a baja temperatura

Simulación de los parámetros de funcionamiento del reactor

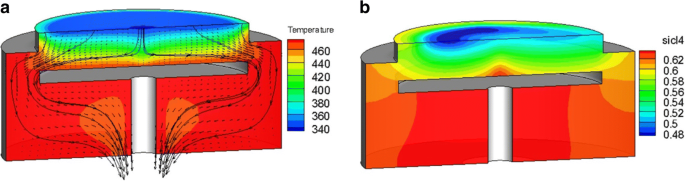

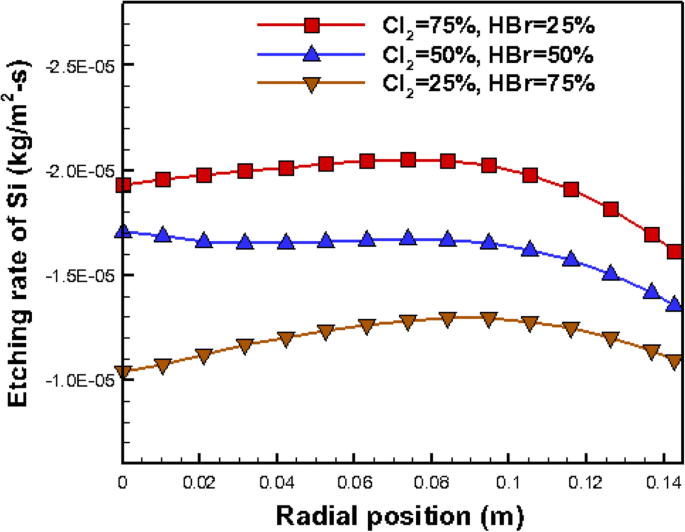

Se simuló un modelo típico de flujos de plasma laminar estables en computadoras personales de alta velocidad. El gas de entrada es una mezcla de Cl 2 , que tiene una fracción de masa de 0,75, y HBr, que tiene una fracción de masa de 0,25. La figura 5a ilustra los contornos del flujo de entrada a baja temperatura, operando a una temperatura más alta en el interior y las líneas de trayectoria de las partículas en la cámara del reactor. La Figura 5b muestra los contornos de la fracción de masa del producto SiCl4, que tiene una baja concentración por encima del susceptor y una alta concentración por debajo del susceptor hasta la salida. Además, mayor fracción de masa de Cl 2 obtiene un buen rendimiento en el grabado, y este conocimiento ha sido validado por las simulaciones actuales como se muestra en la Fig. 6. El eje horizontal representa a lo largo de una posición radial en el susceptor y el eje vertical indica la velocidad de grabado (kg / m 2 s) de Si. La Figura 6 muestra que el mejor proceso de grabado se archiva mediante la mezcla de entrada de 75% Cl 2 y 25% HBr, y esta mezcla se adoptó para realizar experimentos en este estudio.

Contornos de los parámetros del plasma dentro del reactor. un Distribución de temperatura y líneas de trayectoria de partículas r. b Contornos de fracción de masa del producto SiCl 4

Tasas de grabado de Si en el susceptor a partir de mezclas de gases de entrada con varias fracciones

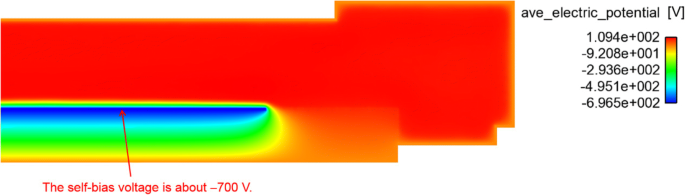

Otro caso que muestra la viabilidad de un experimento asistido por computadora es la distribución del potencial eléctrico en la cámara para el grabado con plasma. Basado en el mecanismo subyacente de este proceso de grabado, se desarrolló un modelo de simulación 2D para la distribución de la densidad de potencia del plasma como se muestra en la Fig.7 y se utilizó para ajustar los datos de medición, con el fin de confirmar la precisión del modelo y ayudar el experimento.

Simulación de distribución de potencial eléctrico para grabado con plasma en la cámara

Según lo propuesto por Sugai [21], el voltaje de autopolarización se puede relacionar con las capacitancias de la vaina en el electrodo de RF (C K ) y electrodo de tierra (C A ), y se expresa de la siguiente manera:

$$ {V} _ {\ mathrm {DC}} =\ frac {C _ {\ mathrm {K}} - {C} _ {\ mathrm {A}}} {C _ {\ mathrm {K}} + {C } _ {\ mathrm {A}}} \ {V} _ {\ mathrm {RF}} $$ (3 *)Según las simulaciones actuales, como se muestra en la Fig. 7, el voltaje de autopolarización es de aproximadamente - 700 V, que está cerca del valor teórico, - 650 V, calculado a partir de la Ec. (3 *). Por lo tanto, se sugiere que la optimización se realice mediante simulaciones para no solo ajustar los parámetros de proceso utilizados, sino también modificar el hardware empleado. Esto ayudará a garantizar la uniformidad en toda la ejecución y conducirá a procesos de alta calidad y bajo costo que están optimizados.

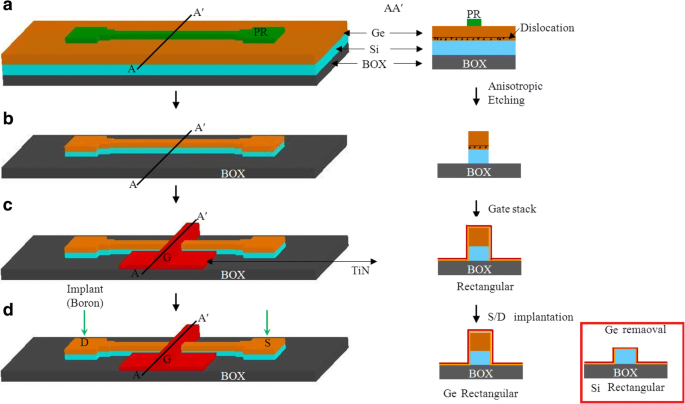

Fabricación y caracterización de dispositivos

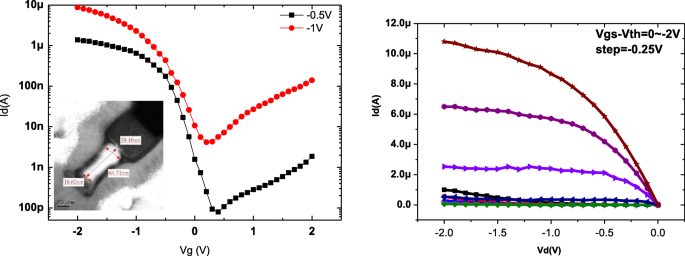

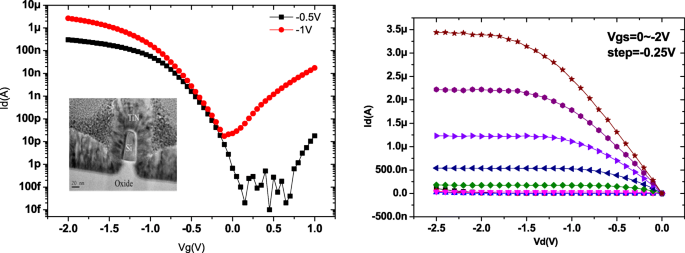

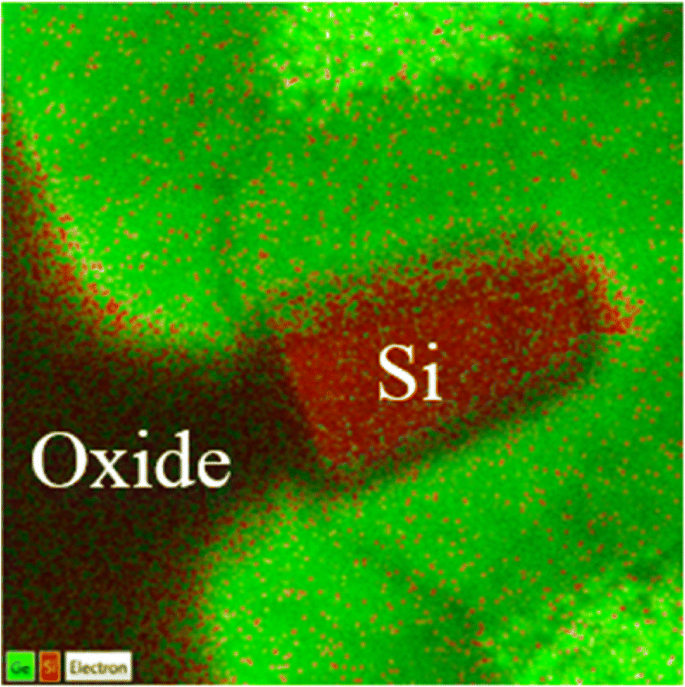

La capa epitaxial de Ge se modeló en aletas con los tamaños de características deseados utilizando litografía de haz de electrones. La aleta se formó mediante grabado anisotrópico con Cl 2 / Plasma a base de HBr para eliminar la interfase Ge cerca de Ge / Si altamente defectuosa. La aleta de Ge flotante en SOI se formó con la mayor selectividad de grabado de Ge que Si y la tasa de grabado mejorada de la región defectuosa [4]. A SiO 2 A continuación, se depositó la capa de remate y se convirtió en el espaciador después del patrón de la puerta. Después de definir la región activa, la puerta se apila de ZrO 2 capa fueron formados por ALD, respectivamente. Las secciones transversales del canal de los dispositivos fabricados se muestran en la Fig. 8. El ancho de la aleta ( W aleta ) se utiliza para la concentración de canal de 8 × 10 19 cm - 3 que se extrae mediante el método de van der Pauw en una capa de Ge epi manta sobre SOI. Tenga en cuenta que la capacidad de control del canal disminuye con el aumento de la concentración del canal y el aumento de W aleta [12, 13]. La concentración de canal grande requiere la pequeña W aleta para mantener el SS bajo. Finalmente, se definieron y depositaron los electrodos de puerta. La Figura 9 muestra las características de salida y transferencia de un Ge FinFET triangular con un ancho de aleta ( W aleta ) de 18 nm y longitud de puerta ( L g ) de 90 nm. El yo en / Yo desactivado la proporción de Ge JL-FET es tan alta como 10 5 y la oscilación del subumbral (SS) es ~ 100 mV dec - 1 . Las características de transferencia del Si JL-FET se muestran en la Fig. 10. El I en / Yo desactivado La proporción de Si JL-FET es tan alta como ~ 10 8 , su SS es 90 mV dec - 1 , es L g es de 80 nm y su W aleta es de 20 nm. La Figura 8 también muestra que el intervalo del voltaje de la puerta, Δ V g , es de aproximadamente 0,5 V y está cerca de la banda prohibida de Ge ( E g / q =0,66 V). Esto confirma que el I d - V g Las curvas que se muestran en la Fig. 8 son para un Ge FinFET. Sin embargo, el intervalo del voltaje de la puerta, Δ V g , que se muestra en la Fig.6 es de aproximadamente 1,8 V y está cerca de la banda prohibida de Si ( E g / q =1,1 V) pero no la de Ge ( E g / q =0,66 V). Por lo tanto, el yo d - V g Las curvas que se muestran en la Fig. 9 son para un Si JL-FET y no para un Ge JL-FET. Esta observación se basa en la física de los dispositivos semiconductores y está respaldada por la I determinada experimentalmente d - V g curvas de los FinFET de Ge y Si, así como los mapas de sección transversal TEM / EDS Si. Dos cosas son evidentes en los recuadros de la Fig. 11. Los recuadros muestran las características de salida y transferencia del Si JL-FET inesperado después de la sobreextensión de Ge; el yo en / Yo desactivado la proporción de este dispositivo es tan alta como 10 8 . Sin embargo, su corriente ON es de solo 17 μA μm - 1 en - 1 V. El alto I en / Yo desactivado La relación es atribuible a la capa de Si y no a la capa de Ge. Cuando solo queda la capa de Si, el dispositivo es en realidad un Si JL-FET en lugar de un Ge JL-FET.

Esquema de la fabricación del dispositivo. un Patrón de aleta. Los materiales de partida son Ge (130 nm) en BOX. b Grabado anisotrópico y rayado fotorresistente. c Formación de puertas por deposición de capa atómica de ZrO 2 y deposición de TiN. d Implante de boro autoalineado en S / D para un buen contacto. Nota:el lado izquierdo son los esquemas 3D y el lado derecho es la vista transversal correspondiente

yo d - V gy I d - V d curva para el Ge FinFET

yo d - V gy I d - V d para el Si FinFET después de que la parte superior Ge se haya grabado descuidadamente. Aunque yo en / Yo desactivado puede llegar a 10 8 , su valor actual es muy bajo

Mapeo TEM para la estructura del canal que se somete a un proceso de sobregrabado

Conclusiones

Confirmamos la relación entre el modelo de simulación y los datos de medición. Por lo tanto, se sugiere que la optimización se realice mediante simulaciones para no solo ajustar los parámetros de proceso utilizados, sino también para modificar el hardware empleado. Con la ayuda de simulaciones numéricas para determinar los parámetros operativos para el rector, demostramos que los parámetros para el proceso de grabado para formar canales Ge / Si se pueden optimizar a través de experimentos, con el fin de mejorar el proceso de grabado y ayudar al desarrollo de transistores mediante mejorando la calidad de fabricación y reduciendo el costo de producción. Los resultados experimentales indicaron que la técnica de grabado en seco desarrollada para Ge FinFETs también es extremadamente útil para la fabricación de dispositivos CMOS de aleta alta.

Nanomateriales

- Tecnologías avanzadas de deposición de capas atómicas para micro-LED y VCSEL

- Ingeniería del proceso de recubrimiento por inmersión y optimización del rendimiento para dispositivos electrocrómicos de tres estados

- Características de alineación interfacial, eléctrica y de banda de pilas de HfO2 / Ge con capa intermedia de SiO2 formada in situ mediante deposición de capa atómica mejorada por plasma

- Dopaje sustitutivo para aluminosilicato mineral y rendimiento superior de separación de agua

- Características ópticas y eléctricas de los nanocables de silicio preparados por grabado electrolítico

- Los efectos de la relación Li / Nb en la preparación y el rendimiento fotocatalítico de los compuestos Li-Nb-O

- Ajuste de las morfologías de la superficie y las propiedades de las películas de ZnO mediante el diseño de la capa interfacial

- Preparación y rendimiento fotocatalítico de fotocatalizadores LiNb3O8 de estructura hueca

- Los efectos de acoplamiento de los polaritones de plasma superficial y las resonancias magnéticas dipolo en metamateriales

- Efectos de la fotoconductividad, la sensibilidad al pH, el ruido y la longitud del canal en los sensores FET de nanocables de Si

- Grabado láser y grabado láser