Ge pMOSFET de alta movilidad con pasivación de Si amorfo:impacto de la orientación de la superficie

Resumen

Reportamos la pasivación de Si amorfo de Ge pMOSFETs fabricados en superficies orientadas (001) -, (011) - y (111) para aplicaciones avanzadas de CMOS y transistores de película delgada. La pasivación de Ge con Si amorfo se lleva a cabo mediante pulverización catódica con magnetrón a temperatura ambiente. Con el espesor fijo de Si t Si Los pMOSFET de Ge orientados a (001) alcanzan la corriente en estado más alta I ACTIVADO y movilidad efectiva del agujero μ ef en comparación con los dispositivos en otras orientaciones. Con una densidad de carga de inversión Q inv de 3,5 × 10 12 cm −2 , Transistores Ge (001) con 0,9 nm t Si demostrar un pico μ ef de 278 cm 2 / V × s, que es 2,97 veces mayor que la movilidad universal de Si. Con la disminución de t Si , yo ACTIVADO de transistores Ge aumenta debido a la reducción del espesor efectivo capacitivo, pero las características del piso de fuga y oscilación por debajo del umbral se degradan debido al aumento de la brecha media D eso .

Antecedentes

El germanio (Ge) ha atraído un gran interés en la investigación para aplicaciones avanzadas de CMOS y transistores de película delgada debido a su mayor movilidad de orificios y menor procesamiento de presupuesto térmico en comparación con Si [1, 2, 3, 4, 5, 6]. Para lograr la alta movilidad del canal, se requiere el proceso de pasivación de la superficie que conduce a una alta calidad de interfaz antes de la formación de la pila de puertas. Se han desarrollado varias técnicas de pasivación de superficie para ofrecer los beneficios de la movilidad del portador en los transistores de efecto de campo semiconductores de óxido metálico (MOSFET) [1, 2, 7,8,9,10]. Entre estas técnicas, una capa de silicio (Si) pasivada en Ge ha sido el punto caliente en los últimos años, debido a sus ventajas de supresión efectiva de estados de interfaz y buena estabilidad térmica y confiabilidad [11]. La formación de la capa de pasivación de Si se ha estudiado ampliamente mediante la deposición química en fase de vapor (CVD) con precursores de SiH 4 [1], Si 2 H 6 [4], Si 3 H 8 [12] y evaporación por haz de electrones [13]. Aunque el método CVD podría proporcionar una capa de pasivación más uniforme que la deposición física de vapor (PVD), su tasa de pasivación tiene una fuerte correlación en la orientación de la superficie del canal y la temperatura del proceso. La técnica PVD podría proporcionar una tasa de pasivación mejorada incluso a temperatura ambiente, que tiene las ventajas de un bajo presupuesto térmico y un bajo costo, lo que la hace más adecuada para los transistores de película delgada y las aplicaciones de integración 3D back-end-of-line. En esta carta, fabricamos pMOSFET de Ge de alta movilidad en superficies orientadas (001) -, (011) - y (111) utilizando pasivación de Si amorfo por pulverización catódica con magnetrón. Movilidad de agujero efectiva significativamente mejorada μ ef se logra en transistores Ge en comparación con la movilidad universal Si. Impactos de la orientación de la superficie y el espesor del Si t amorfo Si sobre el efecto potenciador de la pasivación de Si amorfo en μ ef se estudian.

Métodos

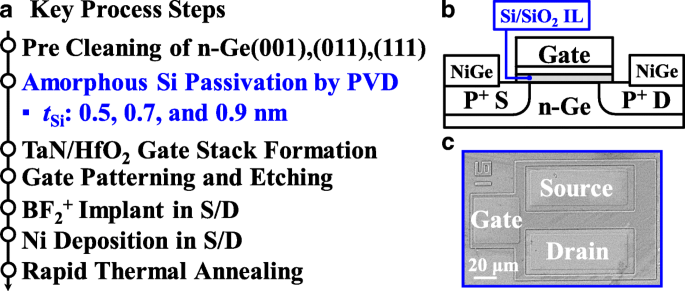

La Figura 1a muestra los pasos clave del proceso para fabricar Ge pMOSFET en superficies orientadas (001) -, (011) - y (111). Después de la limpieza previa a la compuerta en solución diluida de HF (1:50), se depositó una capa de pasivación de Si amorfo ultrafino sobre sustratos de n-Ge mediante pulverización catódica con magnetrón a una potencia objetivo de 50 W. Tres duraciones de pasivación de 60 s, 80 sy 100 Se utilizaron s correspondientes a la deposición de 0,5, 0,7 y 0,9 nm t si , respectivamente. Después de eso, un HfO 2 de 5 nm de espesor El dieléctrico de la puerta se depositó a 250 ° C por deposición de capa atómica usando TDMAHf y H 2 O como precursores de Hf y O, respectivamente. Se depositó un electrodo de puerta de TaN de 50 nm mediante pulverización catódica reactiva. A continuación, se modeló y grabó el electrodo de puerta, seguido de BF 2 + implantación en regiones fuente / drenaje (S / D) a 30 KeV con una dosis de 1 × 10 15 cm - 2 . Se formaron metales S / D no autoalineados de níquel de 15 nm mediante un proceso de despegue. Finalmente, se llevó a cabo un recocido térmico rápido a 400 ° C para la activación del dopante y la metalización S / D. La Figura 1b muestra el esquema transversal del Ge pMOSFET con Si / SiO 2 capa interfacial (IL). La Figura 1c muestra una imagen de microscopio de vista superior de un Ge pMOSFET fabricado.

un Secuencia de proceso que muestra los pasos clave empleados para fabricar los Ge pMOSFET con diferentes t Si . b Esquema transversal de un Ge pMOSFET con SiO 2 ILLINOIS. c Imagen de microscopio de vista superior de un Ge pMOSFET

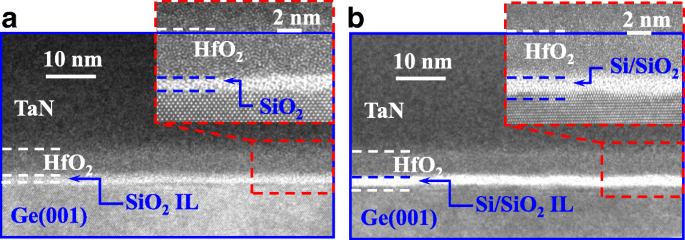

La Figura 2a, b muestra las imágenes del microscopio electrónico de transmisión (TEM) de la pila de puerta de metal / alto κ con SiO 2 / Si capa interfacial (IL) en canal Ge (001) con t Si de 0,5 y 0,9 nm, respectivamente. Los recuadros muestran las imágenes TEM (HRTEM) de alta resolución de las muestras. Para el dispositivo con una t Si de 0,5 nm, la capa de Si amorfo se oxidó por completo, mientras que para el dispositivo con 0,9 nm t Si , quedaron aproximadamente dos monocapas de Si después de los siguientes pasos de recocido.

Imágenes TEM transversales de pilas de compuertas Ge pMOSFET con a 0,5 nm t Si y b 0,9 nm t Si . Las imágenes HRTEM en recuadros muestran que Si / SiO 2 IL se forma entre HfO 2 y canal Ge

Resultados y discusión

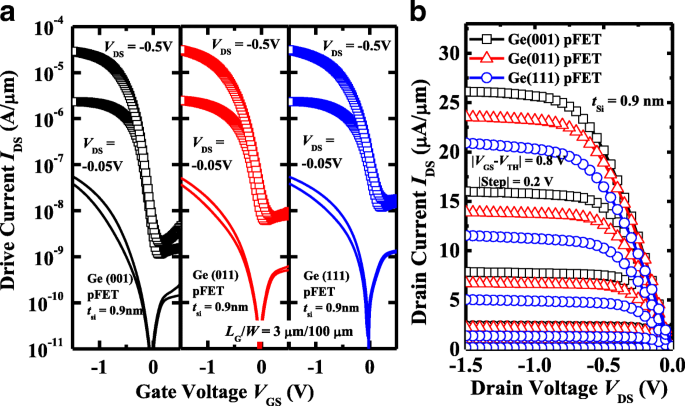

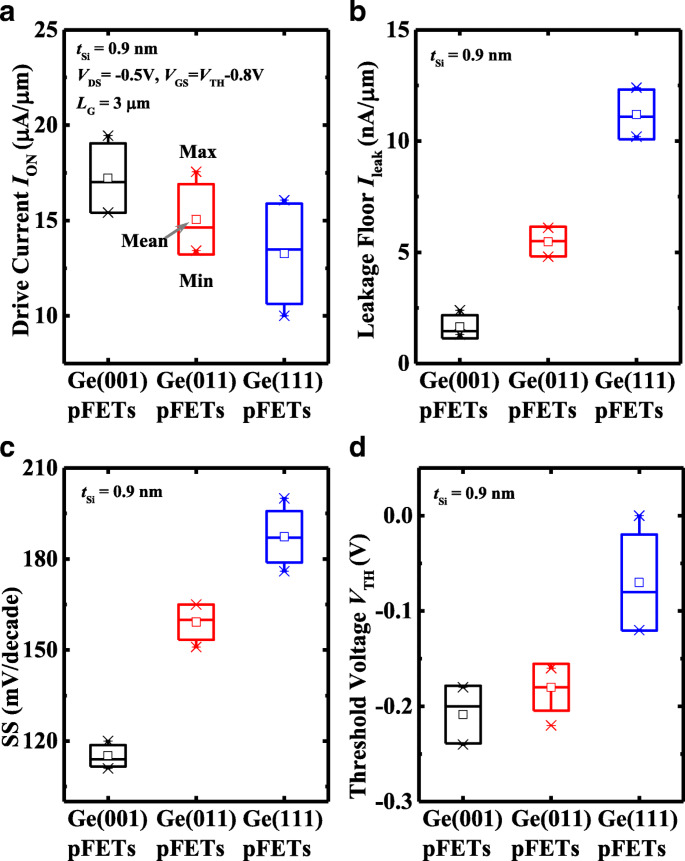

La Figura 3a traza el I medido DS - V GS y yo G - V GS curvas de los pMOSFET de Ge típicos en superficies orientadas (001) -, (011) - y (111) con 0,9 nm t Si , que muestran las excelentes características de transferencia. Todos los transistores tienen una longitud de puerta L G de 3 μm y un ancho de puerta W de 100 μm. La dirección del canal es [110] para todas las orientaciones. El yo DS - V DS curvas de los dispositivos medidos en diferentes compuertas overdrive V GS - V TH se muestran en la Fig. 3b. Aquí, voltaje de umbral V TH se define como la V GS en I DS de 10 −7 A / μm. Se observa que Ge (001) pMOSFET logra la mayor corriente de excitación I ACTIVADO en comparación con los transistores en las superficies (011) y (111) en el V fijo GS - V TH . Más adelante, mostraremos que esto se atribuye al hecho de que los pMOSFET de Ge (001) tienen una movilidad de agujero efectiva más alta μ ef en comparación con los dispositivos en las otras dos orientaciones de superficie. Realizamos una comparación completa del rendimiento eléctrico de los dispositivos con el t fijo Si de 0,9 nm, incluido I ACTIVADO , suelo de fugas I fuga , oscilación del subumbral (SS) y V TH caracteristicas. yo fuga se define como el mínimo I DS en V DS de - 0.05 V. La Figura 4a presenta el gráfico estadístico de la I ACTIVADO para Ge pMOSFET en varias orientaciones, y I ACTIVADO se definió como I DS en una V DS de - 0,5 V y una V GS - V TH de - 0.8 V. Todos los transistores en este gráfico tienen el L G de 3 μm y W de 100 μm. Los dispositivos orientados a (001) exhiben la media mejorada I ACTIVADO en comparación con los de las orientaciones (011) y (111), lo que se atribuye a la mayor μ ef . La figura 4b compara el I fuga para los dispositivos, lo que muestra que los transistores Ge (001) tienen el I más bajo fuga de ellos, y los pMOSFET Ge (011) tienen el I más bajo fuga que los dispositivos orientados a (111). Cabe señalar que el I fuga está determinada por la corriente inversa del p + / n unión en la región de drenaje, que se ve afectada por la concentración de dopaje de tipo n de fondo en el sustrato de Ge y la activación del p + implantado dopantes. Las concentraciones de dopaje de tipo n en las obleas con varias orientaciones no son exactamente las mismas. La orientación de la superficie afecta la velocidad de activación del dopante y la calidad de recristalización de las regiones S / D. Además, aunque el I G es menor que I DS antes del encendido de los transistores, influiría en el I fuga . De manera similar, los pMOSFET de Ge orientados a (001) demuestran las características SS mejoradas en comparación con otras dos orientaciones, lo cual se debe a que los transistores en la superficie (001) tienen la densidad de intervalo medio más baja del estado de interfaz D eso en comparación con los otros dispositivos. La Figura 4d muestra que los dispositivos en diferentes orientaciones tienen diferentes V TH . Con base en los resultados de la Fig.4, se concluye que, con la t fija Si de 0.9 nm, los pMOSFET de Ge orientados a (001) obtienen las mejores características eléctricas.

un Medido I DS - V GS y yo G - V GS curvas de pMOSFET de Ge orientados (001), (011) y (111) con t de 0,9 nm Si mostrando las excelentes características de transferencia. b yo DS - V DS curvas medidas a diferentes V GS - V TH para los dispositivos

Comparación de a yo ACTIVADO , b yo fuga , c SS y d V TH para los pMOSFET de Ge orientados a (001), (011) y (111) con una t Si de 0,9 nm

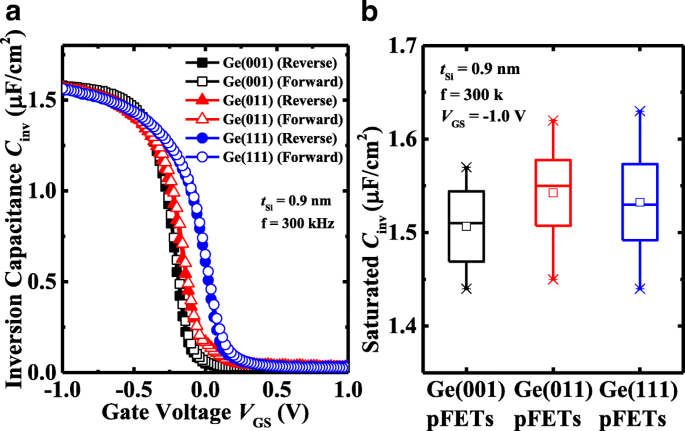

Los espesores de Si / SiO 2 IL en transistores con 0,9 nm t Si en diferentes orientaciones de superficie se estudian utilizando capacitancia de inversión C inv versus V GS medición, como se muestra en la Fig. 5. Las mediciones de barrido hacia adelante y hacia atrás exhiben una histéresis insignificante en los dispositivos. Los transistores exhiben la magnitud similar de C inv , ~ 1,56 μF / cm 2 , correspondiente al espesor efectivo capacitivo (CET) de 2,2 nm. La Figura 5b muestra los resultados estadísticos de C saturado inv para los dispositivos, que demuestran la pequeña diferencia en C inv en los transistores en diferentes orientaciones de superficie. Esto indica que la tasa de pasivación del Si amorfo por pulverización catódica con magnetrón es independiente de la orientación de la superficie. La regla de los cambios de izquierda a derecha de la C inv - V GS curvas es muy consistente con la de V TH para los dispositivos en la Fig. 4d, que podría ser inducida por la concentración de dopaje ligeramente diferente en diferentes sustratos de orientación.

un Comparación de inversión C inv - V GS curvas entre los Ge pMOSFET con 0,9 nm t Si en diferentes orientaciones. Se muestran barridos hacia adelante y hacia atrás. b Gráficos estadísticos para la C saturada inv de los dispositivos que muestran diferencias insignificantes en C inv en el régimen de inversión

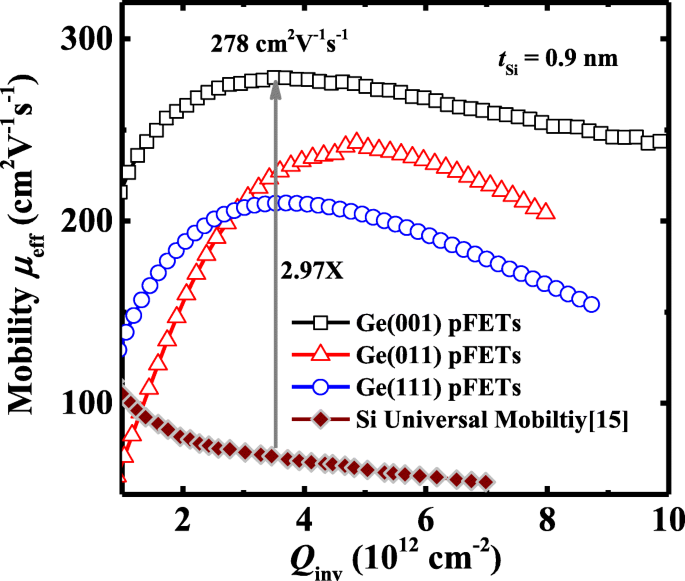

La Figura 6 compara las características de movilidad de los transistores con 0.9 nm t Si en varias orientaciones de superficie. El μ ef se extrajo utilizando un método basado en la pendiente de resistencia total [14]. Los pMOSFET de Ge (001) exhiben una movilidad de canal mucho mayor en comparación con los dispositivos en las orientaciones (011) y (111). Los transistores en el sustrato (001) alcanzan un pico μ ef de 278 cm 2 / V · s con una densidad de carga de inversión Q inv de ~ 3,5 × 10 12 cm −2 , que es 2,97 veces mayor que la movilidad universal de Si. Rugosidad de la superficie en la interfaz Si / Ge y densidad de los estados de la interfaz ( D eso ) puede afectar a μ ef de los dispositivos con una densidad de portadora de inversión alta. Es poco probable que las obleas Ge compradas comercialmente con varias orientaciones de superficie tengan la diferencia obvia en la rugosidad de la superficie. Por lo tanto, se especula que la mejora de la movilidad en los dispositivos orientados a (001) se debe principalmente a la reducción de la dispersión de portadora contribuida por los estados de la interfaz. En este trabajo, evaluamos la brecha media D eso de los dispositivos, y con el t fijo Si de 0,9 nm, los pMOSFET de Ge orientados a (001) tienen el espacio medio inferior D eso en comparación con las otras orientaciones.

Gráfico de μ ef versus Q inv para Ge pMOSFET con 0,9 nm t Si en sustratos orientados (001), (011) y (111). Los pMOSFET de Ge (001) logran una mejora de 2,97 veces en μ ef a una Q inv de 3,5 × 10 12 cm −2 en comparación con la movilidad universal Si. El μ ef se extrajo utilizando un método basado en la pendiente de resistencia total [17]

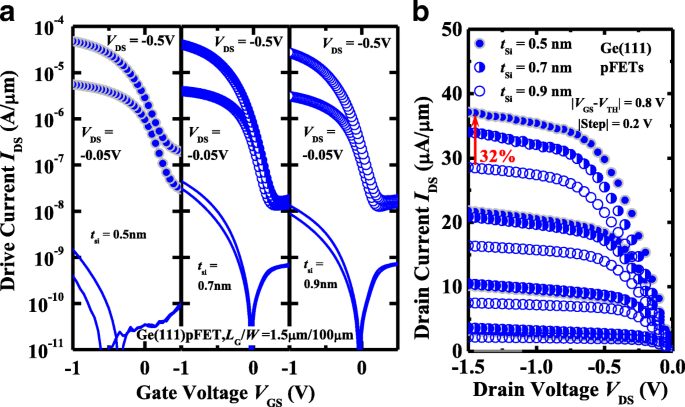

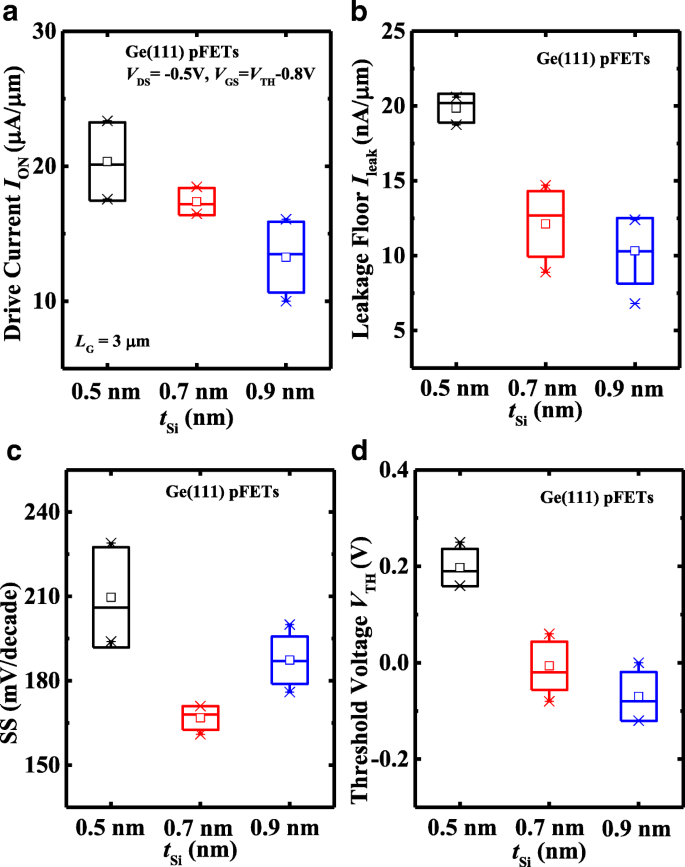

El impacto de t Si sobre el rendimiento eléctrico de los Ge pMOSFET también se investiga. Las figuras 7a, b presentan el I medido DS - V GS y yo DS - V DS curvas, respectivamente, de los pMOSFET de Ge orientados (111) con t Si de 0,5, 0,7 y 0,9 nm a V DS de - 0.05 y - 0.5 V. Los transistores tienen un L G de 1,5 μm. Se observa que Ge pMOSFET con 0.9 nm t Si exhiben características de transferencia mejoradas en comparación con los dispositivos con t más delgados Si , pero yo ACTIVADO del dispositivo disminuye con el aumento de t Si . En V DS de - 1,5 V y V GS - V TH de - 0.8 V, Ge (111) pMOSFET con 0.5 nm t Si demuestra una mejora del 32% en I ACTIVADO en comparación con el dispositivo con 0,9 nm t Si . La Figura 8 traza los resultados estadísticos de I ACTIVADO , yo fuga , SS y V TH de los Ge pMOSFET en (111) -orientación con diferentes t Si . De la Fig. 8a, vemos que los transistores con 0.5 nm t Si lograr el I mejorado ACTIVADO en comparación con los dispositivos con t más gruesa Si , que se debe al transistor con 0,5 nm t Si que tiene un CET más pequeño, lo que lleva a un C más alto inv . Se nota que yo fuga disminuye con el aumento de t Si (Fig. 8b) y transistores con 0,5 nm t Si tiene las características de SS inferiores a las de los dispositivos con capa de pasivación de Si amorfo de 0,7 y 0,9 nm (Fig. 8c). Esto podría deberse a los transistores con 0,5 nm t Si tener una brecha media más alta D eso . La relación entre SS y midgap D eso de Ge pMOSFET se puede expresar mediante SS =ln (10) ⋅ ( kT / q) ⋅ [1 + ( C eso + C d ) / C buey ], donde C buey , C d y C eso son capacitancia de óxido, capacitancia de capa de agotamiento y capacitancia de trampas de interfaz, respectivamente. C eso se puede calcular con q × D eso , eran D eso es la densidad de la trampa de la interfaz. Aunque el transistor con 0,5 nm t Si tiene la C más grande buey en comparación con los otros dos dispositivos, su intervalo medio superior D eso puede conducir a un SS inferior a los dispositivos con el t más grueso Si . La pasivación de la superficie también afectará al I fuga desde el desagüe hasta la fuente. Con el barrido de V GS de posición a negativo, el canal pasa del modo de acumulación al modo de inversión. Sin embargo, si el D eso es alto, algunos puntos en la superficie del canal están fijados por las trampas de interfaz y se pueden formar las rutas de fuga, aumentando I fuga desde el desagüe hasta la fuente. Como se muestra en la Fig. 8d, los pMOSFET de Ge (111) muestran el desplazamiento de V TH a V negativo GS dirección con el aumento de t Si , que se atribuye al aumento del AEC. Además, la densidad de trampas en la mitad inferior de la banda prohibida parece aumentar para la t más delgada Si , lo que podría provocar el cambio de V TH [2].

un yo DS - V GS y yo G - V GS y b yo DS - V DS curvas de Ge (111) pMOSFET con varios t Si . Transistor con 0,5 nm t Si muestra una mejora del 32% en I ACTIVADO en comparación con el dispositivo con 0,9 nm t Si en V DS de - 1,5 V y V GS - V TH de - 0,8 V

Comparación de a yo ACTIVADO , b yo fuga , c SS y d V TH para pMOSFET Ge orientados (111) con 0,5, 0,7 y 0,9 nm t Si mostrando que los transistores con 0.5 nm t Si tengo el mejor yo ACTIVADO , pero peor SS y I fuga características en comparación con dispositivos con t más grueso Si

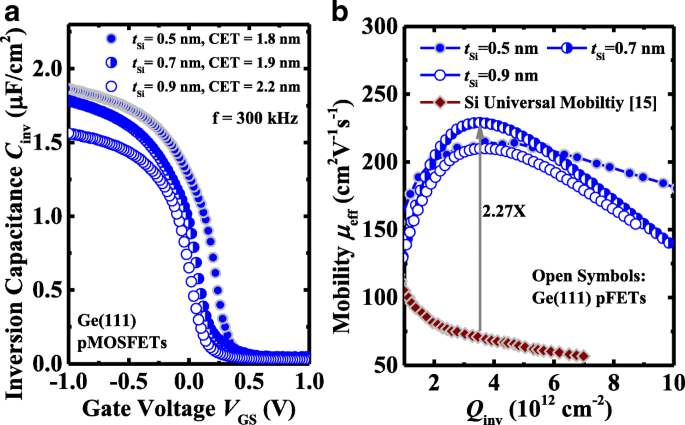

La figura 9a muestra la C inv en función de V GS curvas para los Ge pMOSFET en la superficie orientada (111) con t Si de 0,5, 0,7 y 0,9 nm medidos a una frecuencia de 300 kHz. Los valores CET en las regiones de inversión se extraen para que sean 1.8, 1.9 y 2.2 nm para los dispositivos con 0.5, 0.7 y 0.9 nm t si , respectivamente. μ ef en función de Q inv Las características de los dispositivos se extraen y se muestran en la Fig. 9b. El Ge pMOSFET orientado a (111) con 0,7 nm t si logra la máxima movilidad máxima de 229 cm 2 / V s, que es 2,27 veces mayor en comparación con la movilidad universal Si. Cabe señalar que los dispositivos con 0,5 nm t Si exhiben una μ significativamente mejorada ef sobre los transistores con una t más gruesa Si a un Q alto inv (p. ej., 10 13 cm −2 ). Esto también conduce a un I más alto ACTIVADO en alto V GS - V TH en los dispositivos con 0,5 nm t Si en comparación con los dispositivos con 0,7 y 0,9 nm t Si . El μ ef a un Q alto inv disminuye como t Si aumenta de 0,5 nm a 0,7 ~ 0,9 nm, lo que se atribuye al hecho de que la mayor rugosidad de la superficie conduce a una mayor dispersión de la rugosidad de la superficie de los portadores. Durante la pasivación de la superficie de Ge mediante la pulverización catódica con magnetrón a temperatura ambiente, la difusión de los átomos de la superficie se suprime en gran medida. Entonces, con el aumento de t Si , la rugosidad de la superficie es mayor, lo que se puede observar en las imágenes HRTEM de la Fig. 2.

un C inv - V G características medidas a 300 kHz para dispositivos orientados a (111) con 0,5, 0,7 y 0,9 nm t Si . b μ ef en función de Q inv para Ge pMOSFETs [17]

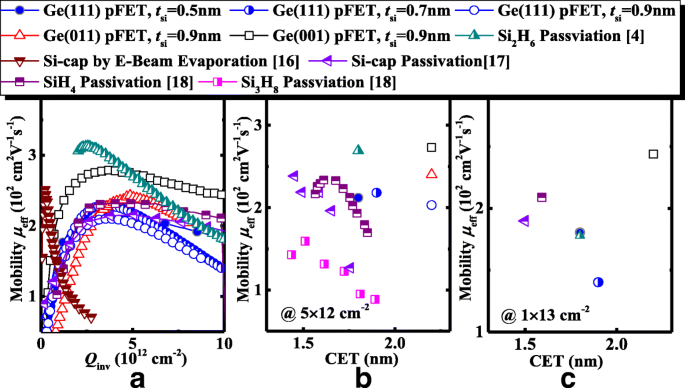

En la Fig. 10, comparamos el μ ef de los Ge pMOSFET en este trabajo con los de los transistores Ge relajados reportados con Si por evaporación de haz E, SiH 4 , Si 2 H 6, y Si 3 H 8 pasivación. En comparación con el Si amorfo por evaporación por haz E en la Ref. [15], los pMOSFET de Ge en este trabajo exhiben la mejora significativa de μ ef . Se ve que, en el CET similar, los pMOSFET de Ge que utilizan pasivación de Si amorfo por pulverización catódica con magnetrón tienen μ más bajos ef en comparación con los dispositivos con Si 2 H 6 pasivación. El proceso de pasivación con Si amorfo debe optimizarse aún más para mejorar la movilidad del portador.

un μ ef para los Ge pMOSFET en este trabajo frente a los resultados publicados para los Ge pMOSFET relajados. b , c Evaluación comparativa de μ ef extraído en Q inv =5 × 10 12 y 1 × 10 13 cm −2 , respectivamente, de los Ge pMOSFET con los diferentes valores CET [18, 19]

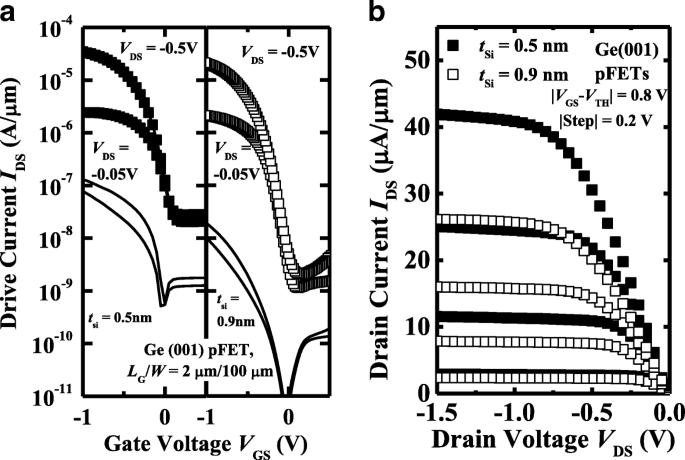

Ge pMOSFET con las diferentes t Si en la superficie orientada (001) también se caracterizan. Las figuras 11a, b ilustran el I medido DS - V GS y yo DS - V DS curvas, respectivamente, de un par de pMOSFET Ge (001) con 0,5 y 0,9 nm t Si . Similar a los dispositivos orientados (111), Ge (001) pMOSFET con 0.5 nm t Si obtiene la mejora en I ACTIVADO pero la degradación en I fuga en comparación con el transistor con 0,9 nm t Si .

un Medido I DS - V GS y yo G - V GS curvas de Ge pMOSFET orientados a (001) con 0,5 y 0,9 nm t Si . b yo DS - V GS curvas de los dispositivos

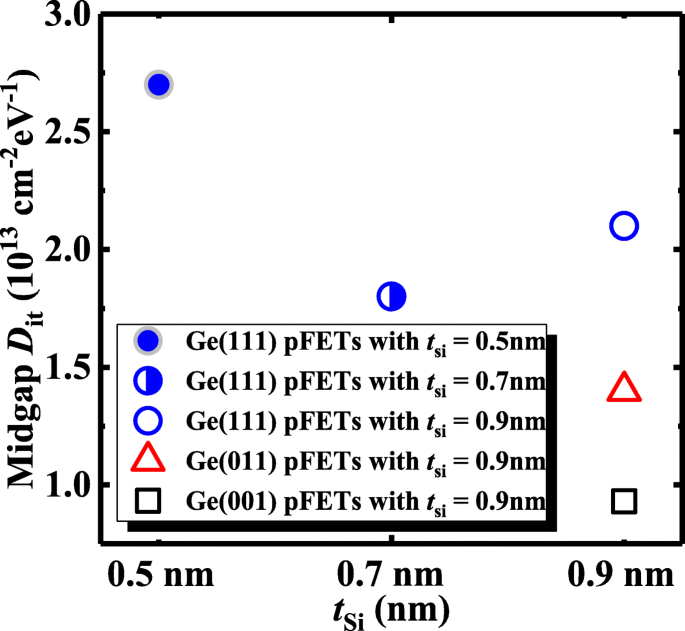

La brecha intermedia D eso Las características de los Ge pMOSFET se estudian mediante el método de [16], y los valores de D eso son calculados por D eso =[SSlog (e) / ( kT / q ) - 1] C G / q , [16] donde q es la carga del electrón, k es la constante de Boltzmann, T es la temperatura absoluta y C G es la capacitancia medida de la puerta por unidad de área. La figura 12 muestra D eso en función del espesor del Si amorfo con varias orientaciones superficiales de Ge. Para una superficie orientada (111), un dispositivo con 0,7 nm t si tiene la D más baja eso valor. Con el t de 0,9 nm Si , El dispositivo orientado a (001) tiene la D inferior eso en comparación con los transistores en otras orientaciones.

D eso versus el espesor de Si amorfo con varias orientaciones de superficie de Ge

Finalmente, comparamos las características eléctricas clave de los Ge pMOSFET en las diferentes orientaciones en la Tabla 1. Con una t fija Si , Ge (001) pMOSFET tiene un rendimiento eléctrico mejorado en comparación con las otras dos orientaciones. La corriente de la unidad se puede mejorar reduciendo el t Si de 0,9 nm a 0,5 nm, lo que se debe a que el t más delgado Si proporciona un CET significativamente reducido sin causar degradación en μ ef .

Conclusiones

El pMOSFET de Ge pasivado por Si amorfo se demuestra en el sustrato orientado (001) -, (011) - y (111). Con una t Si de 0,9 nm, la I mejorada ACTIVADO y las características SS se obtienen en los pMOSFET Ge orientados (001) en comparación con los dispositivos en las orientaciones (011) y (111), debido a la mayor μ ef y espacio medio inferior D eso . Ge (001) pMOSFET con 0,9 nm t Si lograr una movilidad máxima de 278 cm 2 / V s en una Q inv de 3,5 × 10 12 cm −2 , que es 2,97 veces mayor que la movilidad universal de Si. Está demostrado que I ACTIVADO de los dispositivos se mejora con la disminución de t Si debido a la reducción de CET. Pero Ge pMOSFET con t más grueso Si exhiben el piso superior de oscilación y fugas por debajo del umbral, debido a ese espacio intermedio D eso se puede reducir aumentando t Si .

Abreviaturas

- ALD:

-

Deposición de la capa atómica

- BF 2 + :

-

Ión de fluoruro de boro

- CET:

-

Espesor efectivo capacitivo

- Ge:

-

Germanio

- GeO x :

-

Óxido de germanio

- HF:

-

Ácido fluorhídrico

- HfO 2 :

-

Dióxido de hafnio

- HRTEM:

-

Microscopio electrónico de transmisión de alta resolución

- IL:

-

Capa interfacial

- MOSFET:

-

Transistores de efecto de campo semiconductores de óxido metálico

- Ni:

-

Níquel

- Si:

-

Silicio

- SS:

-

Oscilación del subumbral

- TaN:

-

Nitruro de tantalio

- TDMAHf:

-

Tetrakis (dimetilamido) hafnio

Nanomateriales

- KUHMUTE rediseña la movilidad con la impresión 3D SLS

- Impresión 3D de alta velocidad con AFPM

- Impresión 3D de alta velocidad con AION500MK3

- Alto rendimiento de PEDOT:células solares PSS / n-Si basadas en una superficie texturizada con electrodos AgNWs

- Convertidor de polarización con birrefringencia controlable basado en metauperficie híbrida de grafeno totalmente dieléctrico

- Célula solar híbrida de silicio nanoestructurado orgánico de alto rendimiento con estructura de superficie modificada

- Una referencia de voltaje sin resistencia de baja potencia a nanoescala con PSRR alto

- Nanohojas porosas de ZnO con modificación parcial de la superficie para una separación de cargas mejorada y una alta actividad fotocatalítica bajo irradiación solar

- Ge pMOSFET con pasivación GeOx formada por ozono y posoxidación del plasma

- Nuevos conocimientos sobre los factores que limitan el transporte del portador en películas de In2O3 muy delgadas amorfas dopadas con Sn con alta movilidad de pasillo

- Ge pMOSFET de alta movilidad con dieléctrico de ZrO2:impactos del recocido posterior