Ge MOSFET de canal N con dieléctrico ZrO2 Logrando una movilidad mejorada

Resumen

Ge nMOSFET de alta movilidad con ZrO 2 El dieléctrico de la puerta se demuestra y se compara con transistores con diferentes propiedades interfaciales del ozono (O 3 ) tratamiento, O 3 postratamiento y sin O 3 tratamiento. Se encuentra que con O 3 tratamiento, los Ge nMOSFET con ZrO 2 dieléctrico que tiene un EOT de 0,83 nm obtiene una movilidad de electrones efectiva máxima ( μ ef ) de 682 cm 2 / Vs, que es más alta que la de la movilidad universal de Si a la densidad de carga de inversión media ( Q inv ). Por otro lado, el O 3 postratamiento con Al 2 O 3 La capa interfacial puede proporcionar μ dramáticamente mejorada ef , logrando aproximadamente un 50% de μ ef mejora en comparación con la movilidad universal de Si en Q medio inv de 5 × 10 12 cm −2 . Estos resultados indican la posible utilización de ZrO 2 dieléctrico en Ge nMOSFET de alto rendimiento.

Antecedentes

GERMANIUM (Ge) ha mostrado ventajas de mayor movilidad del portador y menor temperatura de procesamiento en comparación con los dispositivos de Si. Estos hacen que Ge sea una alternativa para aplicaciones de dispositivos lógicos CMOS ultraescalados y transistores de película delgada (TFT) como capa superior en circuitos integrados tridimensionales [1, 2, 3]. En los últimos años, se han centrado grandes esfuerzos en la pasivación de la superficie, el dieléctrico de la puerta y la ingeniería de canales para los transistores de efecto de campo (MOSFET) de semiconductores de óxido metálico de canal p de Ge, que han contribuido a una mejora significativa en el rendimiento eléctrico de los dispositivos de canal p.

Pero para los MOSFET de canal n de Ge, la movilidad de portadora efectiva baja ( μ ef ) causado por una capa interfacial deficiente de la pila de puertas limita en gran medida el rendimiento de los dispositivos. Varias técnicas de pasivación de superficie, incluida la pasivación de Si [1], la posoxidación del plasma [4] y la pasivación de InAlP [5] y varios dieléctricos de alto κ, incluido el HfO 2 , ZrO 2 [6,7,8], Y 2 O 3 [9] y La 2 O 3 [10] se han explorado en Ge nMOSFET para impulsar el electrón μ ef . Se demostró que ZrO 2 dieléctrico integrado con canal de Ge puede proporcionar una interfaz robusta debido a que un GeO 2 La capa interfacial puede reaccionar y entremezclarse con el ZrO 2 capa [7]. Un agujero decente μ ef se ha informado en transistores de canal p Ge [6,7,8], mientras que todavía hay mucho margen de mejora en μ de electrones ef para sus homólogos.

En este trabajo, Ge nMOSFET con ZrO 2 los dieléctricos de la puerta se fabrican para lograr una μ mejorada ef sobre Si en todo el rango de densidad de carga de inversión ( Q inv ). Los transistores Ge obtienen una mejora del 50% en electrones μ ef en comparación con la movilidad universal de Si a un Q medio inv de 5.0 × 10 12 cm −2 .

Experimental

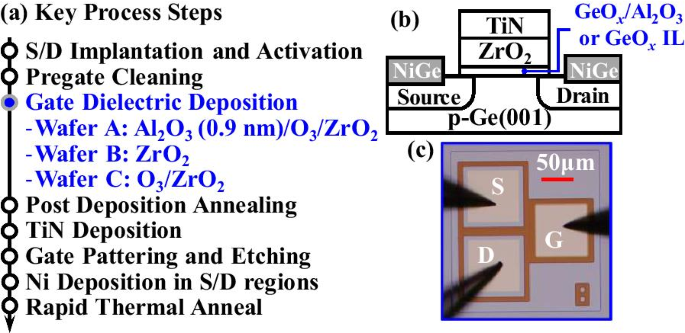

Los pasos clave del proceso para fabricar Ge nMOSFET en obleas p-Ge (001) de 4 pulgadas con una resistividad de 0.136–0.182 Ω cm se muestran en la Fig. 1a. Las regiones de fuente / drenaje (S / D) se implantaron con iones de fósforo a una dosis de 1 × 10 15 cm −2 y una energía de 30 keV seguida de un recocido de activación dopante a 600 ° C. Después de la limpieza previa a la puerta, las obleas de Ge se cargaron en una cámara de deposición de capa atómica para la formación de la (s) capa (s) dieléctrica de la puerta:Al 2 O 3 / O 3 oxidación / ZrO 2 , ZrO 2 , o O 3 oxidación / ZrO 2 para las obleas A, B o C, respectivamente. Para la oblea A, 0.9 nm Al 2 O 3 se utilizó para proteger la superficie del canal durante O 3 oxidación. O 3 La oxidación se llevó a cabo a 300 ° C durante 15 min para las obleas A y C. Para todas las obleas, el espesor de ZrO 2 fue ~ 3,3 nm. Posteriormente, se depositó metal de puerta de TiN (100 nm) mediante pulverización catódica reactiva física, y se utilizaron patrones de litografía y grabado con iones reactivos para formar el electrodo de puerta. Después de eso, se depositó una capa de Ni de 25 nm de espesor en las regiones S / D. Finalmente, se llevó a cabo el recocido posterior a la metalización (PMA) a 350 ° C durante 30 s para formar el germanuro de Ni y mejorar la calidad de la interfase. Las imágenes esquemáticas y de microscopio del transistor fabricado se muestran en las Fig. 1b, c, respectivamente.

un Pasos clave del proceso para fabricar Ge nMOSFET. b Esquema transversal y c imagen de microscopio de los dispositivos fabricados

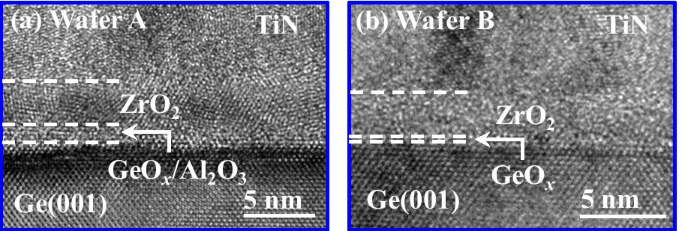

La Figura 2a, b muestra las imágenes de microscopio electrónico de transmisión de alta resolución (HRTEM) de las pilas de puertas en las obleas A y B, respectivamente. El espesor unificado del Al 2 O 3 / GeO x La capa interfacial (IL) para la oblea A es de ~ 1,2 nm, lo que indica la GeO de 0,2 a 0,3 nm x . Para el dispositivo en la oblea B, un GeO ultradelgado x IL se demostró experimentalmente [7].

Imágenes HRTEM de a TiN // ZrO 2 / Al 2 O 3 / GeO x / Ge, b TiN / ZrO 2 / GeO x / Ge pilas para los dispositivos en las obleas A y B, respectivamente

Resultados y discusión

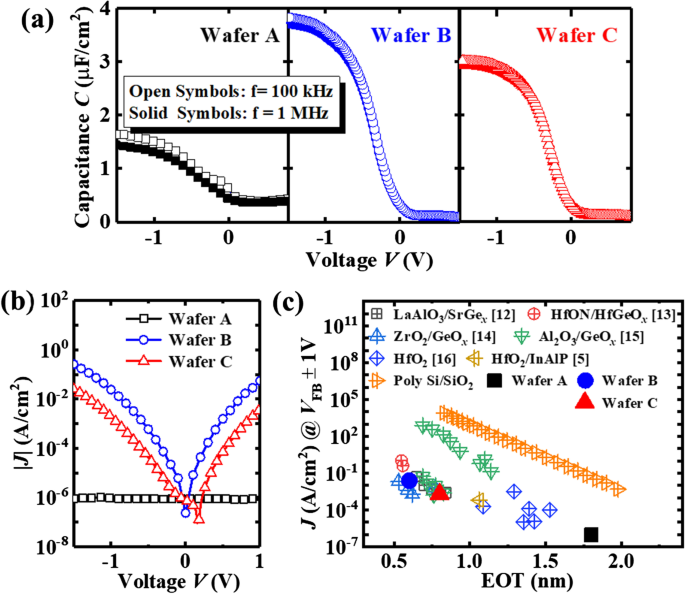

La capacitancia medida ( C ) y la corriente de fuga ( J ) Las características de los condensadores Ge MOS en las obleas A, B y C se miden y se muestran en la Fig. 3a, b, respectivamente. El espesor de óxido equivalente (EOT) de los dispositivos en las obleas A, B y C se extrae para que sea de 1,79, 0,59 y 0,83 nm, respectivamente. Asumiendo el GeO x IL proporciona un EOT adicional de ~ 0.25 nm para las obleas A y C al comparar las obleas B y C, el ZrO 2 de 3.3 nm aporta un EOT de ~ 0,6 nm con un valor de κ de ~ 21,8, que es coherente con el valor informado anteriormente de ZrO 2 amorfo [11]. Estos resultados derivados también confirman que el espesor en GeO x IL en la oblea B es insignificante.

un Medido C en función del voltaje V características de los condensadores Ge pMOS en las obleas A, B y C. b J versus V curvas para los dispositivos. c Evaluación comparativa de J (extraído en V FB ± 1 V) de los condensadores Ge MOS en este trabajo contra datos obtenidos para condiciones de polarización similares de la literatura

El GeO x / Al 2 O 3 IL para la oblea A y GeO x IL para la oblea C produce el EOT de ~ 1,2 y ~ 0,25 nm, respectivamente. El EOT de los dispositivos se puede reducir aún más disminuyendo el grosor de IL o mejorando la calidad de la interfaz y mejorando la permitividad de ZrO 2 con algo de pasivación superficial, por ejemplo, NH 3 / H 2 tratamiento con plasma [6]. La figura 3c compara J frente a las características de EOT para los nMOSFET de Ge en este trabajo frente a los valores de otros dispositivos de Ge reportados [5, 12,13,14,15,16,17]. También se observa que los resultados son consistentes con el Ge MOS informado con EOT ultradelgado siguiendo las mismas tendencias, lo que indica que la diferencia de corriente de fuga mostrada en la Fig. 3b debe atribuirse principalmente a la diferencia de EOT.

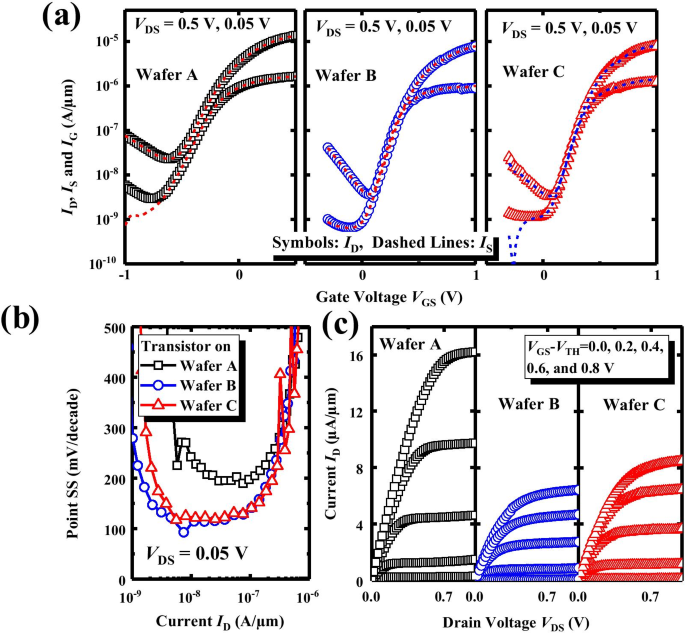

La Figura 4a muestra la corriente de drenaje medida ( I D ) y la fuente actual ( I S ) versus voltaje de puerta ( V G ) curvas de Ge nMOSFET de las obleas A, B y C. Todos los transistores tienen una longitud de compuerta L G de 4 μm y un ancho de puerta W de 100 μm. El punto de oscilación del subumbral (SS), definido como d V G / d (log I D ), en función de I D Las curvas de los transistores de la Fig. 4a se calculan y se muestran en la Fig. 4b. Se aclara que el transistor en la oblea A exhibe el I degradado D piso de fuga y SS en comparación con los dispositivos en las obleas B y C. Además del aumento de EOT en los dispositivos en la oblea A traería el incremento de SS, estos fenómenos deberían atribuirse en parte al hecho de que el dispositivo con el Al 2 O 3 La capa insertada tiene una mayor densidad de trampas de interfaz ( D eso ) dentro de la banda prohibida del canal Ge en comparación con las obleas B y C.

un Medido I D y yo S versus V GS curvas de Ge nMOSFET en las obleas A, B y C. b Punto SS en función de I D para los transistores. c yo D - V D Las características muestran que el Ge nMOSFET en la oblea A tiene una corriente de excitación más alta en comparación con los dispositivos en las obleas B y C

La Figura 4c muestra las características de salida medidas, es decir, I D - V D curvas para varios valores de sobremarcha de puerta | V G - V TH | de los dispositivos que demuestran que el transistor Ge en la oblea A logra una corriente de excitación significativamente mejorada en comparación con los dispositivos en las obleas B y C. Aquí, V TH se define como V GS correspondiente a un I D de 10 −7 A / μm. Teniendo en cuenta las condiciones idénticas para la formación de S / D, el I impulsado DS para transistores en la oblea A indica el mayor μ ef [18,19,20,21]. El Al 2 O 3 capa no ha llevado a la degradación de D eso rendimiento cerca de la banda de conducción del canal Ge.

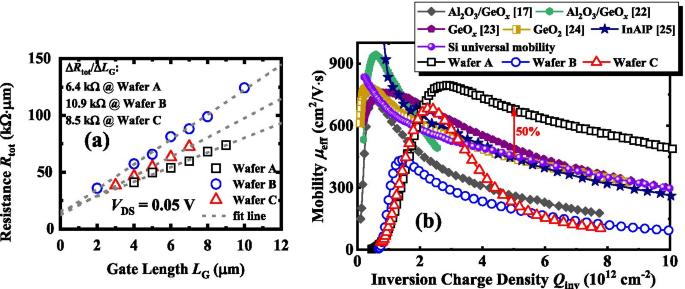

La figura 5a muestra la resistencia total R tot en función de L G para los Ge nMOSFET con ZrO 2 dieléctrico con una L G que van de 2 a 10 µm. Los valores de R tot se extraen en una sobremarcha de puerta de 0. 6 V y una V D de 0,05 V. La resistencia S / D R SD de los transistores se extrae para que sea ~ 13,5 kΩ μm, utilizando las líneas ajustadas que se cruzan en el y -eje. El R similar SD es consistente con el proceso idéntico de formación de PMA y S / D. La resistencia del canal R CH Los valores de los dispositivos se obtienen por la pendiente de las líneas ajustadas, es decir, Δ R tot / Δ L G , que se puede utilizar para calcular el μ ef características de los Ge nMOSFET. Para evaluar la calidad de la interfaz, las densidades de trampa de interfaz ( D eso ) se extrajeron mediante la siguiente ecuación de acuerdo con el método de Hill [17]:

$$ D _ {{{\ text {it}}}} =\ frac {{2G _ {{{\ text {m}} \ max}} / \ omega}} {{qA \ left [{\ left ({\ frac {{G _ {{{\ text {mmax}}}}}} {{\ omega C _ {{{\ text {ox}}}}}}} \ right) + \ left ({1 - C _ {{\ text {m}}} / C _ {{{\ text {ox}}}}} \ right) ^ {2}} \ right]}} $$donde q es la carga electrónica, A es el área del condensador, G m, máximo es el valor máximo de conductancia medida, con su correspondiente capacitancia C m , ω es la frecuencia angular y C buey es la capacitancia de óxido de puerta. La D eso los valores se calculan en 3,7, 3,2 y 2,3 × 10 12 eV −1 cm −2 para los dispositivos de las obleas A, B y C, respectivamente.

Se sabe que los valores calculados corresponden a la brecha media D eso . El dispositivo con Al 2 O 3 IL en la oblea A tiene un espacio medio más alto D eso en comparación con los dispositivos de las obleas B y C. Esto es coherente con los resultados de las Figs. 3a y 4a, y la brecha media superior D eso da lugar a una mayor dispersión de la capacitancia de agotamiento en la oblea A, lo que provoca una mayor corriente de fuga de I DS en comparación con las otras dos obleas. Tenga en cuenta que la oblea A debe tener la D inferior eso cerca de la banda prohibida de conducción debido a su mayor μ ef sobre las obleas B y C.

un R tot versus L G curvas para Ge nMOSFET en las obleas A, B y C. La línea ajustada que se cruza en el eje y y la pendiente de las líneas de ajuste lineal se utilizan para extraer el R SD y R CH , respectivamente. b μ ef para los nMOSFET de Ge de este trabajo frente a los resultados publicados anteriormente para los transistores de Ge sin tensión. Los dispositivos en la oblea A muestran la μ mejorada ef que la movilidad universal de Si en toda la gama de Q inv

Es bien sabido que μ ef es el cuello de botella para la alta corriente de excitación y transconductancia en Ge nMOSFET. Aquí, μ ef se puede calcular mediante \ (\ mu _ {{{\ text {eff}}}} =1 / [WQ _ {{{\ text {inv}}}} (\ Delta R _ {{{\ text {tot}}}} / \ Delta L _ {{\ text {G}}})] \), donde Δ R tot / Δ L G es la pendiente de la R tot versus L G como se muestra en la Fig. 5a. Q inv se puede obtener integrando el C medido inv - V G curvas. En la Fig. 5b, comparamos el μ ef versus Q inv de los nMOSFET de Ge en las obleas A, B y C con los informados anteriormente en [18, 22,23,24,25]. El pico extraído μ ef los valores de los transistores en las obleas A y C son 795 y 682 cm 2 / V s, respectivamente, y el de Ge nMOSFET en la oblea B es 433 cm 2 / V s. Ge nMOSFET con Al 2 O 3 IL logra un μ significativamente mejorado ef en comparación con los transistores en la oblea B o C, los dispositivos en [18, 22,23,24,25] en un campo alto, y la movilidad universal de Si en todo el Q inv rango. En una Q inv de 5 × 10 12 cm −2 , un 50% μ ef la mejora se logra en dispositivos en la oblea A en comparación con la movilidad universal Si. Esto demuestra que al proteger la superficie del canal para evitar la mezcla de ZrO 2 y GeO x usando Al 2 O 3 , se realiza una interfaz de alta calidad entre el aislador de la puerta y Ge para aumentar las características de movilidad, lo que también se informó en los estudios anteriores de MOSFET Ge con EOT ultradelgado [26]. μ ef en transistores en la oblea C es más alto que el universal Si en un Q inv de 2,5 × 10 12 cm −2 , aunque decae rápidamente con el aumento de Q inv rango. Esto indica que el O 3 usado oxidación antes de ZrO 2 la deposición mejoraría la calidad interfacial hasta cierto punto; sin embargo, no produce suficiente superficie de canal plana para suprimir eficazmente la dispersión de la rugosidad de la superficie del portador a un Q alto inv debido a la mezcla de ZrO 2 y GeO x , ya que se informa que la generación de vacantes de oxígeno durante el entremezclado aumentaría la rugosidad de orden de corto alcance (SRO) [27]. Optimización del O 3 proceso de oxidación o reducción del Al 2 O 3 El grosor de IL puede hacer que el transistor Ge logre un EOT reducido mientras mantiene un μ más alto ef en el alto Q inv .

Conclusiones

Se investigan los impactos de la morfología y la estructura dieléctrica de la puerta en las características eléctricas de Ge nMOSFET. Un Al 2 O 3 / ZrO 2 el dieléctrico de la puerta proporciona una μ significativamente mejorada ef en comparación con la movilidad universal Si. μ ef se puede mejorar insertando un Al 2 O 3 capa entre el ZrO 2 y el canal Ge, que, sin embargo, conduce inevitablemente a un EOT más grande. Al 2 O 3 -MOSFET de Ge gratis con O 3 oxidación de la superficie de Ge antes de ZrO 2 la deposición alcanza un pico μ ef de 682 cm 2 / V s que es más alto que el de Si en el Q similar inv .

Disponibilidad de datos y materiales

Los conjuntos de datos que respaldan las conclusiones de este artículo se incluyen en el artículo.

Abreviaturas

- Ge:

-

Germanio

- ZrO 2 :

-

Dióxido de circonio

- Al 2 O 3 :

-

Óxido de aluminio

- O 3 :

-

Ozono

- Si:

-

Silicio

- PMA:

-

Recocido post-metal

- PDA:

-

Recocido posterior a la deposición

- IL:

-

Capa interfacial

- TiN:

-

Nitruro de titanio

- MOSFET:

-

Transistores de efecto de campo semiconductores de óxido metálico

- ALD:

-

Deposición de la capa atómica

- HF:

-

Ácido fluorhídrico

- µ ef :

-

Movilidad eficaz del transportista

- PPO:

-

Post-oxidación del plasma

- SS:

-

Oscilación del subumbral

- CET:

-

Espesor equivalente a capacitancia

- EOT:

-

Espesor de óxido equivalente

- Qinv:

-

Densidad de carga de inversión

- HRTEM:

-

Microscopio electrónico de transmisión de alta resolución

- Ni:

-

Níquel

- GeO x :

-

Óxido de germanio

- I DS :

-

Drenar corriente

- V GS :

-

Voltaje de puerta

- V TH :

-

Voltaje umbral

Nanomateriales

- Lograr la sostenibilidad con tintes y pigmentos

- KUHMUTE rediseña la movilidad con la impresión 3D SLS

- Control completo de polarización de terahercios con ancho de banda ampliado a través de metauperficies dieléctricas

- Memoria resistiva ZrO2 / ZrO2 - x / ZrO2 sin cumplimiento con comportamiento de conmutación multiestado interfacial controlable

- Mecanismo de conducción y resistencia mejorada en RRAM basado en HfO2 con tratamiento de nitruración

- Mejora dieléctrica de capacitores MIM de Al2O3 / ZrO2 / Al2O3 depositados en capas atómicas mediante recocido por microondas

- Ge pMOSFET de alta movilidad con pasivación de Si amorfo:impacto de la orientación de la superficie

- Transistores de película fina a-InGaZnO de alto rendimiento con un presupuesto térmico extremadamente bajo mediante el uso de un dieléctrico de Al2O3 rico en hidrógeno

- 6 maneras en las que mejoramos Protocase Designer con la versión 4.6

- Cómo lograr un acabado fenomenal con metalización

- Resistencia al desgaste mejorada con electrodos de tungsteno de cobre