Un estudio sobre el efecto de los parámetros estructurales y el mecanismo interno de un transistor de efecto de campo de túnel bidireccional simétrico e intercambiable S / D controlado por compuerta bilateral

Resumen

En este artículo se propone un transistor de efecto de campo de túnel bidireccional S / D simétrico e intercambiable S / D bilateral controlado por puerta (B-TFET), que muestra la ventaja de las características de conmutación bidireccional y la compatibilidad con circuitos integrados CMOS en comparación con el TFET asimétrico convencional. Los efectos de los parámetros estructurales, por ejemplo, las concentraciones de dopaje de N + región y P + región, longitud de N + región y longitud de la región intrínseca, en el rendimiento del dispositivo, por ejemplo, las características de transferencia, I en - yo desactivado relación y oscilación subumbral, y el mecanismo interno se discuten y explican en detalle.

Introducción

El consumo de energía es uno de los principales problemas de la industria de los circuitos integrados. Si un dispositivo funciona en estado encendido, su corriente de conducción debe alcanzar un cierto valor crítico; cuando la corriente alcanza un valor crítico, la tensión de puerta correspondiente se define como la tensión de umbral. Cuando el dispositivo está en el estado apagado, el voltaje de la puerta correspondiente debe tener un valor diferente al del estado de encendido crítico, que a menudo se denomina voltaje de estado apagado. El concepto de oscilación de subumbral (SS) es aplicable al dispositivo que opera entre el estado apagado y el estado crítico encendido, que es igual al cambio en el voltaje de la puerta cuando la corriente aumenta en un orden de magnitud. Cuando el dispositivo está bien diseñado, se han determinado el valor crítico de corriente en estado activado, el voltaje umbral y el voltaje en estado desactivado del dispositivo; luego, un SS más pequeño corresponde a cambios de corriente más fuertes en el área del subumbral, una corriente estática más pequeña del dispositivo en el estado apagado y un menor consumo de energía estática del dispositivo. El SS de los transistores de efecto de campo semiconductores de óxido metálico (MOSFET), que son las celdas unitarias básicas ampliamente utilizadas en los circuitos integrados, está limitado por el mecanismo físico de la corriente generada mientras el dispositivo está funcionando y no puede ser inferior al valor límite de 60 mV / dec. Para superar esta limitación, en los últimos años se ha propuesto un transistor de efecto de campo de túnel (PIN o NIP TFET) basado en tecnología basada en silicio. Un TFET convencional se forma agregando una capa de semiconductores intrínsecos de bajo dopaje entre p - y n -materiales semiconductores de tipo. Comparado con MOSFET, el TFET tiene las ventajas de alta sensibilidad y bajo consumo de energía estática [1]. TFET se conmuta modulando el túnel cuántico a través de una barrera en lugar de modular la emisión termoiónica sobre una barrera como en el MOSFET tradicional. Por lo tanto, TFET no está limitado por la cola térmica de los portadores Maxwell-Boltzmann, que limita la SS del MOSFET a 60 mV / dec a temperatura ambiente [2] (exactamente 63 mV / dec a 300 K). El concepto fue propuesto por Chang et al. mientras trabajaba en IBM [3]. Por primera vez, Joerg Appenzeller y sus colegas de IBM demostraron que la SS de TFET podría ser inferior a 60 mV / dec. TFET se puede utilizar como interruptores electrónicos energéticamente eficientes [4], lo que rompe el cuello de botella de los MOSFET y reduce en gran medida el consumo de energía del IC. El proceso de producción es compatible con MOSFET. Es probable que reemplace al transistor MOSFET como la unidad básica de los circuitos integrados de próxima generación. Por lo tanto, los TFET se han convertido en un tema candente en los últimos años [5, 6]. Para mejorar el rendimiento de los TFET en términos de SS, corriente de conducción directa y fuga inversa, se han realizado muchos estudios sobre el diseño de la estructura y la optimización de los dispositivos TFET, que se centran principalmente en mejorar la forma de la estructura del canal del dispositivo y el electrodo de puerta [7 , 8,9,10,11,12] y los materiales dieléctricos de la puerta con diferentes funciones de trabajo. Se ha realizado el análisis característico y la optimización de la estructura del material dieléctrico de la puerta [13,14,15] y los dieléctricos de la puerta con diferentes constantes dieléctricas [15,16,17,18,19,20]. En física de dispositivos, el modelado analítico de TFET con estructura de doble puerta [21,22,23,24,25,26,27] y estructura de puerta circundante [28,29,30,31,32,33] también ha se ha realizado extensamente. Una desventaja de los TFET basados en silicio en comparación con los MOSFET es la corriente directa más pequeña, y la magnitud de la corriente directa está determinada por la eficiencia de la generación de corriente de túnel. La eficiencia de generación de la corriente de tunelización puede aumentarse reduciendo la banda prohibida entre la banda de valencia y la banda de conducción en la región que se utiliza para generar la corriente de tunelización de banda a banda o reduciendo el grosor de la región de tunelización. Por lo tanto, en la ingeniería de materiales, los dispositivos TFET basados en materiales semiconductores de banda estrecha y estructuras de túneles de heterounión se han desarrollado ampliamente [34,35,36,37,38]. Mientras tanto, la introducción de materiales bidimensionales en TFET como capas de tunelización con espesores ultrafinos se ha estudiado ampliamente [39,40,41,42,43,44]. Además, algunos artículos han informado sobre la confiabilidad de los TFET, como el efecto del dopaje de la fuente en el entrelazado de banda prohibida de tunelización [45], el efecto de la tunelización asistida por trampa en las características subumbrales de los TFET [46] y el efecto de la intercalación aleatoria dopaje sobre la perturbación del funcionamiento del dispositivo [47]. Sin embargo, los resultados de la investigación actual apuntan principalmente a las características y principios de funcionamiento básicos de los TFET individuales, y el propósito fundamental más importante de la investigación y el desarrollo de los TFET es proporcionar una unidad estructural básica con menor consumo de energía y reemplazar la estructura MOSFET existente. . Para lograr este objetivo fundamental, se debe configurar en un circuito específico para verificar su compatibilidad con la tecnología MOSFET. En la actualidad, la investigación sobre la estrategia de diseño de circuitos basada en dispositivos TFET se realiza gradualmente, como el circuito de señal analógica y mixta [48,49,50], el circuito lógico digital [50, 51], el diseño del circuito de gestión de potencia [52]. También hay estudios sobre el diseño de circuitos híbridos basados en MOSFET y TFET [53]. Sin embargo, los tipos de dopaje de la región de origen y la región de drenaje son opuestos entre sí, lo que crea una asimetría entre la región de origen y la región de drenaje. Esta estructura asimétrica hace que sea imposible reemplazar completamente MOSFET con la simetría fuente / drenaje.

Toma el n -tipo TFET como ejemplo. El lado con p -tipo impureza se utiliza como la región de origen, mientras que el otro lado con n impureza de tipo-se utiliza como la región de drenaje. Cuando el dispositivo funciona, se debe aplicar una diferencia de potencial positiva desde la región de drenaje a la región de origen. Si se intercambian el electrodo fuente y el electrodo de drenaje, es decir, el p -tipo región de impureza se establece en un mayor potencial en relación con el n -tipo región de impureza, luego la unión PN formada por la p -tipo región de impurezas y n -La región de impurezas de tipo siempre estará en el estado de polarización positiva, lo que provoca la falla de la función de control del electrodo de puerta, el TFET estará casi siempre en el estado encendido y no se puede apagar. En otras palabras, provoca la falla de la función del interruptor TFET. En otras palabras, los módulos funcionales del circuito (como las puertas de transmisión), que deben utilizar las características de conmutación bidireccional de los transistores para funcionar con normalidad, son difíciles de realizar utilizando TFET convencionales con una estructura asimétrica de fuente y drenaje, para solucionar estos problemas. , propusimos un TFET bidireccional intercambiable y simétrico de drenaje de fuente (B-TFET) [54], que muestra la ventaja de las características de conmutación bidireccional y la compatibilidad con circuitos integrados CMOS en comparación con los TFET asimétricos tradicionales. En este artículo, propusimos un B-TFET controlado por puerta bilateral modificado con un canal plano. Los efectos de parámetros estructurales clave, como las concentraciones de dopaje de N + región y P + región, longitud de N + región y longitud de la región intrínseca, en el rendimiento del dispositivo, por ejemplo, las características de transferencia, I en - yo desactivado relación y oscilación subumbral, se explican en detalle sobre la base de un análisis físico. A partir de entonces, estos parámetros estructurales clave se optimizan.

Métodos

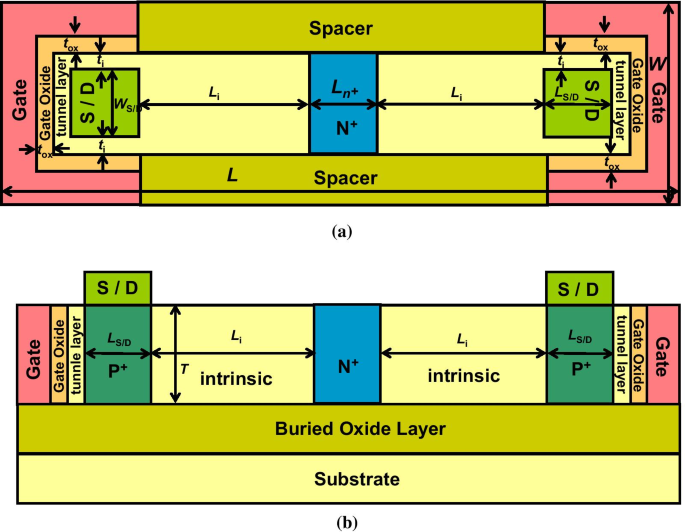

La Figura 1a muestra una vista superior esquemática del N-Tipo B-TFET controlado por puerta bilateral con un canal plano. La Figura 1b muestra una vista transversal del N-Tipo B-TFET controlado por puerta bilateral. A diferencia del TFET convencional, el B-TFET propuesto es completamente simétrico, la fuente / drenaje intercambiable P + Las regiones dopadas se encuentran a cada lado del cuerpo de silicio, y el electrodo de puerta se encuentra a ambos lados del cuerpo de silicio. Toda la estructura del dispositivo es simétrica. El N + -La región dopada está en la parte central del cuerpo de silicio. L y W son la longitud total y la anchura total del dispositivo propuesto, respectivamente. L i es la longitud de la región intrínseca; L N + es la longitud de N + región; L S / D y W S / D son la longitud y el ancho de P + regiones intercambiables fuente / drenaje, respectivamente; \ (T \) es el espesor del cuerpo de silicio; \ (t _ {{{\ text {ox}}}} \) es el espesor del óxido de la puerta; \ (t_ {i} \) es el grosor de la región intrínseca del túnel entre la región S / D y el óxido de la puerta.

un Vista superior esquemática del N-Type B-TFET bilateral controlado por puerta con canal plano. b Vista transversal del N-Type B-TFET bilateral controlado por puerta

En este artículo, se activan todos los modelos físicos, como el modelo estadístico de Fermi, el modelo de movilidad CVT, el modelo de recombinación Auger, el modelo de estrechamiento de la brecha de banda y un modelo estándar de tunelización banda a banda. Todos los parámetros del dispositivo en este documento se enumeran en la Tabla 1.

Resultados y discusión

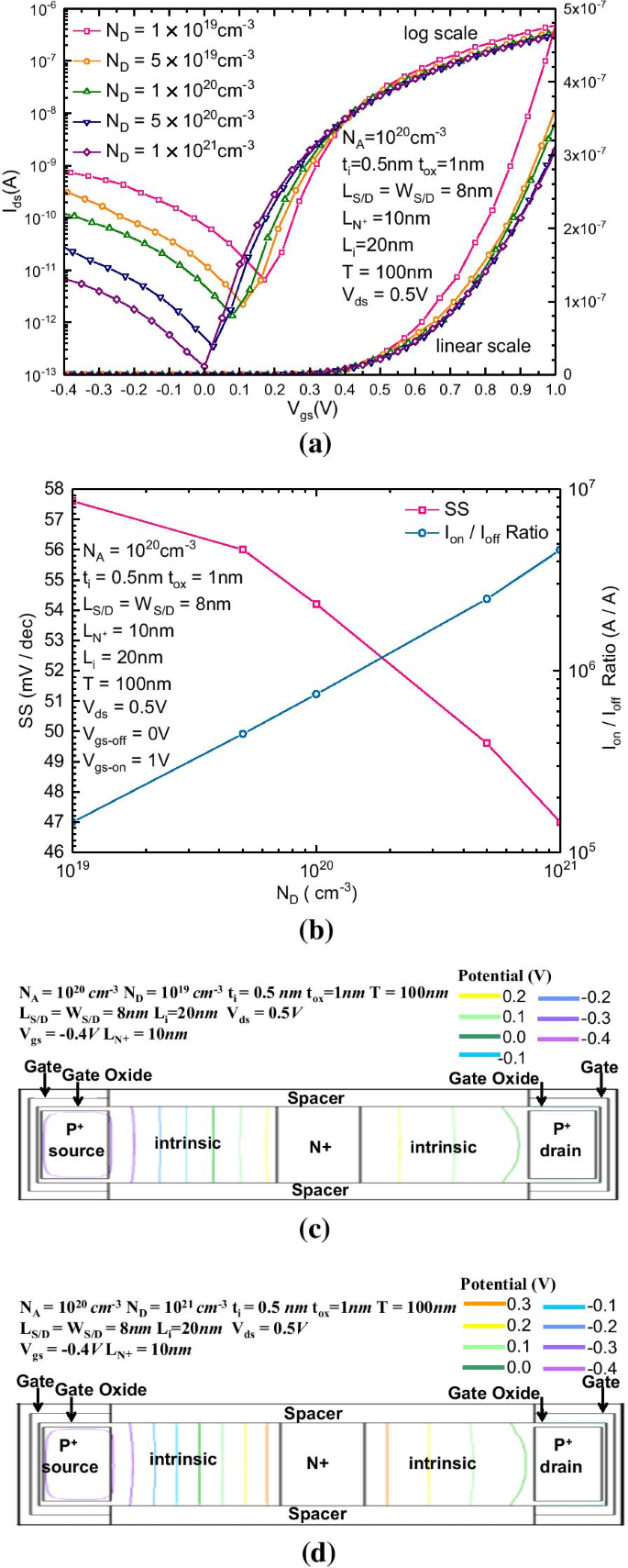

Las figuras 2a, b muestran la característica de transferencia, la relación \ (I _ {{{\ text {on}}}} {-} I _ {{{\ text {off}}}} \) y SS promedio con diferente \ (N_ { D} \) (\ (10 ^ {18} \) - \ (10 ^ {21} \, {\ text {cm}} ^ {- 3} \)). En la Fig. 2a, \ (N_ {D} \) afecta la intensidad de la corriente de fuga de drenaje a fuente con polarización inversa. Con el aumento de la concentración de dopaje, la corriente de fuga se suprime significativamente y la corriente directa no cambia significativamente. En la Fig. 2b, el SS y \ (I _ {{{\ text {on}}}} {-} I _ {{{\ text {off}}}} \) también se ven afectados por \ (N_ {D} \ ). Con el aumento de la concentración de dopaje, debido a que la corriente de fuga inversa se suprime significativamente, la corriente en el punto de funcionamiento estático disminuye, por lo que la SS promedio también disminuye. Debido a que la corriente directa se ve mucho menos afectada que la fuga inversa, la relación \ (I _ {{{\ text {on}}}} {-} I _ {{{\ text {off}}}} \) aumenta con el aumento en concentración de dopaje. Las figuras 2c, d muestran las distribuciones de potencial bidimensionales del B-TFET propuesto con \ (N_ {D} \) igual a 10 19 cm −3 y 10 21 cm −3 , respectivamente. Cuando el electrodo de puerta está polarizado inversamente, se generará un fuerte campo eléctrico entre el electrodo de drenaje polarizado hacia adelante y el electrodo de puerta polarizado inverso, lo que da como resultado un fuerte túnel de banda a banda cerca de la región de drenaje. Entre los pares de huecos-electrones generados resultantes, los electrones pueden fluir directamente fuera del electrodo de drenaje, mientras que los huecos de la banda de valencia deben fluir a través del N + región, posteriormente a la región intrínseca en el lado de la fuente y ser descargada por el electrodo fuente para formar la corriente de fuga continua. Para minimizar la corriente de fuga, los orificios producidos por la tunelización de banda a banda deben bloquearse eficazmente para que no fluyan fuera de la región N +. En comparación con la región N + con menor concentración, la región N + con mayor concentración forma una diferencia de potencial mayor entre la región P + y la región N +, es decir, el valor potencial en el límite entre la región intrínseca y la región N + aumentará con el aumento en \ (N_ {D} \) porque la región N + con mayor concentración puede producir una mayor diferencia de concentración electrónica entre la fuente y el drenaje. Luego, se pueden difundir más electrones desde la región N + a las regiones intrínsecas en ambos lados de la región N +, lo que aumenta la cantidad de carga positiva (compuesta principalmente de donante) en la región N + después de la ionización y, en consecuencia, aumenta el potencial. diferencia entre la región P + y la región N +. Precisamente porque la región N + con mayor concentración de dopaje tiene un potencial más alto que los lados de la fuente y del drenaje después de la ionización, los orificios generados por el túnel de banda a banda cerca de la región de drenaje se pueden bloquear de manera más efectiva, lo que disminuye de manera más efectiva el corriente de fuga.

un \ (I _ {{{\ text {ds}}}} {-} V _ {{{\ text {gs}}}} \) transferir características y b variación en SS y la relación \ (I _ {{{\ text {on}}}} {-} I _ {{{\ text {off}}}} \) del B-TFET propuesto con diferente \ (N_ {D } \); la distribución de potencial bidimensional con sesgo inverso con c N D =10 19 cm −3 y d N D =10 21 cm −3

Además de la concentración de dopaje de la región N +, otro parámetro clave de la región N +, que puede afectar significativamente la corriente de fuga con polarización inversa, es la longitud de la región N +. Las figuras 3a, b muestran las características de transferencia \ (I _ {{{\ text {ds}}}} {-} V _ {{{\ text {gs}}}} \) del B-TFET propuesto con diferentes L N + . La corriente de fuga con polarización inversa disminuye en gran medida al aumentar L N + . Como muestra la Fig. 2b, la oscilación del subumbral y \ (I _ {{{\ text {on}}}} {-} I _ {{{\ text {off}}}} \) también se ven afectados por L N + . Con el aumento de L N + , debido a que la corriente de fuga inversa se suprime significativamente, la corriente en el punto de funcionamiento estático y la SS media también se reducen. La corriente directa se ve mucho menos afectada que la fuga inversa, y la relación \ (I _ {{{\ text {on}}}} {-} I _ {{{\ text {off}}}} \) aumenta con el aumento en L N + . Las figuras 3c, d muestran la distribución bidimensional de la concentración de huecos del B-TFET propuesto con L N + igual a 2 nm y 80 nm, respectivamente. Cuando L N + es igual a 2 nm, la concentración mínima de agujeros en la región N + es mayor que 10 17 cm −3 , mientras que cuando L N + es igual a 80 nm, la concentración mínima del orificio es inferior a 10 14 cm −3 . El aumento de longitud de la región N + mejora su capacidad para evitar que los agujeros pasen a través de la región N +. Como portador minoritario fuera del equilibrio en la región N +, cuando la región N + es más larga, se recombinarán más huecos con electrones antes de pasar a través de la región N +, por lo que el aumento de longitud de la región N + también puede formar un corriente de fuga continua con polarización inversa. La SS promedio se puede reducir a 40.2 mV / dec, y la relación \ (I _ {{{\ text {on}}}} {-} I _ {{{\ text {off}}}} \) puede exceder 10 10 .

un \ (I _ {{{\ text {ds}}}} {-} V _ {{{\ text {gs}}}} \) características; b variación en el SS y la relación \ (I _ {{{\ text {on}}}} {-} I _ {{{\ text {off}}}} \) del B-TFET propuesto con diferentes L N + ; Distribución bidimensional de la concentración de agujeros del B-TFET propuesto con polarización inversa para L N + igual a (3) 2 nm y (4) 80 nm

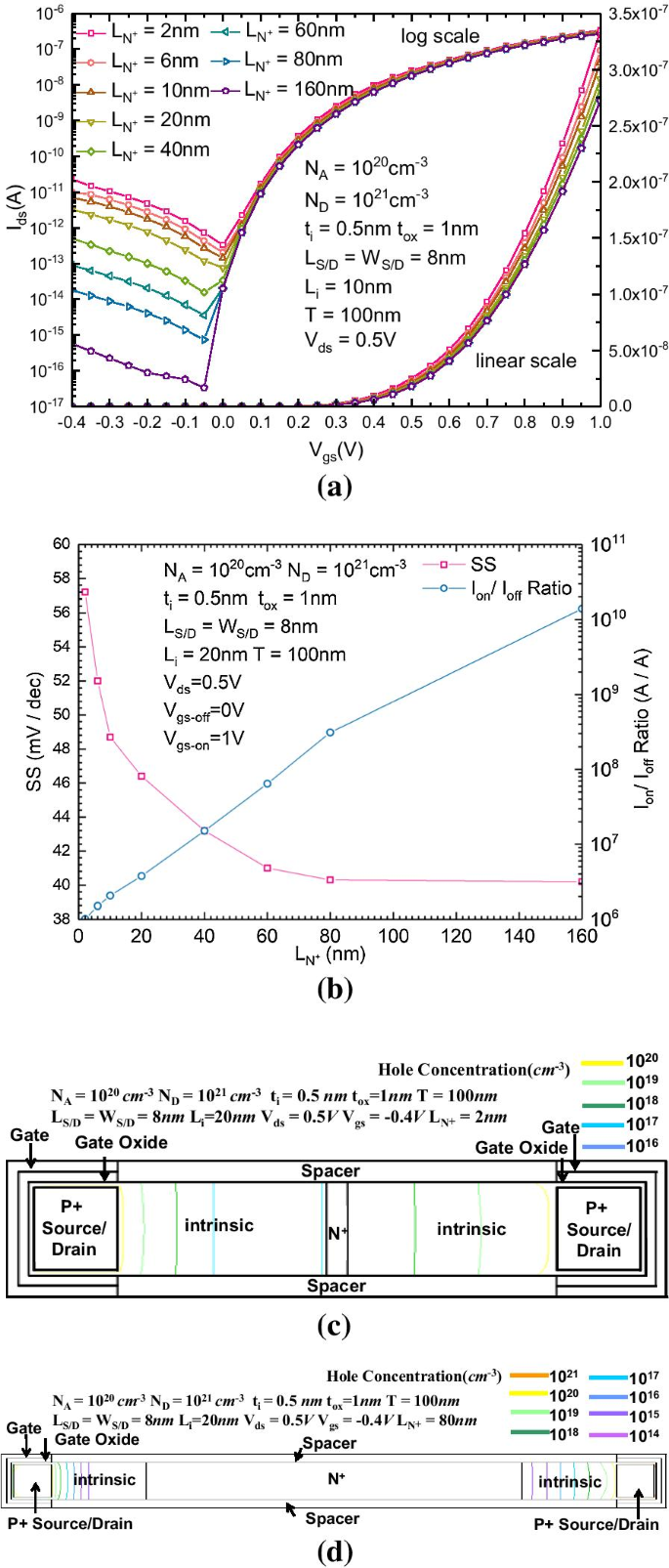

Las figuras 4a, b muestran las características de transferencia \ (I _ {{{\ text {ds}}}} {-} V _ {{{\ text {gs}}}} \) y los cambios en SS y \ (I _ {{{ \ text {on}}}} {-} I _ {{{\ text {off}}}} \) relación del B-TFET propuesto con diferentes L i , respectivamente. La corriente directa disminuye al aumentar L i porque la resistencia de la región intrínseca es proporcional a su longitud. Luego, para maximizar la corriente directa, se debe minimizar la longitud de la región intrínseca. Sin embargo, la disminución en la longitud de la región intrínseca mejora el campo eléctrico en la región intrínseca entre la región de la fuente P + y la región N +, por lo que la flexión de la banda cerca de esta región es mayor que la región intrínseca cerca del electrodo de drenaje, lo que induce corriente de fuga con polarización más inversa. Las figuras 4c, d muestran la distribución de potencial bidimensional con sesgo inverso del B-TFET propuesto para L i igual a 4 nm y 100 nm, respectivamente. Para la L más corta i (4 nm), el campo eléctrico en la región intrínseca entre la región fuente P + y la región N + cerca del electrodo fuente es mucho más fuerte que el de la región intrínseca entre la región de drenaje P + y la región N + cerca de la electrodo de drenaje. Entonces, la corriente de fuga permanece casi constante, lo cual es independiente del cambio en el voltaje de la puerta. La Figura 4b muestra que el rango de valores óptimos de L i es aproximadamente de 7 a 10 nm, donde la SS disminuye a un valor de valle de 41 mV / dec y la \ (I _ {{{\ text {on}}}} {-} I _ {{{\ text {off}}} } \) la proporción aumenta a un valor máximo de casi 10 8 .

un \ (I _ {{{\ text {ds}}}} {-} V _ {{{\ text {gs}}}} \) características de B-TFET y b variación en SS y la relación \ (I _ {{{\ text {on}}}} {-} I _ {{{\ text {off}}}} \) con diferente \ (L_ {i} \); Distribución de potencial bidimensional con sesgo inverso del B-TFET propuesto para L i igual a c 20 nm y d 100 millas náuticas

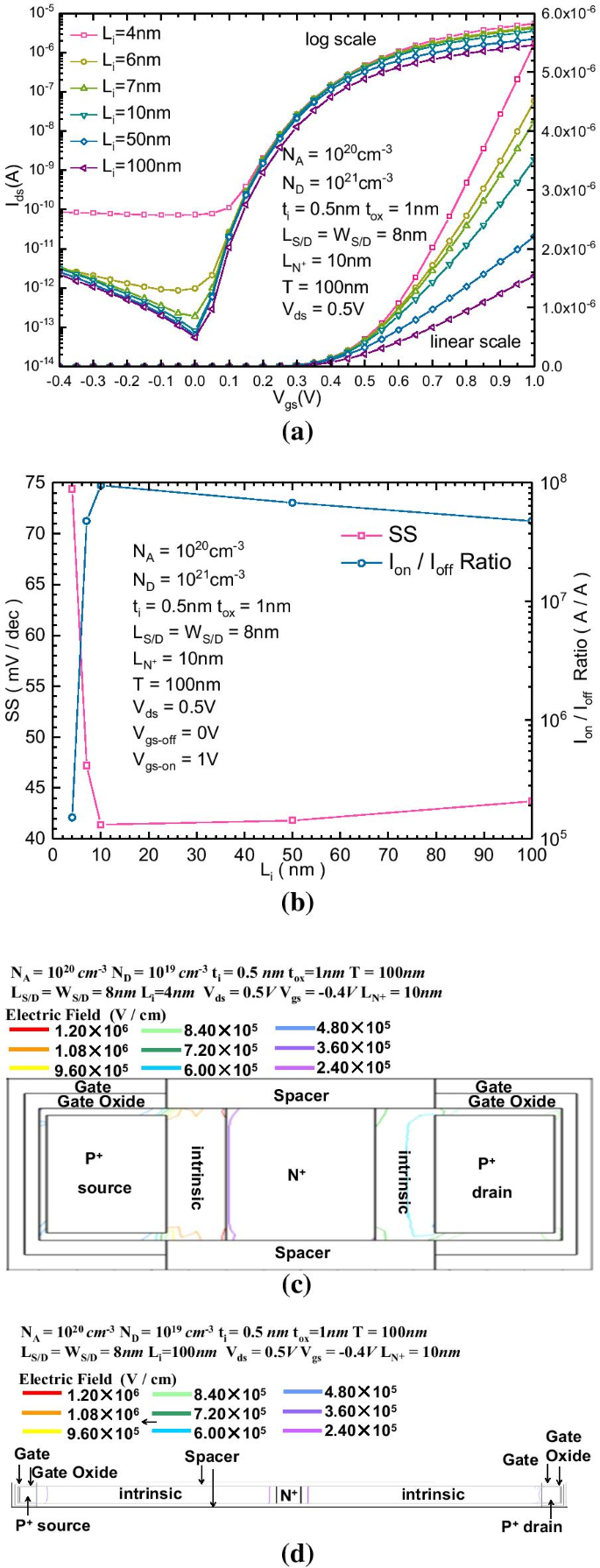

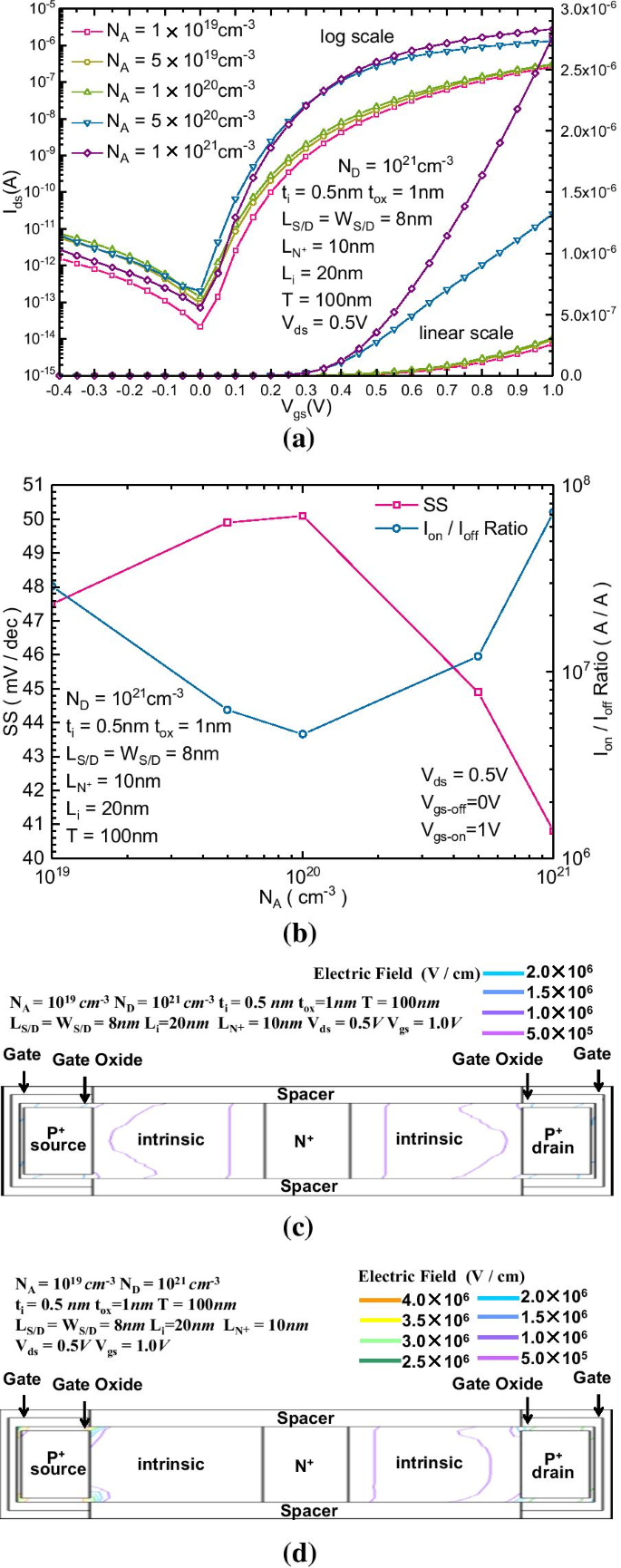

Las figuras 5a, b muestran las características de transferencia \ (I _ {{{\ text {ds}}}} {-} V _ {{{\ text {ds}}}} \) y el cambio en SS y \ (I _ {{{ \ text {on}}}} {-} I _ {{{\ text {off}}}} \) relación del B-TFET propuesto con diferente \ (N_ {A} \). La Figura 5a muestra que al aumentar la concentración de la región dopada con P +, podemos obtener menos SS y una mayor corriente directa. La corriente de fuga con polarización inversa obviamente no se ve afectada por el cambio en \ (N_ {A} \), pero la corriente directa puede incrementarse con el aumento en \ (N_ {A} \). En la Fig. 5b, tanto SS como \ (I _ {{{\ text {on}}}} {-} I _ {{{\ text {off}}}} \) se pueden mejorar aumentando \ (N_ {A } \). Las figuras 5c, d muestran la distribución bidimensional del campo eléctrico del B-TFET propuesto con \ (N_ {A} \) igual a 10 19 cm −3 y 10 21 cm −3 , respectivamente. El aumento de \ (N_ {A} \) mejora el campo eléctrico en la región intrínseca del túnel; luego, se pueden generar más pares de agujeros de electrones a través del tunelización banda a banda, lo que mejora la corriente directa del B-TFET propuesto.

un \ (I _ {{{\ text {ds}}}} {-} V _ {{{\ text {gs}}}} \) transferir características, b variación en SS y \ (I _ {{{\ text {on}}}} {-} I _ {{{\ text {off}}}} \) relación del B-TFET propuesto con diferente \ (N_ {A} \). Distribución bidimensional de campo eléctrico con polarización inversa del B-TFET propuesto para \ (N_ {A} \) igual a (3) 10 19 cm −3 y (4) 10 21 cm −3

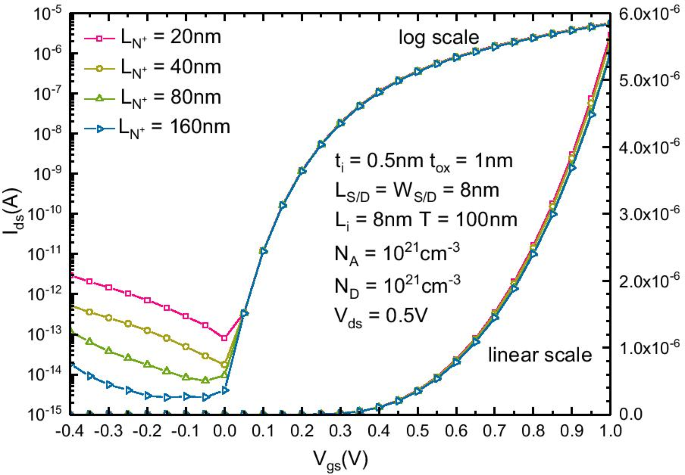

De acuerdo con la discusión anterior, tanto \ (N_ {D} \) como \ (N_ {A} \) deben establecerse en el valor máximo posible. El rango de valor óptimo de L i es de 7 a 10 nm. Sin embargo, existe una compensación entre el consumo de energía estática y L N + . La Figura 6 muestra las características de transferencia \ (I _ {{{\ text {ds}}}} {-} V _ {{{\ text {ds}}}} \) del B-TFET optimizado con diferentes L N + . L N + se puede seleccionar de acuerdo con diferentes requisitos de diseño de consumo de energía estática. Como compromiso, para garantizar que la relación \ (I _ {{{\ text {on}}}} {-} I _ {{{\ text {off}}}} \) sea superior a 10 8 , L N + se recomienda estar por encima de 20 nm. La corriente de encendido aumenta a aproximadamente 6 × 10 –6 A, y la SS se reduce a 38 mV / dec.

\ (I _ {{{\ text {ds}}}} {-} V _ {{{\ text {ds}}}} \) características de transferencia del B-TFET optimizado con diferentes L N +

Conclusiones

En este artículo, se analizan los efectos de los parámetros estructurales y el mecanismo interno de un transistor de efecto de campo de efecto túnel bidireccional S / D simétrico e intercambiable bidireccional controlado por compuerta bilateral. Los efectos de los parámetros clave como la concentración y la longitud de la región N +, la longitud de la región intrínseca entre las regiones P + y N + y la concentración de la región P + se han discutido en detalle. Comparado con el TFET convencional, el B-TFET tiene la ventaja de una fuerte resistencia a la corriente de fuga polarizada inversamente. A partir de entonces, se puede obtener un buen rendimiento, como un SS promedio más bajo y una relación \ (I _ {{{\ text {on}}}} {-} I _ {{{\ text {off}}}} \) más alta. Además, debido a la simetría estructural y las características de conmutación bidireccional e intercambiable fuente / drenaje, es más compatible con el circuito CMOS.

Disponibilidad de datos y materiales

Incluimos una declaración de disponibilidad de datos y material para nosotros y en nombre de nuestros coautores bajo los "Intereses en competencia". Todos los datos y materiales disponibles son obra original. Todos los datos se han proporcionado claramente en el manuscrito sin datos adicionales ni materiales de apoyo.

Abreviaturas

- L :

-

Longitud total del dispositivo propuesto

- W :

-

Ancho total del dispositivo propuesto

- L i :

-

Longitud de la región intrínseca

- L N + :

-

Longitud de N + región

- L S / D :

-

Longitud de la P + regiones intercambiables fuente / drenaje

- W S / D :

-

Ancho de la P + regiones intercambiables fuente / drenaje

- \ (T \):

-

Espesor del cuerpo de silicona

- \ (t _ {{{\ text {ox}}}} \):

-

Espesor del óxido de la puerta

- \ (t_ {i} \):

-

Espesor de la región intrínseca del túnel entre la región S / D y el óxido de la puerta

- MOSFET:

-

Transistor de efecto de campo semiconductor de óxido metálico

- TFET:

-

Transistor de efecto de campo de túnel

Nanomateriales

- El diodo Shockley

- Estudio de los primeros principios sobre la estabilidad y la imagen STM del borofeno

- Efecto de la distribución de nanopartículas de oro en TiO2 sobre las características ópticas y eléctricas de las células solares sensibilizadas por colorante

- El efecto del plasma de no equilibrio por contacto sobre las propiedades estructurales y magnéticas de Mn Х Fe3 - X О4 Espinelas

- Efecto del tratamiento de recocido in situ sobre la movilidad y morfología de transistores de efecto de campo orgánico basados en TIPS-pentaceno

- Estudio experimental sobre las características de flujo y transferencia de calor de nanofluidos de agua-TiO2 en un tubo estriado en espiral

- Matrices de nanotubos de TiO2:fabricadas con una plantilla blanda-dura y la dependencia del tamaño de grano del rendimiento de las emisiones de campo

- Estudio sobre la memoria de conmutación de resistencia multinivel y el fotovoltaje dependiente del estado de la memoria en uniones Pt / Nd:SrTiO3

- Diseño y ajuste de la función de trabajo del grafeno mediante tamaño, modificación, defectos y dopaje:un estudio de teoría del primer principio

- Un estudio de nanofibras de carbono y carbón activo como supercondensador simétrico en un electrolito acuoso:un estudio comparativo

- Prueba de las propiedades estructurales, electrónicas y magnéticas de Ag n V (n =1–12) Clusters