Transistor semiconductor de óxido metálico de doble difusión lateral de resistencia específica ultrabaja con doble puerta mejorada y capa parcialmente enterrada en P

Resumen

Una resistencia específica ultrabaja ( R encendido, sp ) transistor semiconductor de óxido metálico de doble difusión lateral (LDMOS) con doble puerta mejorada y capa parcial P enterrada se propone e investiga en este artículo. El modelo analítico de resistencia para el LDMOS propuesto está construido para proporcionar una visión profunda de la relación entre la resistencia de la región de deriva y la resistencia de la región del canal. La capa N-enterrada se introduce debajo del pozo P para proporcionar una ruta de conducción de baja resistencia y reducir significativamente la resistencia de la región del canal. La estructura mejorada de doble puerta está formada por una capa N-enterrada al tiempo que evita la ruptura de perforación vertical en estado apagado. La capa parcial enterrada en P con longitud optimizada se adopta debajo de la región de deriva N para extender la región de agotamiento vertical y relajar el pico del campo eléctrico en estado apagado, lo que mejora el voltaje de ruptura (BV) con baja resistencia a la región de deriva. Para LDMOS con doble puerta mejorada y capa parcial enterrada en P, el resultado muestra que R encendido, sp es de 8,5 mΩ · mm 2 mientras que BV es 43 V.

Antecedentes

Con el aumento de la demanda de una función lógica más compleja y rápida en el circuito integrado de potencia analógica, es importante mejorar el rendimiento del transistor semiconductor de óxido metálico de doble difusión lateral (LDMOS), minimizando especialmente la resistencia de encendido específica ( R encendido, sp ) y maximizar la tensión de ruptura en estado desactivado (BV) [1,2,3,4,5,6,7,8,9]. Las tecnologías más desarrolladas se centran en la región de deriva y se optimizan para mejorar la compensación de R encendido, sp vs. BV para dispositivos LDMOS [10,11,12,13,14,15,16,17,18,19,20]. En nuestro trabajo anterior, se propuso el LDMOS con aislamiento de zanja ultra superficial (USTI) [21]. La profundidad y el ángulo de esquina de USTI se optimizaron para lograr el mejor rendimiento de su clase. Sin embargo, para el LDMOS de bajo voltaje, la región de deriva está perdiendo dominio en R encendido, sp y la contribución de la región del canal no se puede ignorar.

Método

En este trabajo, se investiga un nuevo LDMOS de resistencia específica ultrabaja con doble puerta mejorada y capa parcial enterrada en P. Los modelos físicos IMPACT.I, BGN, CONMOB, FLDMOB, SRH y SRFMOB se utilizan en simulación numérica. Se propone un modelo analítico de resistencia para proporcionar una visión profunda de la relación entre la resistencia de la región de deriva y la resistencia de la región del canal. Según el modelo, la capa N-enterrada y la capa parcial P-enterrada se optimizan para lograr una R baja encendido, sp y BV alto.

Resultados y discusión

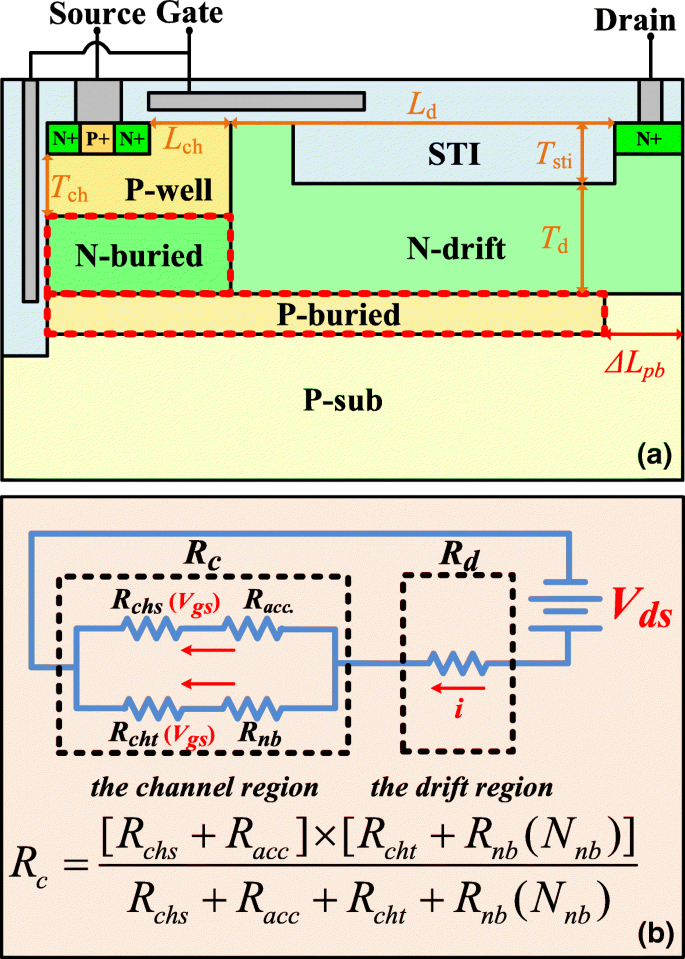

La Figura 1a muestra la sección transversal esquemática de LDMOS de resistencia específica ultrabaja con puerta doble mejorada y capa parcial P enterrada. El LDMOS presenta la puerta doble con capa N-enterrada y la capa parcial P-enterrada que contribuye a reducir R encendido, sp y mejorar la VB, respectivamente. En la región del canal, la puerta doble mejorada está formada por una puerta de trinchera y una capa enterrada con N altamente dopada. En comparación con la estructura convencional de doble puerta, la capa N-enterrada reduce significativamente la resistencia de la región del canal al proporcionar una ruta de conducción de baja resistencia debajo del pozo P en el estado encendido. En la región de deriva, la capa parcialmente enterrada en P con alta concentración de dopaje se introduce debajo de la región de deriva de N para mejorar la VB mientras se mantiene un R bajo encendido, sp . La capa parcialmente enterrada en P ayuda a reducir el campo eléctrico vertical en el estado apagado sin romper el equilibrio de carga en la región de deriva. El tamaño de la clave del dispositivo novedoso se enumera en la Tabla 1.

un Vista esquemática de la sección transversal de LDMOS de resistencia específica ultrabaja con puerta doble mejorada y capa enterrada en P parcial. b Resistencia activa equivalente esquemática para el LDMOS propuesto

La Figura 1b muestra el modelo de resistencia equivalente esquemático para el LDMOS propuesto. La on-resistencia total se considera como la resistencia de la región de deriva ( R d ) y la resistencia de la región del canal ( R c ) en series. En la región del canal, el camino de conducción del canal de superficie es paralelo al camino de conducción del canal de trinchera. Por lo tanto, R c es igual a ( R chs + R acc ) // ( R cht + R nb ), donde R chs , R acc , R cht y R nb son las resistencias del canal de la puerta de superficie, la región de acumulación, el canal de la puerta de la zanja y la capa N-enterrada, respectivamente. Basado en el modelo de resistencia propuesto, la reducción de R c lograría al disminuir R nb sin afectar las otras prestaciones, porque las otras resistencias están determinadas principalmente por la tecnología de proceso, la tensión de funcionamiento y la tensión de umbral. La R d se ha reducido mediante la introducción de una capa enterrada con P debajo de la región de deriva de N para mejorar el efecto Reducir el campo de superficie (RESURF) en nuestro trabajo anterior. En este trabajo, se adopta la capa enterrada de P parcial para mejorar el BV mientras se mantiene el bajo R d .

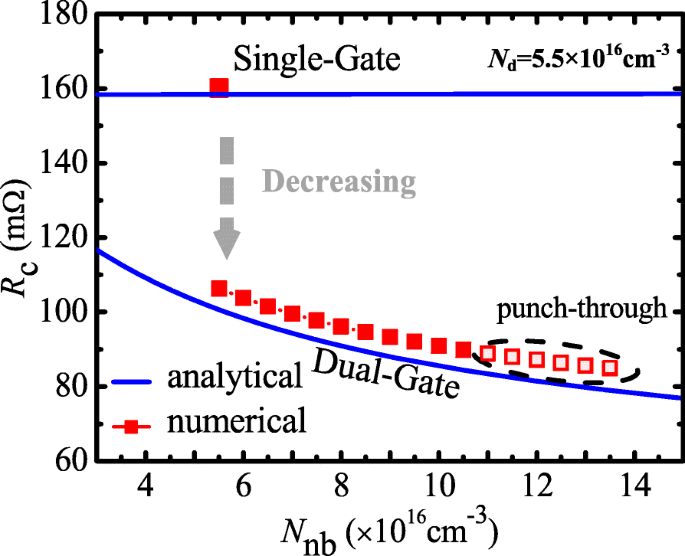

Apuntando a la reducción de R c , la capa N-enterrada con alta concentración de dopaje se introduce debajo del pozo P. La figura 2 muestra R numérica y analítica c en función de la concentración de dopaje de la capa N-enterrada ( N nb ) con puerta simple y puerta doble. Se indica que la estructura de doble puerta ayuda a reducir R c en comparación con la puerta única. Cuando N nb = N d =5,5 × 10 16 cm −3 , R c es 110 mΩ. Según el modelo de resistencia, R nb es el principal contribuyente a R c . Y luego, la R nb se desea disminuir con el objetivo de reducir R c . Como se muestra en la Fig. 2a, R c se reduce con N nb creciente. Cuando N nb =1,35 × 10 17 cm −3 , R c se reduce a 85 mΩ. Sin embargo, la Fig.2 también muestra que N nb estaría limitado por el desglose por perforación. Debido a la adición de una puerta de trinchera, R c se reduce en primer lugar en un 34% con N nb = N d =5,5 × 10 16 cm −3 . Como N nb aumenta, R c disminuye continuamente. Con N optimizado nb =1.05 × 10 17 cm −3 , R c se reduce en un 45% por fin. Cuando N nb > 1.05 × 10 17 cm −3 , se producirá una ruptura de perforación en el pozo P. El resultado analítico de R encendido, sp que se muestra en la Fig. 2 indica que el modelo propuesto proporciona un buen ajuste con los resultados de la simulación numérica. Por lo tanto, el modelo es creíble para guiar el diseño de optimización.

R numérico y analítico c en función de N nb con puerta única y puerta doble ( Z =1 cm). N d es la concentración de dopaje de la región de deriva N

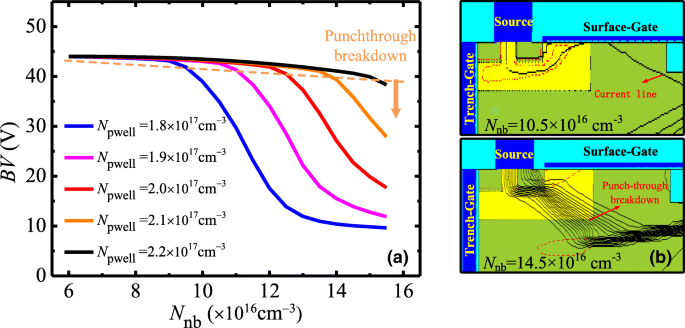

La figura 3a muestra BV numérico en función de N nb con diferente concentración de dopaje de P-well ( N pwell ). N nb tiene un efecto no solo en la R c , sino también el BV. Para un N dado pwell , BV se mantiene sin cambios en una pequeña N nb y luego disminuye con N nb creciente. Cuando N nb aumenta a 1,2 × 10 17 cm −3 , BV comienza a disminuir con N pwell =2 × 10 17 cm −3 . La caída de BV se atribuye a la rotura por perforación en la región del pozo P, como se muestra en la Fig. 3b. A medida que aumenta el voltaje de drenaje, la región de agotamiento en el pozo P se extiende hasta la fuente. Cuando la región de agotamiento ataca la unión del pozo N + / P, se produce la ruptura por perforación. Para un N grande pwell , el agotamiento se extiende principalmente a la región de deriva y se evita la rotura por perforación sin degradar el BV. Aunque el pozo P con alta concentración de dopaje se beneficia de evitar la ruptura por perforación, mejoraría el voltaje de umbral. Por lo tanto, N pwell de 2 × 10 17 cm −3 se elige teniendo en cuenta el voltaje umbral y la compensación entre BV y R encendido, sp .

un BV numérico en función de N nb con diferentes N pwell . b Perfil de densidad de corriente para N nb =10,5 × 10 16 cm −3 y 14,5 × 10 16 cm −3 mientras que N pwell =2 × 10 17 cm −3 en avería

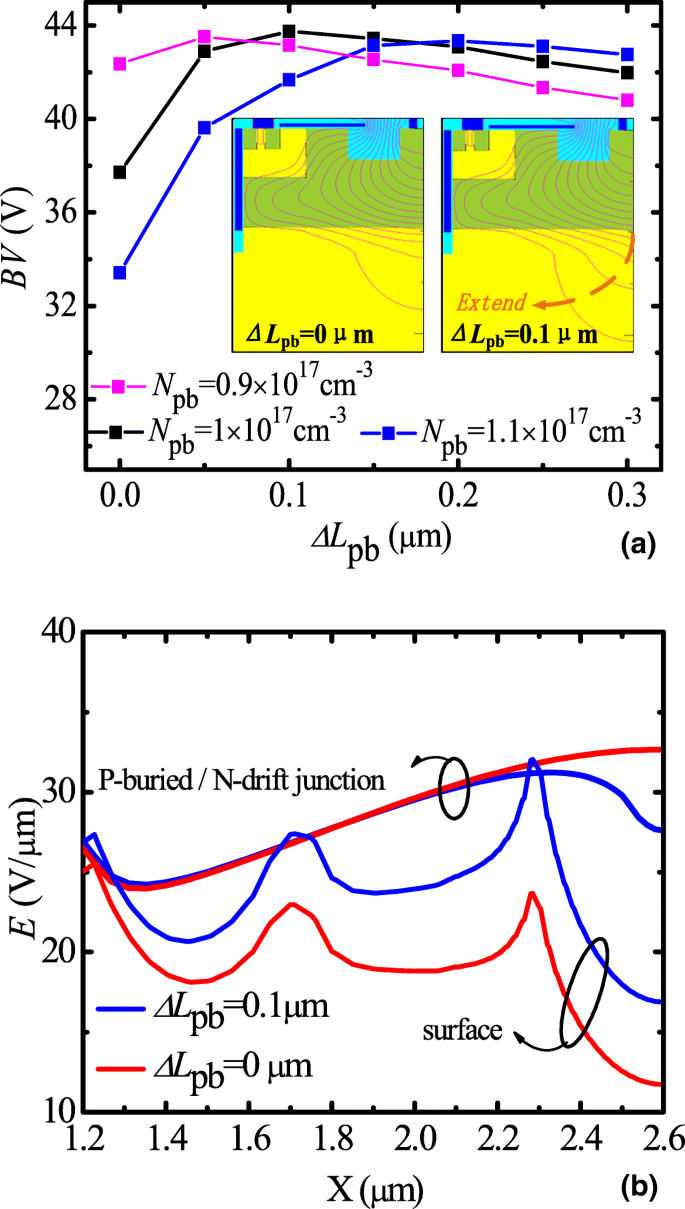

Para lograr una R baja d y alto BV, se introduce una capa parcialmente enterrada en P debajo de la región de deriva de N. La figura 4a muestra BV en función de Δ L pb con diferentes N pb . Para un N dado pb , como Δ L pb aumenta, BV aumenta y luego disminuye ligeramente. Cuando Δ L pb =0,1 μm, N pb =1 × 10 17 cm −3 , BV alcanza el valor máximo 43 V. La plaquita muestra el perfil del contorno equipotencial con N pb =1 × 10 17 cm −3 . Se indica que el contorno equipotencial en la estructura de la capa enterrada en P parcial se extiende más al sustrato en comparación con la capa enterrada en P completa. La Figura 4b muestra la distribución del campo eléctrico en la superficie y la interfaz de unión P-enterrada / N-deriva. Para LDMOS convencionales optimizados, la ruptura ocurre generalmente en la interfaz N-deriva / P-enterrado. Para el LDMOS propuesto, la unión de N-deriva / P-sub reemplaza la unión de N-deriva / P-enterrado para relajar el campo eléctrico vertical y extender la región de agotamiento, lo que da como resultado un BV más alto mientras se mantiene bajo R d .

un BV en función de ΔL pb con diferentes N pb . La plaquita es el perfil de contorno equipotencial con N pb =1 × 10 17 cm −3 . b Distribución del campo eléctrico en la superficie y la interfaz de unión P-enterrada / N-deriva

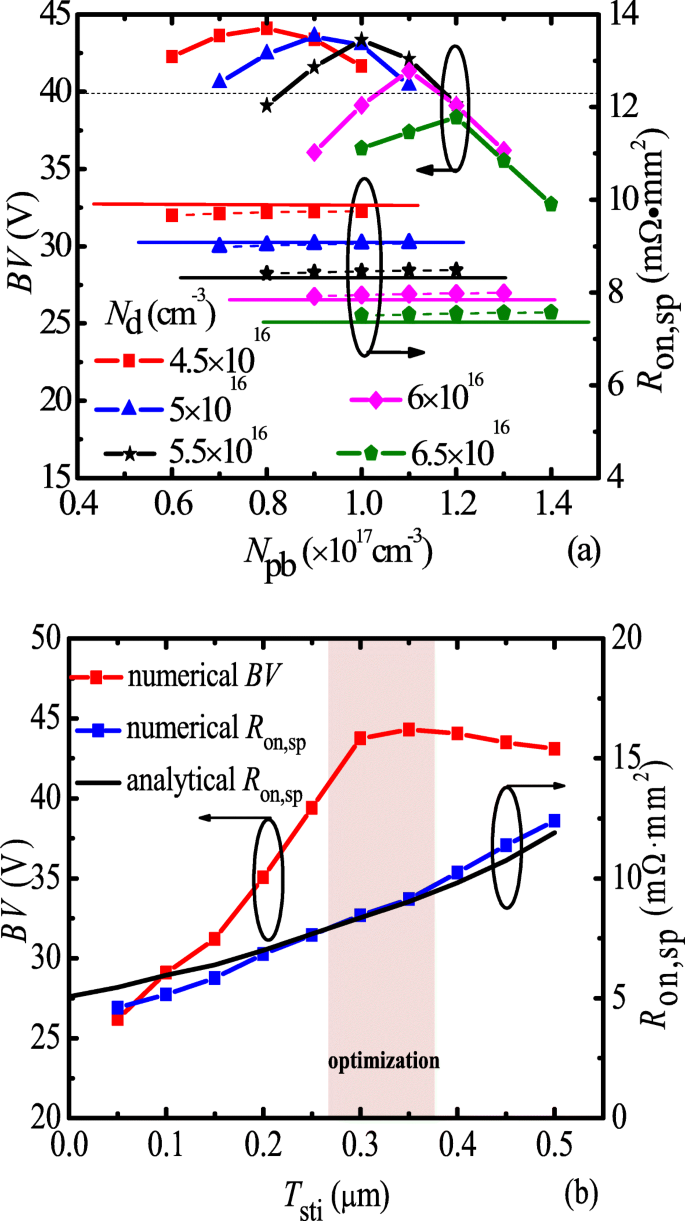

Se requiere un equilibrio de carga entre la deriva de N y la capa enterrada de P parcial para lograr un BV alto. La figura 5a muestra que BV y R numéricos y analíticos encendido, sp en función de la concentración de dopaje del P-enterrado ( N pb ) para diferentes N d . Para un N dado d , BV tiene un valor máximo con variado N pb y el máximo de BV aumenta con la disminución de N d . Sin embargo, R encendido, sp se puede aumentar como N d decreciente. Debido a BV requiere más de 40 V, el N d =5,5 × 10 16 cm −3 y N pb =1 × 10 17 cm −3 son elegidos. La figura 5b muestra BV y R numéricos y analíticos encendido, sp en función del grosor de la capa STI ( T sti ). T sti tiene un fuerte impacto en BV y R encendido, sp , y debe diseñarse y optimizarse cuidadosamente al igual que nuestro trabajo anterior [21]. Para T sti <0.3 μm, el punto de ruptura debajo del borde de la placa de campo polivinílico tiene un pico de campo eléctrico alto. Como T sti aumenta, el pico del campo eléctrico se relaja y luego BV aumenta. Para T sti =0,3 μm, se obtiene un BV de 43 V. Para T sti ≥ 0.3 μm, el pico del campo eléctrico debajo del borde de la placa de campo polivinílico es lo suficientemente bajo, como resultado, el punto de ruptura se transfiere a la unión P / N debajo del lado del drenaje. Como T sti aumenta, BV aumenta y luego se satura.

un BV y R numéricos (línea de puntos) y analíticos (línea sólida) encendido, sp como funciones de N pb para diferentes N d . b BV y R numéricos (línea de puntos) y analíticos (línea sólida) encendido, sp como funciones de T sti

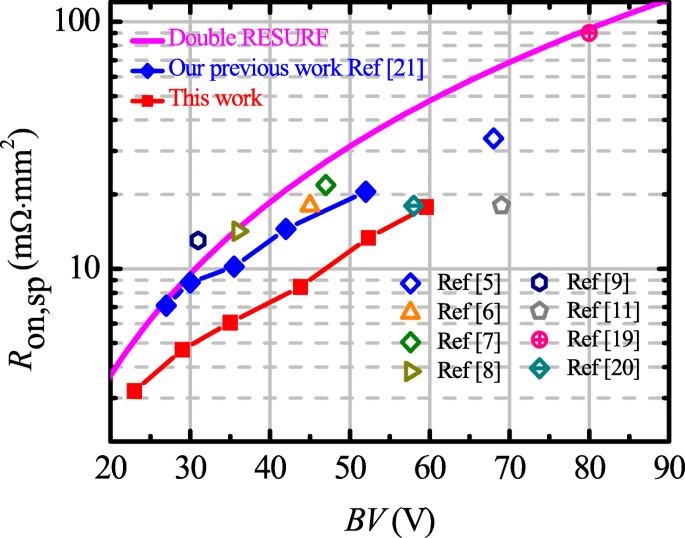

La Figura 6 muestra el punto de referencia de las tecnologías Bipolar-CMOS-DMOS (BCD) existentes y el LDMOS propuesto. Aparentemente, la tecnología de proceso para LDMOS propuesto es compatible con nuestra tecnología BCD desarrollada que logró el mejor rendimiento de su clase de LDMOS. En el proceso de fabricación del LDMOS propuesto, la capa N-enterrada podría compartir la misma máscara con el P-well. Para el LDMOS propuesto, R encendido, sp es de 8,5 mΩ · mm 2 mientras que BV =43 V, que se reduce en aproximadamente un 37% en comparación con nuestro trabajo anterior.

El punto de referencia de las tecnologías BCD existentes y el LDMOS propuesto

Conclusión

En este artículo se propone e investiga un nuevo LDMOS de resistencia específica ultrabaja con doble puerta mejorada y capa parcial enterrada en P, mediante simulación numérica. La capa N-enterrada con alta concentración de dopaje se utiliza para lograr una puerta doble mejorada con reducción de R c . Se introduce una capa parcialmente enterrada en P debajo de la región de deriva N para mejorar BV con mantener el equilibrio de carga. El proceso de fabricación del LDMOS en este trabajo es compatible con la tecnología BCD existente informada en nuestro trabajo anterior. El resultado muestra que la R encendido, sp del LDMOS propuesto se reduce en un 37% en BV de 43 V en comparación con el trabajo anterior. Con la tecnología de procesamiento de semiconductores llegando a un nivel nanométrico, la R encendido, sp puede reducirse aún más con la disminución de la longitud del canal.

Abreviaturas

- BCD:

-

Bipolar-CMOS-DMOS

- BV:

-

Voltaje de ruptura

- LDMOS:

-

Transistor semiconductor de óxido metálico de doble difusión lateral

- RESURF:

-

Reducir el campo de superficie

- R encendido, sp :

-

On-resistencia específica

- USTI:

-

Aislamiento de zanja ultra superficial

Nanomateriales

- Nanofibras y filamentos para una mejor administración de fármacos

- Características de alineación interfacial, eléctrica y de banda de pilas de HfO2 / Ge con capa intermedia de SiO2 formada in situ mediante deposición de capa atómica mejorada por plasma

- Un nuevo fotocatalizador de heterounión Bi4Ti3O12 / Ag3PO4 con rendimiento fotocatalítico mejorado

- Efecto de la estabilidad térmica mejorada de la capa de soporte de alúmina sobre el crecimiento de nanotubos de carbono de pared simple alineados verticalmente y su aplicación en membranas de nanof…

- Influencia de nanopartículas de agricultura con diferentes tamaños y concentraciones incrustadas en una capa compacta de TiO2 en la eficiencia de conversión de las células solares de perovskita

- Potencial de activación antiproliferativa y de apoptosis de nanopartículas de lípidos dirigidos a base de paclitaxel con internalización celular mejorada por receptores de transferrina:un estudio …

- Absorbedor omnidireccional por el efecto del plasma del vacío en la región visible con campo eléctrico localizado muy mejorado

- Transistor de efecto de campo SnSe2 con alta relación de encendido / apagado y fotoconductividad con conmutación de polaridad

- Nanomembranas de TiO2 fabricadas por deposición de capa atómica para electrodo de supercondensador con capacitancia mejorada

- Nanohojas porosas de ZnO con modificación parcial de la superficie para una separación de cargas mejorada y una alta actividad fotocatalítica bajo irradiación solar

- Pasivación de Si mejorada y eficiencia de células solares PERC mediante óxido de aluminio depositado en capa atómica con recocido posterior en dos pasos