FET de canal U de puerta rectangular de alto rendimiento con solo 2 nm de distancia entre los contactos de fuente y drenaje

Resumen

En este documento se propone un novedoso FET de canal en U de puerta rectangular de alto rendimiento (RGUC FET) para una distancia integrada extrema entre los contactos de fuente y drenaje. El RGUC FET representa características de subumbral casi ideales hasta que la distancia entre los contactos fuente / drenaje (S / D) se reduce a 2 nm. A diferencia de los otros FET empotrados o basados en canales en forma de U, los contactos de la puerta no necesitan formarse en la región empotrada, sino solo en una capa de espaciador para el aislamiento entre las dos partes verticales en ambos lados del canal en U. Sus ventajas estructurales permiten su aplicación a la fabricación de circuitos integrados con mayor integración para distancias integradas extremas entre contactos fuente y drenaje. Las propiedades eléctricas del RGUC FET se investigaron escrupulosamente mediante el estudio de la influencia de los parámetros de diseño, incluida la distancia horizontal entre los contactos S / D, la altura de extensión de la región S / D y el grosor y material de la capa de óxido de la puerta. Las propiedades eléctricas del RGUC FET se verifican mediante simulación cuántica. En comparación con los otros FET de múltiples puertas de canales que no son de planificador, el novedoso RGUC FET es adecuado para una mayor integración.

Introducción

Como uno de los dispositivos más prometedores utilizados en circuitos integrados (IC) a nanoescala, el transistor de efecto de campo sin unión (JL FET) que presenta características eléctricas notables en comparación con los FET de semiconductores de óxido metálico (MOS) convencionales basados en unión, además de su simplicidad de fabricación, ha sido profundamente estudiada en los últimos años [1, 2, 3, 4]. Si bien el aumento del voltaje de la compuerta forma la región de acumulación en el canal, lo que resulta en una mayor corriente [5], la introducción del FET de compuerta múltiple (MG) fortaleció la capacidad de control de la corriente de fuente a drenaje desde el voltaje de compuerta, lo que resulta a propiedades de subumbral mucho mejores del dispositivo. Los FET de puertas múltiples sin unión (JL MG) también se han estudiado ampliamente durante años [6, 7, 8]. Aunque el MOSFET de puerta de canal vertical muestra un I casi ideal - V Rendimiento con un radio de solo varios nanómetros, el canal vertical del mismo hace que el contacto fuente y drenaje no se pueda fabricar en la misma capa, lo que hace que el diseño de los circuitos integrados sea incompatible con la tecnología del planificador. Además, como la fabricación de semiconductores se ha visto obligada a reducir la longitud del canal a menos de 10 nm, los FET MG se enfrentan nuevamente al efecto de canal corto [9,10,11]. Para superar el efecto de canal corto, los MOSFET de canal empotrado se han convertido en un tema candente en los últimos años [12,13,14,15,16]. El trabajo de modelado y simulación de MOSFET de canal empotrado también se lleva a cabo de forma exhaustiva [17,18,19,20]. Un MOSFET de canal empotrado tiene partes de canal vertical planificador debajo de los contactos de fuente y drenaje y una parte de canal plano horizontal. De hecho, prolongó la longitud efectiva del canal en comparación con los MOSFET convencionales con solo el canal plano horizontal. Para el dispositivo con la misma distancia entre la fuente y los contactos de drenaje, puede ser más inmune al efecto de canal corto en comparación con los MOSFET convencionales con canal plano; sin embargo, los datos experimentales muestran que la oscilación subumbral de los MOSFET con canal de receso no puede realizar una oscilación subumbral ideal con una longitud de canal efectiva inferior a 100 nm. Esto se debe a que, aunque la longitud del canal se prolonga, la capacidad de control de la puerta no se refuerza como MG FET. Cabe señalar que es mejor definir un nuevo parámetro geométrico clave relacionado con la descripción de la integración, en lugar de la longitud del canal. La distancia entre la fuente y los contactos de drenaje es más realista y efectiva porque el objetivo final del diseño del dispositivo a nanoescala es lograr el mejor rendimiento en un área de chip determinada limitada, y el tamaño real del dispositivo está relacionado con el ancho del canal. y la distancia entre la fuente y los contactos de drenaje. Con el fin de combinar las ventajas de los FET MG y los MOSFET de canal empotrado, en nuestro trabajo anterior, propusimos FET de puerta en forma de silla de montar con un canal en forma de U [21,22,23], que promueve la capacidad de control de la puerta a la horizontal parte del canal del canal empotrado de un tipo de puerta única plana a un tipo de puerta triple 3-D. Después de eso, actualizamos esta característica de triple puerta 3-D formada no solo en la parte del canal horizontal sino también en ambas partes del canal vertical. Este dispositivo se denomina FET de canal en U de puerta H, y el canal empotrado también se actualiza a un canal de tubo en forma de U 3-D [24]. Como se mencionó anteriormente, el objetivo final del diseño del dispositivo a nanoescala es lograr el mejor rendimiento en un área de chip dada limitada a través de la optimización. Para realizar un dispositivo optimizado de alto rendimiento, tanto la estructura de la puerta como la estructura del canal correspondiente deben estar bien consideradas y diseñadas. También se debe considerar bien la complejidad de fabricación. Los dispositivos mencionados anteriormente, como el dispositivo de canal empotrado, los FET de sillín propuestos anteriormente y los FET de HGUC tienen un terreno común, una estructura sándwich de óxido de puerta / puerta / óxido de puerta debe estar bien formada en la pequeña región empotrada. Esta característica estructural limita su mayor promoción de la integración. Parece que una buena manera de promover la integración es simplificar la característica estructural en la región empotrada y mantener la capacidad de control de la puerta para la parte del canal vertical y la parte del canal horizontal del canal en forma de U al mismo tiempo. Con el fin de realizar estas características y funciones del dispositivo, en este documento, propusimos un novedoso FET de canal en U de puerta rectangular (RGUC FET) para una distancia integrada extrema entre los contactos de fuente y drenaje. Tiene un canal en forma de U que puede prolongar la longitud del canal de efecto sin aumentar la distancia entre la fuente y los contactos de drenaje. En comparación con los otros FET de canal en forma de U, el RGUC FET tiene una estructura interna más simple en la región rebajada del canal en forma de U; a partir de entonces, puede realizar una fabricación más simple en la parte interior de la región empotrada y una distancia más pequeña entre los contactos de fuente y drenaje (mayor integración). La estructura propuesta tiene una mejor capacidad de control de la puerta y una menor corriente de fuga inversa acompañada de una I más alta ACTIVADO / Yo APAGADO proporción. La distancia entre el contacto de la fuente y el contacto de drenaje se puede reducir a menos de 2 nm. Todas las propiedades eléctricas se analizan mediante simulaciones cuánticas.

Métodos

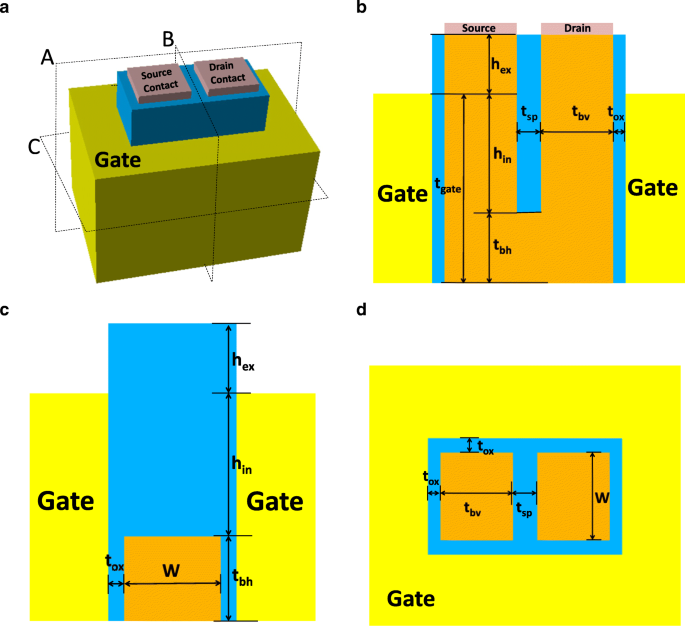

La figura 1a presenta la vista esquemática en 3D del RGUC FET, y las figuras 1b ad son perfiles del dispositivo cortados a través de los planos A, B, C y D que se muestran en la figura 1a. W es el ancho del cuerpo del silicio, t b es el grosor del cuerpo del silicio, h en es la altura interior del espaciador en la región empotrada, h ex es la altura de la fuente de extensión / región de drenaje, t buey es el espesor del óxido de la puerta alrededor del cuerpo de silicio, y t sp es el grosor del espaciador de la capa aislante depositada en la región rebajada del canal en forma de U que equivale a la distancia entre el contacto de la fuente y el contacto del drenaje.

un Vista esquemática 3D del RGUC FET. b Perfiles del dispositivo cortados a través del plano A de a . c Perfiles del dispositivo cortados a través del plano B de a . d Perfiles del dispositivo cortados a través del plano C de a

Dado que el grosor del cuerpo de silicio es inferior a 6 nm, en este artículo se introducen simulaciones cuánticas en lugar de simulaciones clásicas para obtener resultados de simulación más precisos. Todas las simulaciones se realizan utilizando el TCAD de la simulación de dispositivo SILVACO Atlas 3D, utilizando el modelo de movilidad dependiente de la concentración, el modelo Shockley-Read-Hall dependiente de la concentración, el modelo de recombinación Auger, el modelo de estrechamiento de banda prohibida, el modelo estándar de tunelización banda a banda y Modelo de potencial cuántico de Bohm [25]. Los parámetros de simulación se enumeran en la Tabla 1. Las dos partes verticales del cuerpo son en realidad cubos con cuatro lados, cuyas superficies superiores están cubiertas con la fuente o región de drenaje y la superficie inferior están ambas conectadas a la parte horizontal del cuerpo. Los lados triples exteriores de las partes verticales del cuerpo están rodeados por el óxido de la puerta y el contacto de la puerta rectangular, y el otro lado interior está conectado al espaciador interior en la región rebajada. Los cuatro lados del cuerpo horizontal están todos rodeados por el óxido de la puerta y el contacto de la puerta rectangular. Es conjeturable que la puerta rectangular tiene una fuerte capacidad de control de efecto de campo tanto para el cuerpo horizontal como para las dos partes verticales debido a las características de la estructura mencionadas anteriormente. Y, el espaciador interno en realidad prolongó la distancia del camino más corto entre la fuente y los contactos de drenaje en el silicio, lo que podría eliminar el efecto de canal corto que no se puede evitar para los dispositivos de múltiples puertas con características de canal plano. En comparación con otros dispositivos de canal 3-D [21,22,23,24], la estructura propuesta no necesita formación de compuertas en la región empotrada, lo que reduce en gran medida la complejidad de la estructura interna de la región empotrada.

Resultados y discusiones

El modelo de potencial cuántico de Bohm (BQP) calcula un término de energía potencial dependiente de la posición utilizando una ecuación auxiliar derivada de la interpretación de Bohm de la mecánica cuántica. Este modelo se deriva de la física pura y permite que el modelo se aproxime al comportamiento cuántico de diferentes clases de dispositivos, así como de una variedad de materiales. Los efectos del confinamiento cuántico en el rendimiento del dispositivo, incluido I - V características, luego se calcularán con una buena aproximación. Estudios anteriores muestran que la corriente de fuga de la compuerta es insignificante para los casos de óxido de espesor superior a 0,5 nm [7, 26].

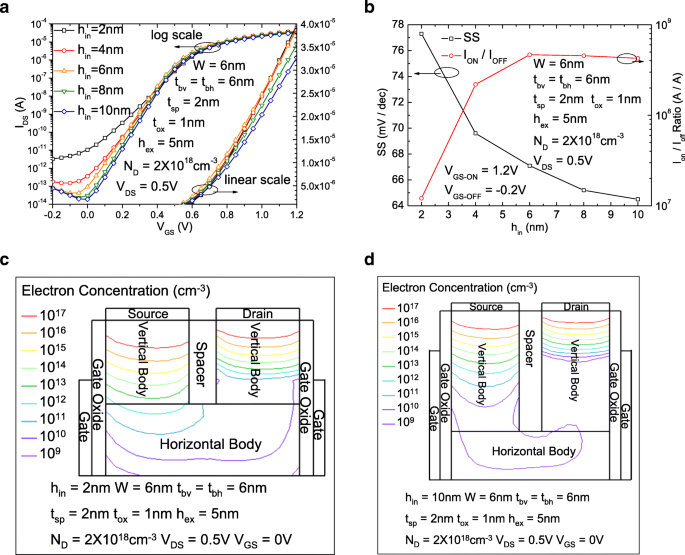

La Figura 2a muestra las comparaciones del voltaje de la fuente de la puerta de la corriente de la fuente de drenaje ( I DS - V GS ) características del RGUC FET con diferentes h en s en escalas logarítmicas y lineales. La Figura 2b muestra las comparaciones de oscilaciones por debajo del umbral (SS) y I ACTIVADO / Yo APAGADO relación del RGUC FET con diferentes h en s. Con el aumento de h en , la trayectoria vertical de todo el canal desde la fuente hasta el drenaje aumenta continuamente, luego la longitud efectiva más corta del canal aumenta gradualmente y el efecto de canal corto se debilita gradualmente y finalmente se elimina. El SS puede alcanzar un valor casi ideal de 65 mV / dec para h en alcanza los 10 nm. El yo ACTIVADO / Yo APAGADO la proporción también aumenta unas 35 veces para h en aumenta de 2 a 10 nm debido a la disminución continua de SS. El prolongado h en hace que la distancia del camino más corto desde la fuente al drenaje aumente de 6 a 22 nm, lo que equivale a 2 h en + t sp y es equivalente a la longitud de canal efectiva de la estructura propuesta. Las figuras 2c yd muestran una distribución de concentración de electrones en 2-D en el cuerpo de silicio en estado apagado para el dispositivo con 2 nm y 10 nm h en , respectivamente. Para el caso de 2 nm, la concentración de electrones más alta en la región horizontal del cuerpo es aproximadamente 10 12 cm −3 y la distancia entre el contacto fuente / drenaje y la región horizontal del cuerpo es muy corta. A partir de entonces, el sesgo de fuente / drenaje afecta seriamente a la distribución de electrones en la región horizontal del cuerpo; la solución es prolongar el canal vertical que mantiene la fuente / drenaje lejos de la región horizontal del cuerpo. Para el caso de 10 nm, en la Fig. 2d, podemos ver que la concentración de electrones más alta en la región horizontal del cuerpo se reduce a 10 9 cm −3 , y hace una región completamente agotada más ideal para el estado apagado que trae un nivel mucho más bajo de corriente de fuga.

un Las comparaciones del I DS - V GS características del RGUC FET con diferentes h en s en escalas logarítmicas y lineales. b Las comparaciones de oscilaciones por debajo del umbral (SS) y I ACTIVADO / Yo APAGADO relación del RGUC FET con diferentes h en s. c Distribución de concentración de electrones 2-D en el cuerpo de silicio en estado apagado para el dispositivo con 2 nm h en . d Distribución de concentración de electrones 2-D en el cuerpo de silicio en estado apagado para el dispositivo con 10 nm h en

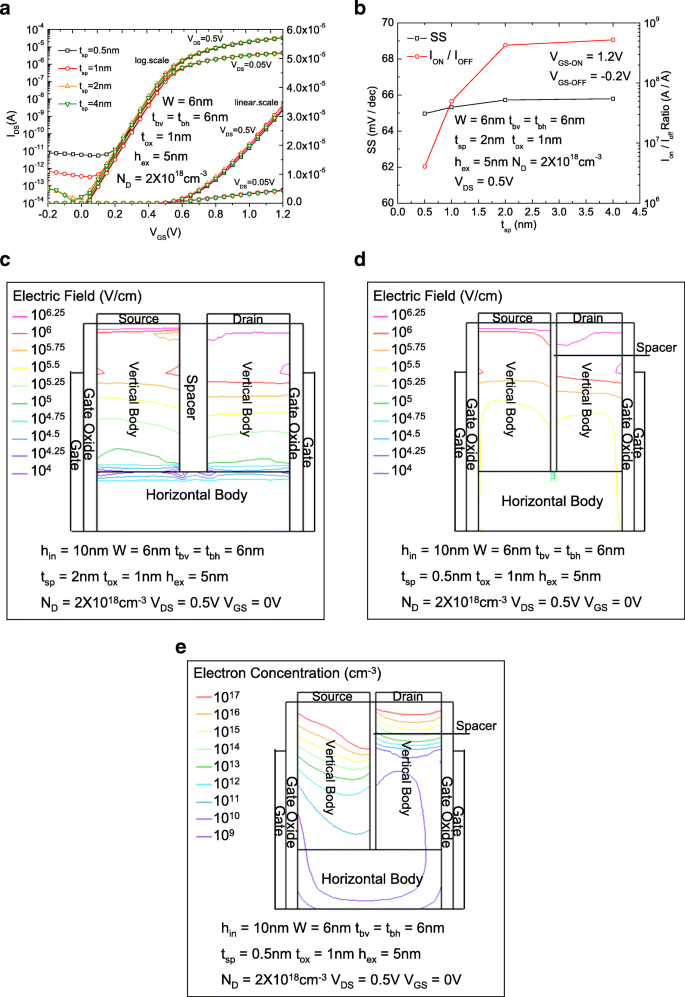

La Figura 3a muestra las comparaciones de I DS - V GS características del RGUC FET con diferentes t sp s en escalas logarítmicas y lineales. La Figura 3b muestra las comparaciones de oscilaciones por debajo del umbral (SS) y I ACTIVADO / Yo APAGADO relación del RGUC FET con diferentes t sp s. Con la disminución de t sp , la distancia entre la fuente y los contactos de drenaje también se reduce continuamente. La corriente de fuga es inducida principalmente por la corriente de túnel de banda a banda. La probabilidad de tunelización es proporcional a la curvatura de la banda, que puede ser equivalente a la intensidad del campo eléctrico en un punto determinado. La corriente de túnel total es la suma de la corriente de túnel generada en cada punto de la región del cuerpo.

un Las comparaciones del I DS - V GS características del RGUC FET con diferentes t sp s en escalas logarítmicas y lineales. b Las comparaciones de oscilaciones por debajo del umbral (SS) y I ACTIVADO / I APAGADO relación del RGUC FET con diferentes t sp s. c Distribución de campo eléctrico 2-D en el cuerpo de silicio en estado apagado para el dispositivo con 2 nm t sp . d Distribución de campo eléctrico 2-D en el cuerpo de silicio en estado apagado para el dispositivo con 0.5 nm t sp . e Distribución de concentración de electrones 2-D en el cuerpo de silicio en estado apagado para el dispositivo con 0,5 nm t sp

La figura 3c y la figura 2d muestran una distribución de campo eléctrico 2-D en el cuerpo de silicio en estado apagado para el dispositivo con 2 nm y 0,5 nm t sp , respectivamente. Para un espaciador de mayor espesor o un voltaje de fuente de drenaje menor ( V DS ), la intensidad del campo eléctrico en la interfaz entre el espaciador en la región empotrada no es lo suficientemente fuerte como para producir una gran cantidad de corriente de fuga. La intensidad del campo eléctrico más fuerte aparece cerca de la interfaz entre el óxido de la puerta y la parte vertical del cuerpo, que se decide por V GD . Sin embargo, si la distancia de la fuente al drenaje se reduce a menos de 1 nm (menos que el espesor del óxido de la puerta), la intensidad de campo más fuerte aparece cerca de la interfaz entre el espaciador en la región empotrada y las dos partes verticales del cuerpo. Puede verse que cuando t sp es inferior a 1 nm, para un V más grande DS (0,5 V por ejemplo), la corriente de fuga es casi independiente de la polarización de la puerta y se decide principalmente por V DS . La SS es casi independiente con t sp y mantiene un valor casi ideal de 65 mV / dec para una h en =Caja de 10 nm hasta el t sp es inferior a 2 nm. El yo ACTIVADO / Yo APAGADO proporción mantiene 10 8 hasta el t sp =2 nm y está seriamente degradado por t sp aparece menos de 2 nm debido al aumento de la corriente de fuga inducido por el fuerte campo eléctrico cerca de la interfaz entre el espaciador en la región empotrada y las dos partes verticales del cuerpo. La intensidad del campo eléctrico del cuerpo de silicio en la región del cuerpo se mejora ampliamente para el t de 0,5 nm. sp caso. La figura 3e muestra la distribución de la concentración de electrones en 2-D en el cuerpo de silicio en estado apagado para el dispositivo con 0,5 nm t sp . En comparación con la Fig. 2d, se ve claramente que la concentración de electrones en la región horizontal del cuerpo aumenta de 10 9 a 10 10 cm −3 . Además, la dimensión del grosor del espaciador de 0,5 nm está muy cerca de una capa de una sola molécula, lo que puede dañar la propiedad de aislamiento de la capa espaciadora hasta cierto punto. Debido a la razón mencionada anteriormente, el t sp se sugiere que sea de 2 nm para un diseño de alta integración y baja fuga y bajo consumo de energía.

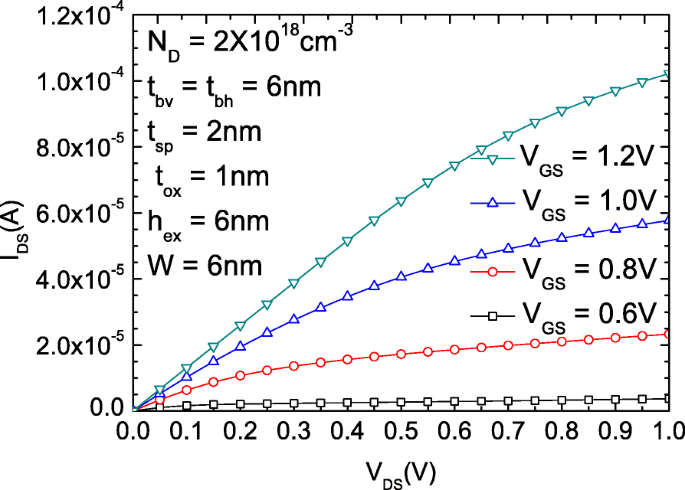

La figura 4 muestra el I DS - V DS del propuesto RGUC FET con estructura optimizada bajo diferentes.

yo DS - V DS característica del RGUC FET propuesto con parámetros de dispositivo optimizados

V GS valores, el SS de los cuales es de aproximadamente 63 mV / dec, y el I ENCENDIDO / I APAGADO es 10 9 ~ 10 10 . La corriente saturada aumenta a medida que V GS aumenta.

Conclusiones

En este documento se propone un nuevo RGUC FET con alta integración y alto rendimiento, que presenta oscilaciones de subumbral bajo y I más alto ACTIVADO / Yo APAGADO proporción. La distancia entre los contactos de fuente / drenaje (S / D) se puede reducir a 2 nm, con características casi ideales como SS, corriente de fuga inversa y I ACTIVADO / Yo APAGADO proporción. Todas las propiedades eléctricas se simulan con modelos cuánticos para garantizar resultados más precisos.

Abreviaturas

- BQP:

-

Potencial cuántico de Bohm

- FET:

-

Transistor de efecto de campo

- h ex :

-

Altura de extensión del espaciador entre la región S / D

- h en :

-

Altura interior del espaciador en la región empotrada

- I APAGADO :

-

Fuera de corriente

- I ACTIVADO :

-

En corriente

- JL:

-

Sin empalmes

- MOS:

-

Semiconductor de óxido de metal

- N D :

-

Concentración de dopaje

- RGUC:

-

Canal en U de puerta rectangular

- S / D:

-

Fuente / drenaje

- SS:

-

Oscilación del subumbral

- t bh :

-

Espesor de cuerpo horizontal

- t bv :

-

Espesor del cuerpo vertical

- t puerta :

-

Longitud vertical de la puerta

- t buey :

-

Espesor de la capa de óxido de puerta

- t sp :

-

Espesor del espaciador entre la región S / D

- V DS :

-

Voltaje de la fuente de drenaje

- V GS :

-

Voltaje de fuente de puerta

- W:

-

Ancho del cuerpo

Nanomateriales

- Diferencia entre estructura y clase:explicada con el ejemplo de C++

- Diferencia entre while y do-while:explicada con ejemplos

- Nanomaterial inteligente y nanocompuesto con actividades agroquímicas avanzadas

- Transistores de efecto de campo de nanoflake SnSe multicapa con contactos au óhmicos de baja resistencia

- Síntesis fácil de nanocables de plata con diferentes relaciones de aspecto y utilizados como electrodos transparentes flexibles de alto rendimiento

- Electrodo de puerta plateado impreso con inyección de tinta y curado por UV con baja resistividad eléctrica

- Resistencia de contacto reducida entre el metal y n-Ge mediante la inserción de ZnO con tratamiento con plasma de argón

- Láseres de nanocables de plasma de canal con cavidades de ranura en V

- Materiales de interfaz térmica asistidos por grafeno con un nivel de contacto de interfaz satisfecho entre la matriz y los rellenos

- Material de cátodo de alto rendimiento de FeF3 · 0.33H2O modificado con nanotubos de carbono y grafeno para baterías de iones de litio

- Sobre la figura de méritos de Baliga (BFOM) Mejora de un nuevo transistor de efecto de campo vertical (FET) de nanopilar GaN con canal 2DEG y Sustrato estampado