Transistores de efecto de campo de nanoflake SnSe multicapa con contactos au óhmicos de baja resistencia

Resumen

Divulgamos monocristales de monoselenuro de estaño (SnSe) de tipo p, cultivados en ampollas de cuarzo de doble sellado utilizando una técnica de Bridgman modificada a 920 ° C. Las mediciones de difracción de rayos X en polvo (XRD) y espectroscopía de rayos X de dispersión de energía (EDX) confirman claramente que el SnSe desarrollado consiste en SnSe monocristalino. El transporte eléctrico de nanoflakes de SnSe multicapa, que se prepararon mediante exfoliación de monocristales a granel, se realizó utilizando estructuras de transistores de efecto de campo (FET) con puertas traseras con contactos de Au y Ti en SiO 2 / Sustratos de Si, revelando que las nanoflakes de SnSe multicapa exhiben características de semiconductores de tipo p debido a las vacantes de Sn en las superficies de las nanoflakes de SnSe. Además, se observó un fuerte efecto de detección de portadores en los FET de nanoflacas de SnSe de 70-90 nm de espesor. Además, el efecto de los contactos de metal en los FET multicapa basados en nanoflacas de SnSe también se analiza con dos metales diferentes, como los contactos de Ti / Au y Au.

Antecedentes

Los calcogenuros metálicos transitorios ofrecen una gama de bandas prohibidas ópticas, que hacen que estos materiales sean adecuados para su uso en diversas aplicaciones ópticas y optoelectrónicas [1]. Películas delgadas de estos materiales, incluidos PbTe, PbSe y Bi 2 Se 3 [2], han atraído una atención considerable debido a su posible uso en dispositivos optoelectrónicos infrarrojos, detectores de radiación, células solares, dispositivos de memoria y dispositivos de grabación holográfica [3, 4, 5, 6, 7, 8]. Mono y diselenuros de estaño (SnSe y SnSe 2 ) han estado en el centro de atención de la investigación debido a sus altos coeficientes de absorción, lo que resulta ventajoso para las aplicaciones optoelectrónicas. Además, estos materiales son prometedores para su uso en aplicaciones termoeléctricas [9,10,11,12,13,14,15,16,17,18,19,20,21,22,23,24]. El monoselenuro de estaño (SnSe) es un semiconductor de tipo p con una banda prohibida para las transiciones indirectas permitidas cercanas a ~ 0,9 eV y para las transiciones directas permitidas cercanas a ~ 1,2 eV, mientras que el diselenuro de estaño (SnSe 2 ) es un semiconductor de tipo n [6]. La estructura cristalina de SnSe es ortorrómbica y sus parámetros de celda unitaria son a =11,496 Å, b =4.151 Å y c =4,444 Å; esta estructura ortorrómbica se transforma en una estructura tetragonal a alta temperatura que, sin embargo, es más baja que el punto de fusión del SnSe 2 [25].

Recientemente, se han investigado ampliamente dispositivos eléctricos de calcogenuro y dicalcogenuro binarios basados en Sn, incluidos transistores de efecto de campo (FET) con una puerta trasera común de área grande. En particular, se ha avanzado mucho en la caracterización de los FET basados en dicalcogenuro de Sn [26, 27]. En 2016, Pei et al . informó un SnSe 2 de pocas capas FET, que demuestra una alta proporción de encendido / apagado de ~ 10 4 con una capa superior de un electrolito polimérico [27]. Guo y col. también informó un SnSe 2 de alta movilidad y pocas capas FET con un espesor de ~ 8,6 nm [28]. A partir de trabajos anteriores, se confirmó que las películas delgadas y de baja concentración de portadores de SnSe producen una alta movilidad y una relación de encendido / apagado de SnSe 2 FET. A pesar de estos esfuerzos para utilizar SnSe 2 sin embargo, no se ha informado de la caracterización eléctrica de los SnSe FET, preparados por exfoliación a partir de monocristales. Una caracterización detallada del transporte eléctrico en SnSe 2 de pocas y múltiples capas Se deben realizar escamas para evaluar las propiedades de transporte eléctrico de los calcogenuros de estaño, como las nanoflakes de SnSe, porque se espera que los cristales individuales de SnSe exhiban una alta movilidad de portador de ~ 7835 cm 2 / V s [29].

En este trabajo, caracterizamos el SnSe monocristalino cultivado utilizando un método de Bridgman modificado. El transporte eléctrico en nanoflake FET multicapa de SnSe preparados por exfoliación de monocristales a granel se caracterizó por primera vez utilizando estructuras FET back-gated en SiO 2 / Sustratos de Si. Además, el efecto de los contactos metálicos en los FET basados en nanoflake de SnSe multicapa también se estudió para dos tipos diferentes de contactos (Ti / Au y Au) porque la función de trabajo del metal de contacto determina la conducción de los portadores de orificios a través de la barrera de Schottky en la interfaz de nanoflake metal-SnSe.

Métodos

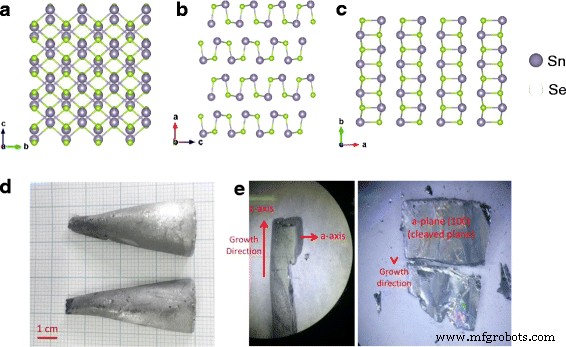

SnSe tiene una estructura cristalina ortorrómbica estratificada a temperatura ambiente [24]. La Figura 1a-c muestra las vistas en perspectiva de la estructura cristalina de SnSe a lo largo de la a , b y c direcciones axiales. Como se muestra en la Fig. 1c, las placas de SnSe con una capa de dos átomos están ranuradas, mientras que la escisión fácil en los cristales ocurre a lo largo del plano (100) (Fig. 1b). Los cristales individuales de SnSe se cultivaron utilizando el método de Bridgman modificado, como se describió anteriormente [24, 30]. Cantidades estequiométricas de Sn (99,999% de granalla, Alfa Aesar) y Se (99,999% de polvo, Alfa Aesar) se fundieron primero en un lingote (~ 20 g) en una ampolla de cuarzo con doble sellado. Las materias primas se calentaron lentamente a 500 ° C y se dejaron reposar durante 10 h, luego se mantuvieron a 920 ° C durante 10 h adicionales antes de apagar el horno. El lingote obtenido se trituró en polvo y se introdujo en un tubo de cuarzo en forma de cono, se evacuó y se selló a la llama. Este tubo de cuarzo con forma de cono cargado se colocó en un tubo de cuarzo más grande. El tubo exterior se llenó con Ar gaseoso para evitar la explosión y la oxidación, y luego se selló a la llama. La ampolla de cuarzo cargada se colocó en la posición en la que el gradiente de temperatura era mayor en el horno de tubo vertical. El horno de tubo vertical se calentó lentamente a 970 ° C durante 20 h, se mantuvo durante 10 hy luego se enfrió a 830 ° C a una velocidad de 0,5 ° C / h. El horno se mantuvo a 830 ° C durante 24 h más y luego se enfrió a 500 ° C a una velocidad de 100 ° C / h antes de apagar el horno.

un - c Estructura cristalina de cristales de SnSe a lo largo de a -, b - y c -direcciones axiales. d Fotografía de un SnSe monocristalino crecido. e Fotografías de cristales de SnSe escindidos a lo largo de la a plano del eje (100). Vistas superiores del plano escindido (100) del monocristal de SnSe ( imagen derecha en d )

Resultados y discusión

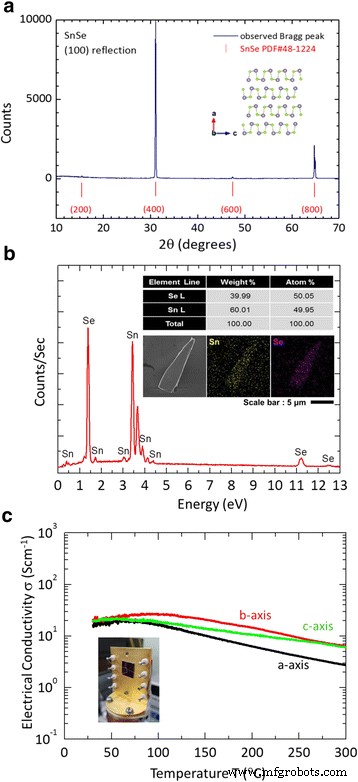

Se obtuvo un cristal de SnSe en forma de cono (diámetro, 30 mm; longitud, 70 mm) y se muestra en la Fig. 1d-e. El cristal obtenido se dividió en dos piezas debido a una fisura que se produjo durante la extracción del cristal de la ampolla de cuarzo (Fig. 1d). La calidad de los cristales de SnSe crecidos se comprobó utilizando un difractómetro de rayos X en polvo (XRD, New D8-Advance, Bruker-AXS, Alemania) con Cu Kα ( λ =1,5406 Å). La Figura 2a muestra el patrón XRD del archivo de difracción de potencia (PDF) 48-1224 para SnSe ortorrómbico, junto con el patrón para la a cristalográfica eje, que es perpendicular al plano escindido (100) del cristal de SnSe. Como se muestra en la Fig. 2a, el patrón XRD de SnSe monocristalino sugiere fuertemente un cristal ortorrómbico monofásico con un grupo espacial Pnma [31], lo que indica una fuerte orientación preferida con (h00) reflejos, lo que concuerda con un informe anterior [32]. Además, los picos predominantes fueron (400) y (800), a 2 θ = 31.081 ° y 64.818 °, respectivamente, como se muestra en la Fig. 2a [33]. Como se muestra en la Fig. 2b, la espectroscopia de rayos X de dispersión de energía (EDX) reveló la relación atómica Sn:Se de 1:1, lo que confirma la relación estequiométrica de Sn y Se (recuadro de la Fig. 2b). Los recuadros de la Fig. 2b también muestran una imagen de microscopía electrónica de barrido (SEM) y mapeo EDX de una nanoflake FET de SnSe con un grosor de dispositivo de 90 nm. Este resultado concuerda bien con informes anteriores [24, 33]. Además, se midió la conductividad eléctrica del SnSe monocristalino (recuadro de la Fig. 2b) para temperaturas que oscilaban entre 30 y 300 K, utilizando el método convencional de sonda de cuatro puntos. La Figura 2c muestra la conductividad eléctrica dependiente de la temperatura de los monocristales de SnSe a lo largo de tres direcciones cristalográficas diferentes, lo que indica comportamientos similares dependientes de la temperatura y comportamientos de anisotropía debido a las diferentes movilidades de los orificios en SnSe a lo largo de las diferentes direcciones axiales. Como se muestra en la Fig. 2c, la conductividad eléctrica a lo largo de b - y c -eje a 300 K se determinó en ~ 6.00 S cm −1 , que es ~ 2,2 veces más grande que el de a -eje (~ 2,7 S cm −1 ). Este resultado concuerda bien con los resultados anteriores para el SnSe monocristalino [24]. En la figura 2c, se muestra la conductividad eléctrica dependiente de la temperatura del SnSe monocristalino para el rango de semiconductores (30–100 K) y para el rango metálico (> 100–300 K). Por encima de 100 K, los cristales de SnSe crecidos exhibieron un comportamiento de transporte metálico, consistente con observaciones previas [24].

un Patrón XRD de monocristales de SnSe, que muestra una difracción clara (h00). b Espectro EDX de los monocristales de SnSe . Recuadro muestra la información detallada de la relación atómica de Sn y Se. Inserciones exhiben una imagen SEM y mapeo EDX de una nanoflake FET de SnSe con un grosor de dispositivo de 90 nm. c Conductividad eléctrica dependiente de la temperatura de los monocristales de SnSe, para temperaturas que oscilan entre 30 y 300 K, medida con el método de sonda de cuatro puntos

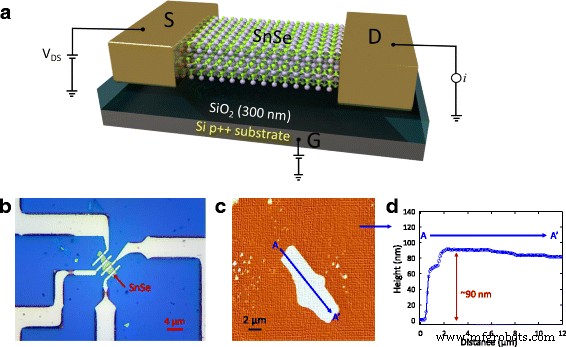

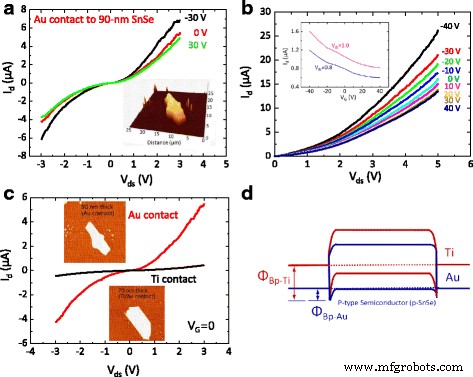

Los dispositivos SnSe FET se fabricaron como sigue. En primer lugar, se exfoliaron mecánicamente nanoflakes de SnSe sobre un SiO 2 de 300 nm de espesor / p ++ Sustrato de Si a partir de cristales individuales de SnSe, que se escinde fácilmente en el plano (100) utilizando el conocido método de cinta adhesiva (Fig. 1e) [26, 27, 34]. Las mediciones del transporte eléctrico en FET de nanoflakes de SnSe individuales preparadas se realizaron a temperatura ambiente en la configuración de FET de puerta trasera. La Figura 3a muestra esquemáticamente dispositivos FET basados en nanoflacas de SnSe con una puerta trasera de área grande. En este estudio, se prepararon dos nanoflakes de SnSe (nanoflakes de SnSe de 70 y 90 nm de espesor) en el SiO 2 / Sustrato de Si. Los FET de SnSe se fabricaron utilizando el método estándar de litografía por haz de electrones seguido de dos tipos de metalización, es decir, Au (grosor, 100 nm) y Ti / Au (grosor, 10/100 nm) se consideraron contactos óhmicos en nanoflakes de SnSe. Antes del proceso de metalización, se realizó un grabado con óxido tamponado (BOE) para eliminar el polímero y los residuos de óxido en las superficies de las nanoflakes. La Figura 3b muestra una imagen óptica de un nanoflake FET de SnSe con un grosor de dispositivo de 90 nm. Los espesores de las nanoflakes de SnSe se midieron utilizando un microscopio de fuerza atómica (AFM) a temperatura ambiente (Fig. 3c-d). Como se muestra en la Fig. 3b y en el recuadro de la Fig. 2b, el SnSe FET fabricado de 90 nm de espesor tenía la longitud del canal ( L ) de 5 μm y ancho ( W ) de 4,71 μm, mientras que para el SnSe FET L de 70 nm de espesor era de 5 μm y W era de 6 µm. Toda la corriente-voltaje ( I - V ) se midieron las características utilizando un analizador de parámetros de semiconductores (HP 4155C, Agilent Technologies, EE. UU.) en una estación de sonda blindada eléctricamente a temperatura ambiente. La Figura 4a muestra la corriente de drenaje ( I d ) en función del voltaje de la puerta ( V g ), para el nanoflake de SnSe de 90 nm de espesor, para los voltajes fuente-drenaje ( V ds ) de −30, 0 y 30 V, a temperatura ambiente, lo que indica un claro comportamiento de semiconductor tipo p, que se atribuye principalmente a las vacantes de Sn, como se informó anteriormente [15, 16, 22, 24, 35,36,37 , 38,39]. El resultado de la Fig. 4a implica que se espera que el AU metálico con su alta función de trabajo forme contactos óhmicos débiles en nanoflakes de SnSe, lo que indica una barrera de Schottky más baja para la banda de conducción de las nanoflakes de SnSe. Más adelante se proporcionará una discusión más detallada sobre las funciones de trabajo de diferentes metales. La figura 4b muestra I d frente a V ds para diferentes V g , que van desde −40–40 V, en pasos de 10 V. De la Fig. 4b, la movilidad del agujero ( μ p ) se determina en ~ 2,7 cm 2 / V s, obtenido de μ p = t m [ L ⁄ ( WC buey V ds)], donde t m es la transconductancia (= dI d / dV g =2,89 × 10 - 8 A / V ), L es la longitud (~ 5,1 μm), W es el ancho (~ 4,75 μm), V ds es el voltaje de la fuente de drenaje (~ 1 V) del SnSe FET, y C buey (= ε r ε 0 / d =11,5 nF / cm 2 ) con ε r (la constante dieléctrica) de 3.9 y d (el grosor de la capa de óxido) de 300 nm es la capacitancia por unidad de área del FET de nanoflake de SnSe con puerta trasera. La movilidad del orificio evaluada de los FET de nanoflake de SnSe exfoliados mecánicamente es mucho menor que la de las películas delgadas de SnSe epitaxial (~ 60 cm 2 / V s) preparado por deposición de láser pulsado sobre sustratos de MgO utilizando dianas ricas en Se [40]. Sin embargo, el valor obtenido aquí es ~ 1,8 veces mayor que el obtenido para nanoplacas de SnSe monocristalino (~ 1,5 cm 2 / V s) [33]. Una movilidad de orificios relativamente baja puede atribuirse a una fuerte dispersión de fonones debido a las vacantes de Sn en la superficie de SnSe [18, 36, 41, 42] y una barrera de Schottky relativamente alta en la interfaz de nanoflake de metal de Au-SnSe.

un Esquema de un nanoflake FET de SnSe exfoliado mecánicamente en un SiO 2 / p ++ Sustrato de Si. b Imagen óptica de un nanoflake FET de SnSe fabricado que se utilizó para mediciones de transporte eléctrico. c Imagen AFM de una nanoflaca de SnSe en un SiO 2 / Sustrato de Si. d Perfil de altura AFM de un nanoflake de SnSe, para estimar el grosor y fabricar dispositivos FET

un Drenar corriente ( I d ) en función del voltaje de fuente-drenaje aplicado ( V ds ), para los voltajes de la puerta ( V g ) de -30, 0 y 30 V, para un FET de nanoflacas de SnSe de 90 nm de espesor, a temperatura ambiente. b yo d frente a V ds para V g que van desde -40–40 V en pasos de 10 V, para el FET de nanoflacas de SnSe de 90 nm de espesor. El recuadro muestra I d frente a V g para V ds de 0,8 y 1,0 V, medidos a temperatura ambiente. c yo d frente a V ds sin sesgos V g (=0) para contactos de Au y Ti en un nanoflake FET de SnSe. El recuadro muestra una imagen escaneada por AFM de nanoflakes de SnSe. d Esquemas de los diagramas de bandas de energía de dos metales, Au y Ti, en semiconductores de SnSe de tipo p

Además, observamos un ajuste de puerta débil de la conductancia en la región de agotamiento del I d frente a V ds curva (Fig. 4c) y una relación de encendido / apagado de corriente baja (~ 2 en V ds de 1 V, insertos de la Fig. 4c) en el FET de nanoflake de p-SnSe con contactos de metal de Au. Se informó un comportamiento similar para otros materiales semiconductores bidimensionales (2D) con un grosor similar, incluidos SnS FET (grosor, ~ 50-80 nm) [43], nanoplacas de SnSe de ~ 15,8 nm de grosor [33], ~ 80 -nm de espesor MoS 2 [44] y SnSe 2 de ~ 84 nm de espesor [26]. Estos comportamientos pueden explicarse por el efecto de longitud de pantalla del portador finito debido a la existencia de una capa superficial conductora en dispositivos FET con espesores mayores que la longitud de pantalla \ (\ left (\ sqrt {\ varepsilon {K} _B T} {e } ^ 2 p \ right) \), donde ε , K B y p son la constante dieléctrica del semiconductor, la constante de Boltzmann y la densidad del portador de huecos, respectivamente, [43].

Los contactos metálicos determinan de manera importante las características de los dispositivos FET 2D [45]. Para determinar el efecto de las funciones de trabajo del metal en SnSe, consideramos Au (función de trabajo, ~ 5,1 eV) y Ti (función de trabajo, ~ 4,3 eV) como contactos de metal en nanoflakes de SnSe. La figura 4c muestra una I típica d frente a V ds curvas sin modulación de puerta ( V g =0) para los FET de nanoflake de SnSe con contactos de Au y Ti, lo que indica una mayor resistencia general para Ti (~ 15,4 MΩ) en comparación con la de Au (~ 0,56 MΩ). Por tanto, la barrera de Schottky en la interfase metal-SnSe es mayor para el Ti (Fig. 4c). Este comportamiento siempre se observa en todos los SnSe FET con contactos Ti. Como se muestra en la Fig. 4d, la altura de la barrera Schottky para agujeros aumenta a medida que disminuye la función de trabajo del metal. Por lo tanto, metales como Pd, Au y Pt, con grandes funciones de trabajo, pueden ser adecuados como contactos óhmicos en FET de nanoflake de p-SnSe porque para estos metales, la altura de la barrera Schottky para la inyección de orificios será menor. La resistencia de contacto debe medirse para metales adicionales, para determinar su idoneidad como contactos de metal en nanoflake de SnSe. Este problema se está abordando actualmente mediante el método de longitud de transferencia.

Conclusiones

En resumen, se cultivaron nanoflakes de SnSe multicapa, se exfoliaron y se caracterizaron para los canales de SnSe FET con una estructura de FET back-gated en SiO 2 / Sustratos de Si. Las mediciones de transporte eléctrico demostraron que las nanoflakes de SnSe multicapa con contactos de metal Au exhiben características de semiconductores de tipo p con una barrera Schottky relativamente baja y una baja resistencia de contacto en los FET de nanoflake de SnSe exfoliados. Además, enfatizamos que este estudio es el primero en reportar FET a base de nanoflake de SnSe exfoliados mecánicamente y estamos seguros de que nuestros FET de nanoflake de SnSe son muy prometedores para dispositivos eléctricos 2D, así como para aplicaciones de recolección de energía, incluida la generación futura de termoelectricidad. .

Nanomateriales

- Transistores, efecto de campo de unión (JFET)

- Transistores, efecto de campo de puerta aislada (IGFET o MOSFET)

- Transistores de efecto de campo de unión

- Transistores de efecto de campo de puerta aislada (MOSFET)

- Introducción a los transistores de efecto de campo de unión (JFET)

- Introducción a los transistores de efecto de campo de puerta aislada

- Separadores de aire para chips de 10 nm

- Un salto nanométrico a billones de transistores

- Aprendizaje no supervisado con neuronas artificiales

- Efecto del tratamiento de recocido in situ sobre la movilidad y morfología de transistores de efecto de campo orgánico basados en TIPS-pentaceno

- Deposición en dos pasos de ZnO dopado con Al en p-GaN para formar contactos óhmicos