Estudio de simulación del transistor de efecto de campo de túnel de doble puerta con espesor de canal de paso

Resumen

Se espera que el transistor de efecto de campo de túnel de doble puerta (DG TFET) amplíe las limitaciones de la corriente de fuga y la pendiente por debajo del umbral. Sin embargo, también sufre el comportamiento ambipolar con la arquitectura simétrica de fuente / drenaje. Para superar la corriente ambipolar, se debe introducir una asimetría entre la fuente y el drenaje. En este artículo, investigamos el rendimiento de DG TFET con espesor de canal de paso (SC TFET) utilizando la simulación 2D. La asimetría entre fuente y drenaje se introduce a través del espesor del canal escalonado; por tanto, se espera que se alivie el comportamiento ambipolar. Los resultados muestran que el SC TFET presenta una reducción significativa de la corriente ambipolar en comparación con el DG TFET convencional. Los mecanismos de SC TFET se analizan a fondo para explorar la percepción física. Los impactos introducidos por los parámetros de la estructura en el voltaje de inicio, pendiente subumbral, corriente de drenaje en estado encendido y estado ambipolar también se exhiben para determinar la estructura óptima.

Antecedentes

A medida que continúa el proceso de escalado extremo, la tecnología CMOS con MOSFET convencional se enfrenta a varios desafíos, como el aumento de la corriente de fuga y la pendiente del subumbral ( SS ). Se espera que el transistor de efecto de campo de túnel (TFET), que utiliza los mecanismos de tunelización de banda a banda (BTBT), amplíe las limitaciones de la corriente de fuga y SS [1,2,3,4,5,6,7,8]. TFET basado en silicio muestra ventajas como alta confiabilidad y bajo costo. Sin embargo, el TFET convencional basado en silicio exhibe una corriente relativamente baja en comparación con el MOSFET debido a la tasa de BTBT restringida [9,10,11]. Para desarrollar el potencial del TFET basado en silicio, se han propuesto recientemente varias estructuras TFET novedosas para mejorar la corriente en estado. El TFET de doble puerta (DG TFET) muestra una tasa BTBT mejorada, lo que conduce a una mejora en la corriente [12,13,14]. Sin embargo, la corriente ambipolar de DG TFET también aumenta ya que la mejora de la tasa de BTBT también se activa en el estado ambipolar [15]. Para superar aún más la corriente ambipolar, debe introducirse una asimetría entre la fuente y el drenaje [16]. Los DG TFET con una superposición de drenaje en la compuerta y una menor concentración de dopaje en el drenaje son métodos habituales para aliviar el problema ambipolar [17,18,19]. Pero el traslapo puerta-drenaje requiere una mayor distancia S / D y una menor concentración de dopaje en el drenaje aumenta las resistencias en serie [15]. Un trabajo anterior ha demostrado que los efectos ambipolares en el TFET con drenaje debajo del traslapo podrían aliviarse aún más mediante el uso de espaciadores de baja k y colocando los contactos en la configuración superior e inferior [15], lo que sugiere que las estrategias de asimetría combinadas podrían ser significativas en mejorar el rendimiento del TFET. En nuestro trabajo anterior, se ha demostrado que el FinFET con ancho de aleta de asimetría mejora el rendimiento de FinFET [20]. También se cree que el espesor del canal t si tiene un impacto significativo en la tasa BTBT de la DG TFET [21]; por lo tanto, la asimetría entre el espesor de la fuente y el espesor del drenaje podría aliviar aún más la corriente ambipolar y debe estudiarse a fondo.

En este artículo, investigamos las diversas actuaciones de DG TFET con espesor de canal escalonado (SC TFET), la asimetría entre la fuente y el drenaje se introduce a través del espesor del canal escalonado de modo que se espera que se reduzca la corriente ambipolar. El resto de este documento está organizado de la siguiente manera:La Sección 2 presenta la estructura del dispositivo y la configuración de la simulación. En la Sección 3, se analizan en profundidad los mecanismos del SC TFET. La discusión detallada sobre los impactos de los parámetros de la estructura en las curvas de transferencia, voltaje de inicio ( V inicio ), SS promedio y la corriente de drenaje en estado encendido / ambipolar también se presenta. Finalmente, los hallazgos de este documento se aclaran en la sección IV.

Estructura y simulación

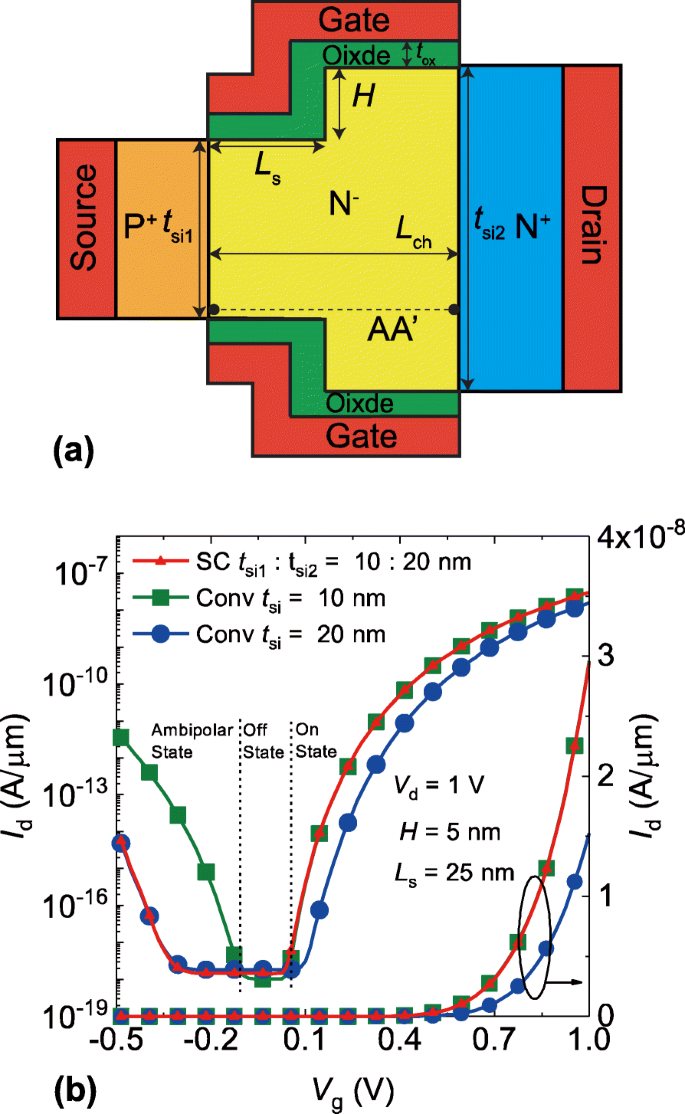

El diagrama esquemático del SC TFET considerado en este artículo se muestra en la Fig. 1a. El espesor del canal cerca de la región de origen no es igual al espesor del canal cerca de la región de drenaje. El grosor del canal cambia gradualmente en un punto determinado de la región del canal. La altura del escalón y la posición del escalón se indican como H y L s respectivamente. t si1 y t si2 son el espesor del canal cerca de la región de origen y la región de drenaje, respectivamente. El espesor de óxido efectivo (EOT) es de 1 nm en nuestra simulación. La región de origen está altamente dopada p (10 20 átomos / cm 3 ) y la región de drenaje está altamente dopada con n (10 20 átomos / cm 3 ) para reducir la resistencia en serie [15], la región del canal está ligeramente dopada con n (10 17 átomos / cm 3 ). Para analizar el voltaje de inicio con varias configuraciones de espesor de canal, la función de trabajo de la puerta de metal se fija en 4.5 eV, la longitud de la puerta es igual a la longitud del canal L ch y ajustado a 50 nm [22,23,24,25]. Las simulaciones se llevan a cabo utilizando Sentaurus TCAD versión I-2013.12 [26, 27]. El modelo de dependencia del dopaje y el modelo de movilidad dependiente del campo son el modelo de movilidad unificado de Philips y el modelo de movilidad Lombardi, respectivamente. También se utilizan las estadísticas de Fermi-Dirac, el modelo de recombinación de Shockley-Read-Hall y Auger. Para tener en cuenta las regiones de fuente / drenaje altamente dopadas, se activa el modelo de estrechamiento de la banda prohibida. El modelo BTBT no local basado en la aproximación de Wentzel-Kramer-Brillouin (WKB) sintonizada con los resultados experimentales de [28] y el modelo de cuantificación de gradiente de densidad permiten lograr una simulación precisa [29, 30]. El voltaje de inicio se define como el voltaje de puerta en el que la pendiente del subumbral es máxima. El SS promedio se extrae de la corriente fuera de estado a I d =10 −11 A / μm.

un Diagrama esquemático 2D del SC TFET, t si1 y t si2 son el espesor del canal cerca de la región de la fuente y la región de drenaje, obviamente se introduce la asimetría entre la fuente y el drenaje. Línea de corte AA 'es la línea de corte a lo largo de la dirección horizontal. La distancia vertical entre la línea de corte y la superficie de la región fuente es de 0,5 nm. b Transferencia de curvas de la SC TFET y las DG TFET convencionales en escala logarítmica y lineal

Resultados y discusión

Mecanismo y curvas de transferencia

La Figura 1b muestra las curvas de transferencia de SC TFET y DG TFET convencional en escala logarítmica y lineal, respectivamente. En la figura 1b, marcamos el estado activado, el estado desactivado y el estado ambipolar. Para TFET, siempre se desea una corriente más alta de estado activado y una corriente más baja de estado ambipolar, lo que requiere que el V inicio y SS debe ser bajo mientras que el estado apagado debe tener un amplio rango de voltaje. Como se muestra en la Fig. 1b, la V inicio del DG TFET convencional con un grosor de canal de 10 nm son inferiores a los del DG TFET con un grosor de canal de 20 nm. El V extraído inicio de la DG TFET con t si =10 nm es 0.04 V y su promedio extraído es SS es 44,8 mV / dec, el V inicio y el promedio de SS de la DG TFET convencional con t si =20 nm es 0,1 V y 50,6 mV / dec, respectivamente. La corriente de drenaje del DG TFET convencional con t si =10 nm se mejora en un 94,7% en comparación con el DG TFET convencional con t si =20 nm. La razón principal de esta mejora de la corriente de drenaje es la reducción de SS y V inicio . Sin embargo, el rango fuera del estado de la DG TFET convencional con t si =10 nm es solo 0,17 V. El DG TFET convencional con t si =20 nm, en comparación, exhibe un rango de estado desactivado de 0,45 V. Como resultado, la corriente de estado ambipolar del DG TFET convencional con t si =20 nm se reduce en 3 órdenes de magnitud en comparación con el DG TFET convencional con t si =10 millas náuticas.

Para una comparación justa, el t si1 y t si2 de SC TFET son iguales a los espesores de canal de los DG TFET convencionales anteriores, respectivamente. El grosor del canal más estrecho t si1 de SC TFET es de 10 nm y el grosor de canal más ancho t si2 de SC TFET es de 20 nm. La posición del paso se asume en el medio del canal y la L s es de 25 nm. Se puede observar que el SC TFET muestra características prometedoras, incluida la alta corriente de drenaje en el estado activado, así como en el estado desactivado de amplio rango. La corriente de drenaje de SC TFET en el estado encendido es similar en comparación con el DG TFET convencional con t si =10 nm, el SS promedio es de 45,8 mV / dec y el V inicio es 0.03 V. Sin embargo, el rango de estado desactivado de SC TFET se mejora hasta un 123.5% y la corriente de estado ambipolar también se reduce en 3 órdenes de magnitud en comparación con el DG TFET convencional con t si =10 nm. Como resultado, las características en estado de SC TFET son similares a las del DG TFET convencional con un espesor de canal estrecho, el SC TFET también muestra curvas apagadas / ambipolares casi paralelas al DG TFET convencional con un ancho de canal ancho. Por lo tanto, el SC TFET puede lograr un SS bajo , V reducido inicio y un amplio rango fuera del estado simultáneamente.

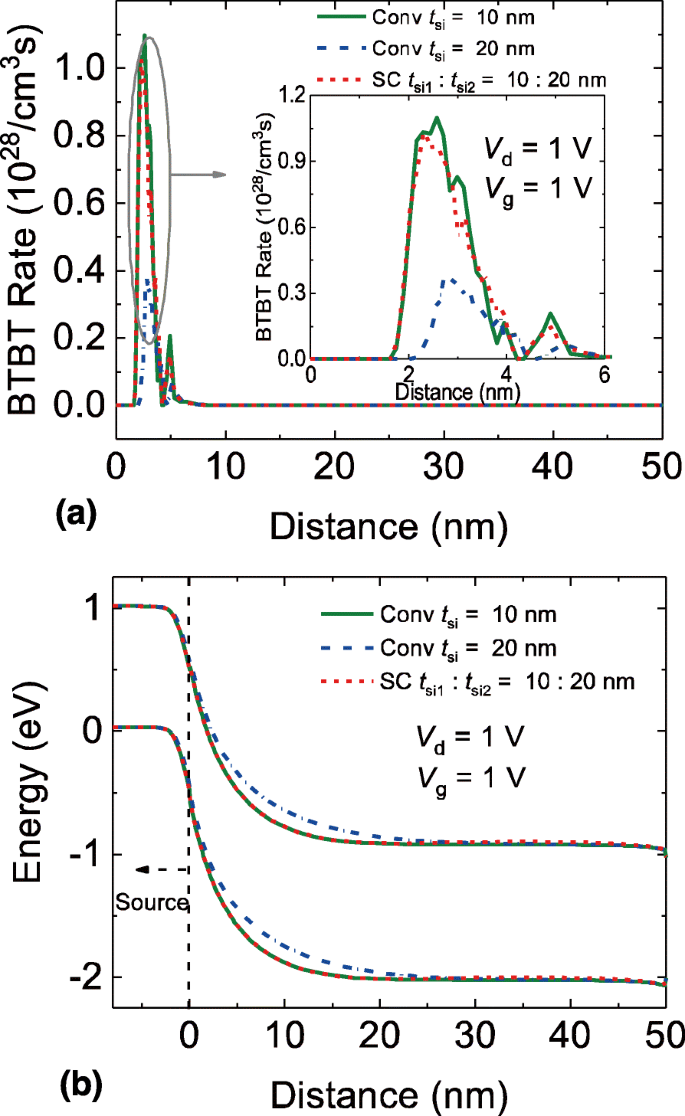

Para explorar el mecanismo físico del SC TFET, comparamos las tasas de BTBT y los diagramas de bandas de energía en el estado activado, el punto de inicio cercano y el estado ambipolar, respectivamente. La Figura 2a muestra las tasas BTBT del SC TFET y los DG TFET convencionales. Puede verse que la tasa de BTBT depende en gran medida del grosor del canal. De hecho, la relación entre el espesor del canal y la corriente BTBT I BTBT se puede expresar como [31].

$$ {I} _ {BTBT} \ propto \ exp \ left (- \ frac {4 \ lambda \ sqrt {2 {m} ^ {\ ast} {E_g} ^ {2/3}}} {3 \ mathrm {\ hslash} \ left (\ Delta \ Phi + {E} _g \ right)} \ right) $$ (1)

un Tarifas BTBT y b Diagrama de bandas de energía del SC TFET y los DG TFET convencionales en el estado activado, la distancia es la posición lateral de la línea de corte AA 'en la Fig. 1

Donde λ =( ε si t si t buey / 2 ε buey ) 1/2 es la longitud natural, ε si y ε buey son la permitividad de silicio y óxido respectivamente y t buey es el espesor del óxido. Δ Φ es el rango de energía en el que se pueden realizar túneles, E g es la banda prohibida en el cruce del túnel y m * es la masa de tunelización. La ecuación (1) indica que I BTBT debería aumentar como t si reduce. Por lo tanto, la tasa BTBT de DG TFET convencional con t si =10 nm debería ser mayor que el del DG TFET convencional con t si =20 nm. El SC TFET muestra una distribución similar de la tasa BTBT al DG TFET convencional con t si =10 nm. Esto se debe a que el BTBT ocurre principalmente cerca de la unión de la fuente en el estado activado, por lo tanto, el grosor del canal cerca de la unión de la fuente determinará la tasa de BTBT en el estado activado. La Figura 2b muestra el diagrama de bandas de energía del SC TFET y los DG TFET convencionales. Dado que la tasa de BTBT está fundamentalmente relacionada con la distancia de tunelización, el diagrama de bandas de energía, que puede presentar la distancia de tunelización con claridad, explicará el origen de la variación de las tasas de BTBT. En la Fig. 2b, la distancia mínima de tunelización del SC TFET se encuentra cerca de la unión de la fuente y es más o menos igual a la del DG TFET convencional con t si =10 nm. La distancia mínima de túnel de DG TFET convencional con t si =20 nm es significativamente más ancho; por lo tanto, su tasa de BTBT se reduce en comparación con el SC TFET y el DG TFET convencional con un espesor de canal más delgado.

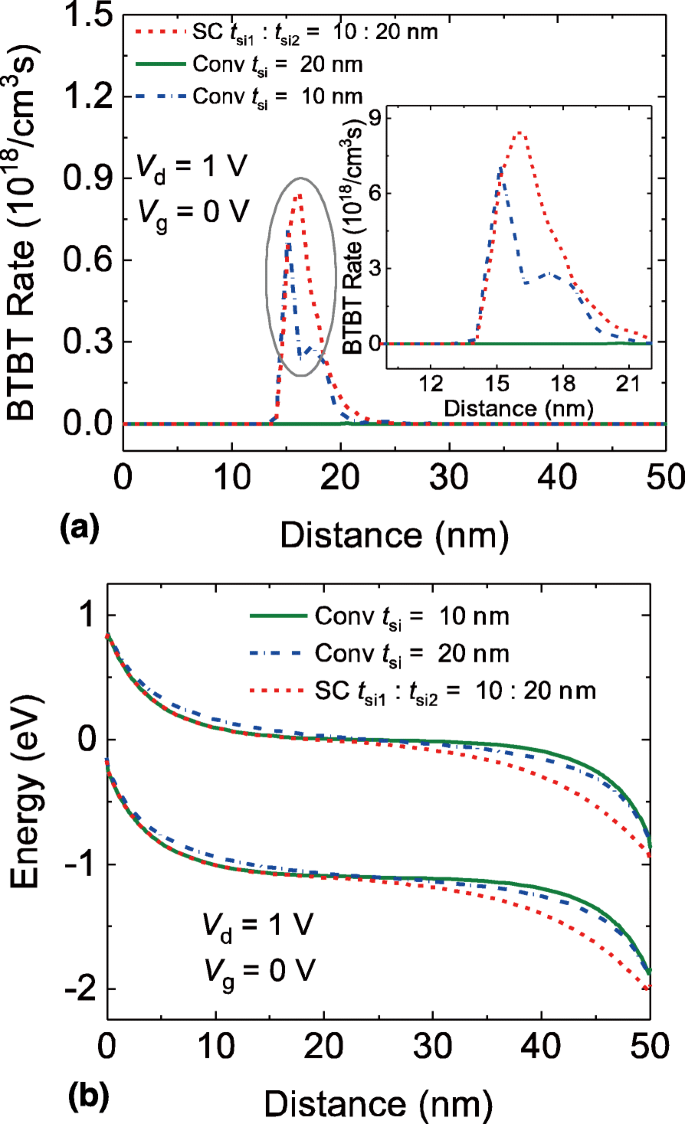

La Figura 3a muestra las tasas de BTBT cuando el voltaje de la puerta es cero y está cerca del voltaje de inicio. Se puede ver que el SC TFET posee la tasa BTBT más alta, seguido por el DG TFET convencional con t si =10 nm. El DG TFET convencional con t si =20 nm muestra la tasa BTBT más baja. La figura 3b muestra el diagrama de bandas de energía correspondiente. Se puede observar que la ubicación de la distancia mínima desde la banda de valencia a la banda de conducción está en el centro de la región del canal. Además, la distancia mínima del DG TFET convencional con un grosor de canal más ancho es mayor que la del SC TFET y la del DG TFET convencional con un grosor de canal más delgado. Indica que el grosor del canal también tiene un impacto significativo en la tasa de BTBT en el punto de inicio. Por lo tanto, la V inicio también depende del grosor del canal. Otro hecho es que el SC TFET presenta una tasa de BTBT mayor que el del DG TFET convencional con t si =10 nm aunque sus espesores mínimos de canal sean iguales. Este fenómeno se atribuye a la variación de la distribución de potencial introducida por la esquina del electrodo de puerta, como también se puede observar en otros trabajos [32, 33]. Como resultado, el SC TFET muestra el V más bajo inicio , seguido del DG TFET convencional con un grosor de canal delgado, y el DG TFET convencional con un grosor de canal ancho presenta el V más alto inicio .

un Tarifas BTBT y b Diagrama de bandas de energía del SC TFET y los DG TFET convencionales en el punto de inicio cercano, la distancia es la posición lateral de la línea de corte AA 'en la Fig. 1

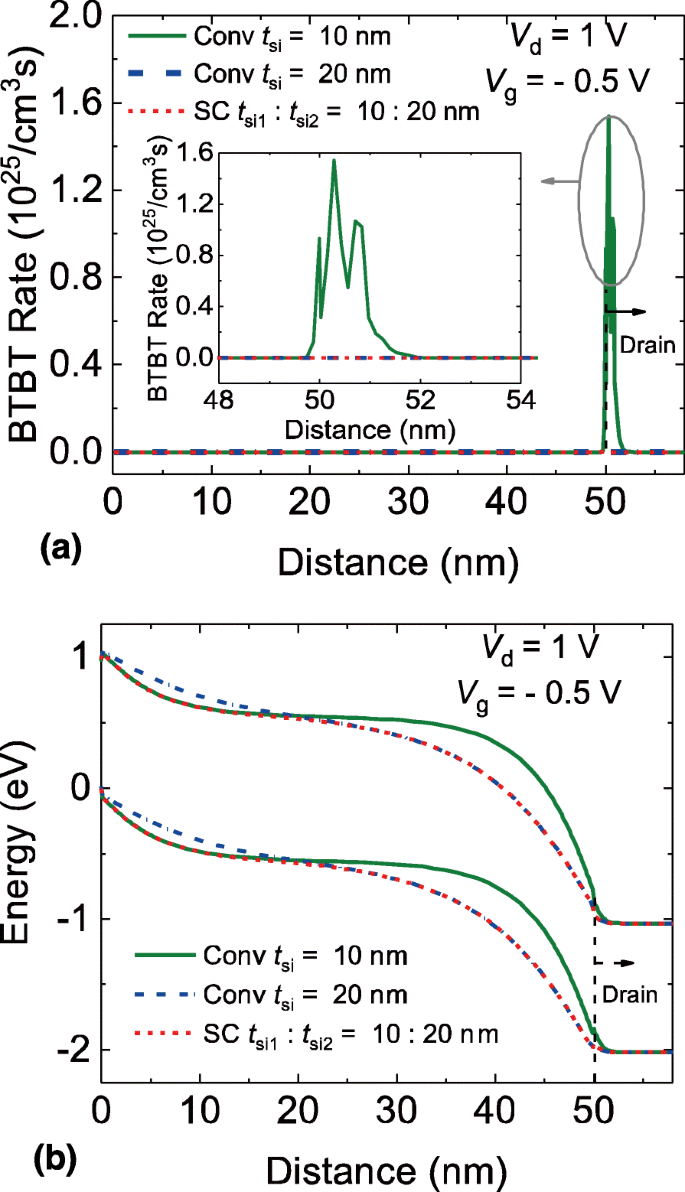

La figura 4a muestra la comparación de las tasas de BTBT en el estado ambipolar. Dado que la tasa de BTBT depende en gran medida del grosor del canal, el TFET convencional con t si =10 nm muestra la tasa BTBT más significativa en comparación con las otras dos estructuras TFET. El SC TFET, sin embargo, muestra la tasa BTBT similar al DG TFET convencional con t si =20 nm. Esto se debe a que la formación de túneles se genera principalmente cerca de la región de drenaje y el SC TFET tiene un grosor de canal más amplio cerca de la región de drenaje. En la Fig. 4b, también se muestra el diagrama de bandas de energía en el estado ambipolar. Puede verse claramente que la distancia mínima de túnel se encuentra cerca de la región de drenaje. Además, las distancias de túnel de SC TFET y DG TFET convencional con un espesor de canal más ancho son mayores que las del DG TFET convencional con un espesor de canal más delgado, lo que da como resultado la baja corriente ambipolar de SC TFET y DG TFET convencional con un espesor de canal más ancho.

un Tarifas BTBT y b Diagrama de bandas de energía del SC TFET y los DG TFET convencionales en el estado ambipolar, la distancia es la posición lateral de la línea de corte AA 'en la Fig. 1

Impactos de H y L S sobre las características de DC

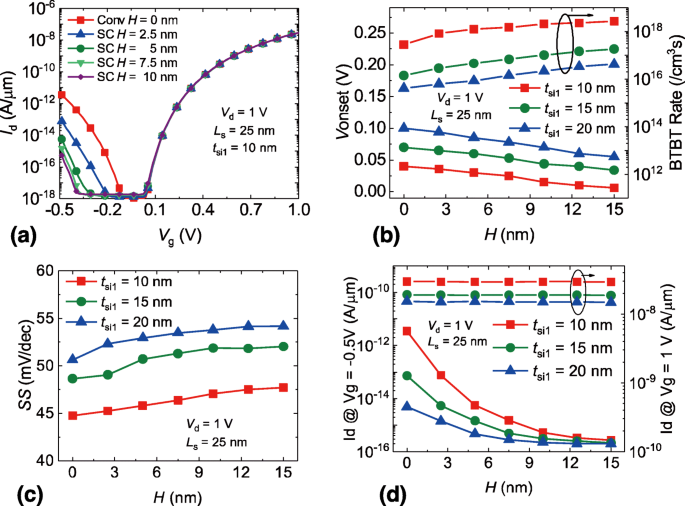

La Figura 5a muestra las curvas de transferencia del SC TFET con varios H y t si1 =10 nm. Se puede ver que el H tiene menos impacto en la corriente en el estado. Sin embargo, la corriente ambipolar se reduce significativamente a medida que H aumenta, el rango fuera del estado mejora con el aumento de H también. También se puede ver que la reducción de la corriente ambipolar disminuye a medida que H aumenta. La razón de esto es que el efecto de acoplamiento de la estructura de doble puerta tiende a ser menos significativo con un canal de mayor espesor [31]. Por lo tanto, como H aumenta, las tasas de BTBT se vuelven más independientes del grosor del canal, lo que conduce a la saturación de la corriente ambipolar. Para explorar más a fondo el parámetro de estructura óptima, los efectos de H varía de 0 a 15 nm en el rendimiento del dispositivo se extraen y se muestran en la Fig. 5b – d. La figura 5b muestra la V inicio y la variación de la tasa BTBT con diferentes H y t si1 . Puede verse que el V inicio disminuye monótonamente con el aumento de H . Esto se debe a que la esquina del electrodo de puerta introduciría la variación de la distribución de potencial en la región del canal [32, 33], dando como resultado la alteración de la tasa BTBT y la V inicio . La Figura 5b demuestra que la tasa BTBT aumenta a medida que H mejora. Como resultado, la disminución de V inicio se puede encontrar con el aumento de H . También se puede observar que V inicio aumenta a medida que t si1 aumenta. La principal razón es que el aumento de t si1 debilita la tasa BTBT, lo que resulta en un V más alto inicio . En la Fig. 5c, el promedio extraído de SS de SC TFET con varios H y t si1 se muestra. La tendencia de las SS con diferentes H es opuesto al de la V inicio . En otras palabras, las SS se eleva como el H aumenta. Hemos mencionado que la corriente de drenaje en estado depende de la t si1 , de modo que los SC TFET con diferentes H pero con la misma t si1 debe tener una corriente de drenaje similar en el estado encendido. Además, también se sabe que la V inicio disminuye con el aumento de H . Esto implica que el rango de voltaje de la puerta para impulsar la misma corriente de drenaje se mejora como el H aumenta. Como resultado, el promedio de SS aumenta monótonamente con el aumento de H . También se puede ver que el aumento de t si1 socavará el SS , que se debe a la capacidad reducida de control de la puerta. La Figura 5d muestra la corriente de drenaje en el estado activado y en el estado ambipolar con diferentes H y t si1 , respectivamente. La corriente en estado es casi independiente de la H , pero se ve muy afectado por el t si1 , que corresponde a nuestro resultado anterior de que el túnel en estado se produce principalmente cerca de la región de origen y depende en gran medida del grosor del canal cerca de la región de origen. Sin embargo, la corriente ambipolar se reduce a medida que H aumenta. Dado que el túnel del estado ambipolar está dominado cerca de la región de drenaje, el aumento de H mejorará el grosor del canal en el lado del drenaje y, por lo tanto, debilitará la corriente ambipolar. También se puede ver que la corriente ambipolar cae más significativamente cuando el H es inferior a 10 nm, lo que se debe al mayor efecto de acoplamiento con un grosor de canal más delgado.

Los impactos de H en el a curvas de transferencia, b V inicio y tasa de BTBT, c promedio SS y d drenar corriente en estado encendido / ambipolar, H es la altura del escalón y H =0 nm representa el DG TFET convencional

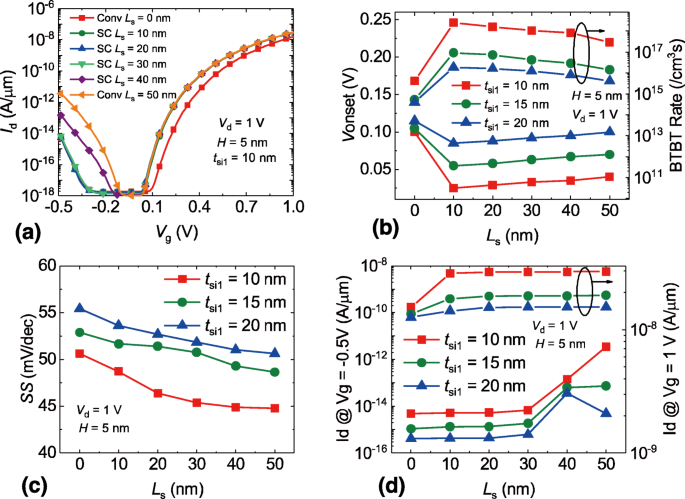

En la Fig. 6a, las curvas de transferencia de SC TFET con diferentes L s se presentan respectivamente. L s =0 nm representa el DG TFET convencional con la t correspondiente si2 y L s =50 nm representa el DG TFET convencional con la t correspondiente si1 . Se puede ver que la ubicación del paso tiene un impacto significativo en la corriente ambipolar y en el rango fuera de estado. Los SC TFET con L s menos de 30 nm muestran una corriente ambipolar similar y un rango fuera de estado. Como L s supera los 30 nm, la corriente ambipolar aumenta considerablemente. La Fig. 6b muestra la V inicio y la variación de la tasa BTBT con varios L s y t si1 , la tendencia que el V inicio aumenta a medida que t si1 las mejoras también se pueden observar claramente. El punto de inflexión del cambio en la L s =10 nm es el resultado de la variedad de t si1 . Desde L s =0 nm es el DG TFET convencional con un grosor de canal más grande, la tasa de BTBT se reduciría, lo que conduciría a un aumento de V inicio y una disminución de la corriente en estado. Salvo el caso de la DG TFET convencional, la V inicio de SC TFET aumenta monótonamente a medida que L s aumenta, que se debe a la reducción de la tasa de BTBT inducida por la estructura del canal escalonado. La Figura 6c muestra los impactos de la L s y t si1 en el SS de SC TFET. El aumento de t si1 da como resultado el SS degradado . Según Eq. (1), un grosor de canal elevado reduciría los efectos de acoplamiento entre los electrodos de puerta, lo que conduciría a una capacidad de control de puerta reducida y un aumento de SS [12]. Como L s caídas, la región con mayor espesor de canal se expandirá y debilitaría la capacidad general de control de la puerta. Como resultado, una L reducida s socavará el SS de SC TFET, que se puede observar claramente en la Fig. 6c. La Figura 6d presenta la corriente de drenaje en el estado activado y en el estado ambipolar con diferentes L s y t si1 , respectivamente. Se puede observar que la corriente en estado de SC TFET es más o menos igual a la DG TFET convencional con la correspondiente t si1 . En cuanto a la corriente ambipolar, los SC TFET con L s menos de 30 nm muestran la corriente similar a los TFET DG convencionales con el t correspondiente si2 . Cuando el L s aumenta a 40 nm, la corriente ambipolar aumenta drásticamente. De hecho, para el caso de SC TFET con L s =40 nm y t si1 =20 nm, su corriente ambipolar es incluso mayor que la del DG TFET convencional con t si1 =20 nm. Esto se debe a que la parte vertical del electrodo de puerta puede mejorar el área de tunelización, especialmente cuando la parte vertical del electrodo de puerta está cerca de la unión PN [34]. Indica que la L s debe ser inferior a 40 nm con el fin de reducir la corriente ambipolar.

Los impactos de L s en el a curvas de transferencia, b V inicio y tasa de BTBT, c promedio SS y d drenar corriente en estado encendido / ambipolar, L s es la distancia lateral desde la región de origen al paso, L s =0 nm representa el DG TFET convencional con el t correspondiente si2 y L s =50 nm representa el DG TFET convencional con la t correspondiente si1.

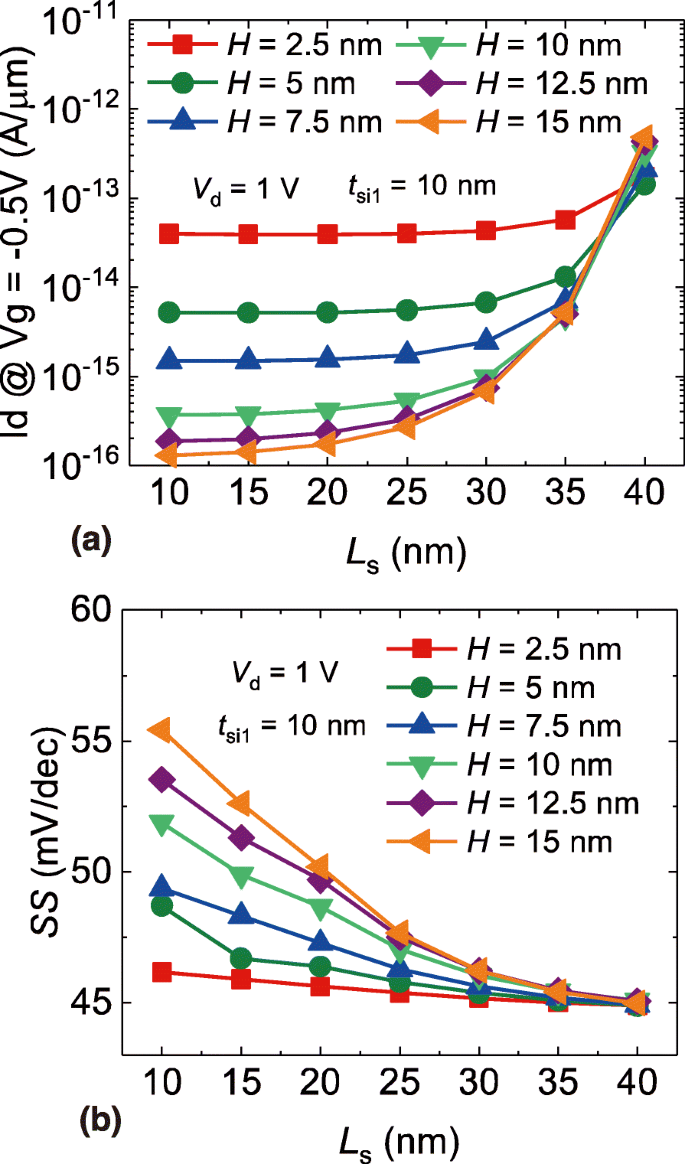

Para determinar los parámetros de estructura óptimos del SC TFET, se realiza una simulación ortogonal mediante el estudio del efecto combinado de H y la L s en el rendimiento del dispositivo. La t si1 se fija en 10 nm para lograr una mayor corriente en estado. En la Fig. 7a, la corriente ambipolar se extrae en función de la L s con varios H . Puede verse claramente que la corriente ambipolar se reduce significativamente a medida que H disminuye, lo que sugiere que una H más alta es prometedor en términos de lograr una corriente ambipolar más baja. Sin embargo, se puede observar que el beneficio de una mayor H es menos significativo. Por lo tanto, una H =15 nm sería el valor óptimo considerando que una H más grande solo podría aumentar el área del dispositivo. Mientras tanto, una disminución de L s también disminuirá la corriente ambipolar, especialmente con un H mayor . Por lo tanto, una L más baja s se desea con el propósito de una corriente ambipolar mínima. Sin embargo, una L más baja s también podría conducir a un aumento de la pendiente subumbral, como se puede observar en la Fig. 7b. La pendiente del subumbral aumenta lentamente con un L más alto s pero aumenta rápidamente con una L más baja s , lo que indica que una L s unos 25 nm sería el valor de compromiso. Como resultado, los parámetros óptimos del dispositivo serían H =15 nm y L s =25 nm donde tanto la corriente ambipolar como la pendiente del subumbral son relativamente bajas.

un La corriente ambipolar y b la pendiente del subumbral del SC TFET en función del L S con varios H

Método de fabricación

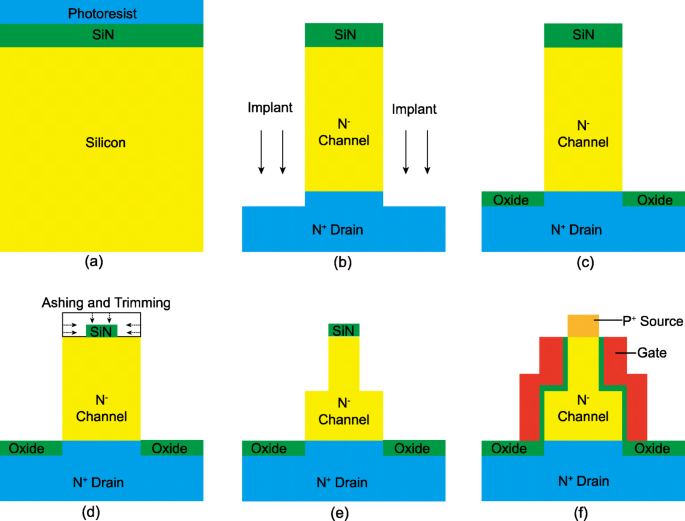

En la Fig. 8 se muestra un proceso de fabricación factible del SC TFET. Debido a la forma única del canal, el espesor del canal escalonado se puede lograr más fácilmente adoptando la estructura vertical. El proceso comienza preparando el sustrato de silicio con SiN y deposición de fotorresistente, como se muestra en la Fig. 8a. En la Fig. 8b, el patrón de SiN se logra mediante litografía, seguido del grabado para formar la región del canal, luego el N + La región se introduce mediante una implantación vertical de As y un recocido [35]. Después de eso, el óxido de aislamiento se deposita para evitar que la región de drenaje se ataque en el siguiente proceso, como se muestra en la Fig. 8c. En la Fig. 8d, la incineración y el recorte se adoptan utilizando el grabado con iones de reacción [36] para reducir el grosor y la anchura del SiN. El espesor del canal del escalón se introduce luego mediante grabado, como se muestra en la Fig. 8e. Los procesos restantes son similares al TFET vertical convencional, que implican la formación de óxido en la puerta, la deposición de la puerta, la exposición al silicio y la implantación de la región de la fuente [35, 37], como se muestra en la Fig. 8f.

Proceso de fabricación del SC TFET. un Preparación de sustrato de silicio con SiN y deposición fotorresistente. b Grabado, implantación y recocido. c Deposición de óxido de aislamiento. d Reducir el espesor y el ancho del SiN mediante incineración y recorte. e Se introduce el grosor del canal de paso. f Formación de óxido de compuerta, deposición de compuerta, planarización de compuerta e implantación de la región de origen

Conclusión

Investigamos el rendimiento eléctrico de DG TFET con espesor de canal de paso (SC TFET) utilizando la simulación 2D. La asimetría entre la fuente y el drenaje se introduce a través del espesor del canal escalonado; por tanto, el comportamiento ambipolar se alivia significativamente. El SC TFET exhibe características en estado similares del DG TFET convencional con el correspondiente t si1 y curvas paralelas off / ambipolar de la DG TFET convencional con las correspondientes t si2 . Como resultado, el SC TFET puede lograr un amplio rango fuera de estado, baja corriente ambipolar y mantener el bajo SS simultaneamente. Los mecanismos de SC TFET se analizan a fondo para explorar la percepción física. También se estudian los impactos introducidos por los parámetros de la estructura en el voltaje de inicio, pendiente subumbral, corriente de drenaje en estado activado y estado ambipolar para determinar la estructura óptima. El SC TFET con H de 15 nm y L s de 25 nm muestra los rendimientos óptimos. Además, la arquitectura del espesor del canal escalonado proporciona un método de asimetría alternativo. Dado que se ha demostrado que las estrategias de asimetría combinadas son efectivas, nuestro trabajo podría mejorar aún más el rendimiento del TFET.

Disponibilidad de datos y materiales

Todos los datos están completamente disponibles sin restricciones.

Abreviaturas

- DG TFET:

-

Transistor de efecto de campo de túnel de doble puerta

- SC TFET:

-

DG TFET con espesor de canal escalonado

- SS :

-

Pendiente subumbral

- BTBT:

-

Tunelización banda a banda

- EOT:

-

Espesor de óxido efectivo

- V inicio :

-

Voltaje de inicio

- H :

-

Altura del escalón

- L s :

-

Posición del paso

- L ch :

-

Longitud del canal

- t si :

-

Espesor del canal

- t si1 :

-

Espesor del canal cerca de la región de origen

- t si2 :

-

Espesor del canal cerca de la región de drenaje

Nanomateriales

- Conexión de las piezas:integración de un componente portátil compatible con FACE con un entorno de simulación

- El transistor de efecto de campo de unión (JFET) como interruptor

- Comprensión de los componentes de corriente de fuga en transistores MOS de canal corto

- En sintonía con el corazón de un átomo de cobre

- MoS2 con espesor controlado para evolución electrocatalítica de hidrógeno

- Efecto superficial sobre el transporte de petróleo en nanocanales:un estudio de dinámica molecular

- El estudio de un nuevo sistema micelar similar a un gusano mejorado con nanopartículas

- La optimización de programación de DRAM 1T sin capacitor basada en TFET de doble puerta

- Transistores de efecto de campo ferroeléctricos basados en patrones de banda de micrones dominados por nanotubos de carbono de pared simple con capa de control de defectos de HfO2

- Láseres de nanocables de plasma de canal con cavidades de ranura en V

- Rendimiento analógico / RF del transistor de efecto de campo de túnel de fuente dual de puerta en forma de T