Rendimiento analógico / RF del transistor de efecto de campo de túnel de fuente dual de puerta en forma de T

Resumen

En este artículo, se propone e investiga un transistor de efecto de campo de túnel de fuente dual de puerta en forma de T basado en silicio (TGTFET) mediante simulación TCAD. Como estudio contrastivo, se discuten la estructura, característica y rendimiento analógico / RF de TGTFET, LTFET y UTFET. La superposición de la puerta introducida por la puerta en forma de T puede mejorar la eficiencia de la unión de túneles. Las regiones de doble fuente en TGTFET pueden aumentar la corriente en estado ( I ACTIVADO ) al ofrecer un área de unión de túneles duplicada. Para mejorar aún más el rendimiento del dispositivo, el bolsillo n + se introduce en TGTFET para aumentar aún más la tasa de tunelización de banda a banda. Los resultados de la simulación revelan que el I del TGTFET ACTIVADO y relación de conmutación ( I ACTIVADO / Yo APAGADO ) alcanzan 81 μA / μm y 6,7 × 10 10 en una puerta de 1 V para generar voltaje ( V g ). La oscilación media del subumbral de TGTFET (SS avg , de 0 a 0,5 V V g ) alcanza 51,5 mV / dec, y la oscilación mínima del subumbral de TGTFET (SS min , a 0,1 V V g ) alcanza los 24,4 mV / dec. Además, se encuentra que TGTFET tiene una gran robustez en el efecto de reducción de la barrera inducida por el drenaje (DIBL). Se investigan los efectos de la concentración de dopaje, la dimensión geométrica y el voltaje aplicado en el rendimiento del dispositivo para crear la guía de diseño TGTFET. Además, la transconductancia ( g m ), conductancia de salida ( g ds ), capacitancia de puerta a fuente ( C gs ), puerta para drenar la capacitancia ( C gd ), frecuencia de corte ( f T ), y el ancho de banda de ganancia (GBW) de TGTFET alcanza los 232 μS / μm, 214 μS / μm, 0,7 fF / μm, 3,7 fF / μm, 11,9 GHz y 2,3 GHz a 0,5 V de drenaje a voltaje de fuente ( V d ), respectivamente. Aprovechando la ventaja estructural, TGTFET obtiene mejores características de CC / CA en comparación con UTFET y LTFET. En conclusión, el considerable buen rendimiento hace que TGTFET se convierta en una opción muy atractiva para la próxima generación de aplicaciones de baja potencia y analógicas / RF.

Antecedentes

La reducción de los transistores de efecto de campo de semiconductores de óxido metálico (MOSFET) aporta una mejora significativa en el consumo de energía del circuito integrado (IC), la característica de conmutación, la función del circuito y la densidad de IC [1, 2]. Pero la contradicción irreconciliable entre el escalado de la tensión de alimentación y la reducción de las corrientes de fuga fuera de estado ( I APAGADO ) dará lugar finalmente a un consumo de energía elevado e inaceptable [3]. Al mismo tiempo, la degradación de la fiabilidad causada por los efectos de canal corto (SCE) se vuelve cada vez más grave [4, 5]. Para abordar estos problemas, es válido reducir la oscilación del subumbral (SS) y la tensión de alimentación de los dispositivos. Según el mecanismo de tunelización de banda a banda, los transistores de efecto de campo de túnel (TFET) alcanzan la oscilación del subumbral (SS) inferior a 60 mV / dec y podrían reducir eficazmente la tensión de alimentación [6,7,8,9,10] . Además, debido a la existencia de la unión de túnel cerca de la fuente, TFET generalmente tiene una pequeña puerta para generar capacitancia ( C gs ) [1, 11] que es beneficioso para el rendimiento de frecuencia del dispositivo.

Estudios recientes muestran que TFET parece ser un candidato prometedor para futuras aplicaciones de baja potencia [12,13,14,15,16] y aplicaciones analógicas / RF [17,18,19]. Sin embargo, debido a la pequeña área efectiva de tunelización, la corriente de tunelización limitada se convierte en una desventaja inherente en el TFET P-I-N convencional, lo que conduce a una baja corriente de operación en estado ( I ACTIVADO ). Con el fin de mejorar el rendimiento de TFET, se han propuesto muchas estructuras nuevas en los últimos años [20, 21, 22, 23, 24, 25]. Beneficiándose de la puerta empotrada, se propuso el transistor de efecto de campo de túnel en forma de L (LTFET) [23, 24] y el transistor de efecto de campo de túnel en forma de U (UTFET) [25] para obtener un alto I ACTIVADO con una estructura de dispositivo compacta. Sin embargo, todavía hay mucho margen de mejora en LTFET y UTFET y es necesario dedicar más esfuerzo a estudiar el rendimiento analógico / RF de estos dispositivos.

En este artículo, un transistor de efecto de campo de túnel de fuente dual de puerta en forma de T (TGTFET) con fuente dual se presenta y estudia mediante simulación TCAD. El TGTFET diseñado puede duplicar el área de unión de túneles en comparación con LTFET y UTFET. La superposición de la puerta introducida por la puerta en forma de T diseñada puede mejorar la tasa de tunelización banda a banda (tasa BBT). Los resultados de la simulación muestran que el TGTFET propuesto obtiene un I más alto ACTIVADO (8,1 × 10 - 5 A / μm en V d =1 V) que LTFET y UTFET en las mismas condiciones. Ambos SS min (en V g =0,1 V) y SS avg (0 ~ 0,5 V V g ) de TGTFET son inferiores a 60 mV / dec (24,4 mV / dec y 51,5 mV / dec, respectivamente). TGTFET obtiene una mejor característica de entrada / salida ( g m =232 μS / μm, g ds =214 μS / μm) que UTFET y LTFET. Además, las características de capacitancia de TGTFET, UTFET y LTFET se analizan en detalle. Finalmente, TGTFET obtiene un mejor rendimiento analógico / RF ( f T =11,9 GHz y GBW =2,3 GHz) en comparación con UTFET y LTFET. Como resultado, se puede obtener TGTFET con un desempeño considerable. Las estructuras de este trabajo son las siguientes:la sección de “Métodos” incluye la descripción de la estructura y los parámetros de TGTFET, LTFET [23, 24] y UTFET [25 ] así como los métodos de simulación TCAD. La sección "Resultados y discusión" incluye la descripción de los resultados de la simulación. En esta sección, se estudian el mecanismo, las características y el rendimiento analógico / RF de TGTFET y se comparan con LTFET y UTFET. La influencia de los parámetros del dispositivo en TGTFET también se analiza en detalle. La sección "Conclusiones" ofrece una conclusión de este documento.

Métodos

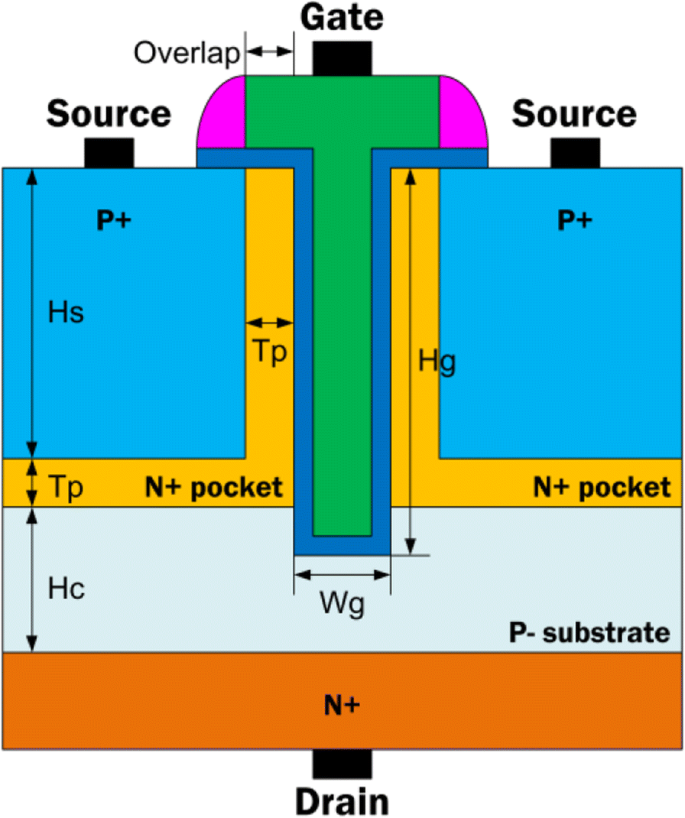

La estructura del transistor de efecto de campo de túnel de fuente dual de puerta en forma de T (TGTFET) se ilustra en la Fig. 1. La forma de la puerta es similar a la letra del alfabeto “T” (región verde). Las regiones de fuente dual están ubicadas en dos lados de la puerta (regiones de zafiro). Se insertan dos n + bolsillos (regiones amarillas) para aumentar la tasa de tunelización del canal [20, 21, 22]. El drenaje n + se coloca en el fondo del canal. Por lo tanto, la puerta en forma de T se superpone a los n + bolsillos tanto en la dirección vertical como en la lateral. De esta manera, se puede aumentar el campo eléctrico en la parte superior de la unión de túnel. La mejora del campo eléctrico hace que la banda de energía se doble más abruptamente. Finalmente, la tasa de tunelización de electrones se mejora debido a la mejora del campo eléctrico de esquina [26].

Esquema del transistor de efecto de campo de túnel de fuente dual de puerta en forma de T propuesto (TGTFET)

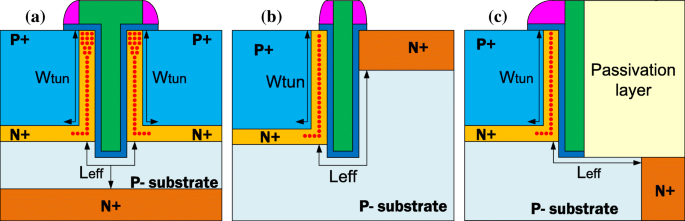

La Figura 2 muestra la estructura del dispositivo de LTFET [23, 24], UTFET [25] y TGTFET. La superposición de la puerta puede ayudar a mejorar la eficiencia de túnel de TGTFET. Las regiones de doble fuente en TGTFET pueden duplicar el área de unión de túneles en comparación con LTFET y UTFET.

Comparación de a el TGTFET propuesto, b UTFET y c LTFET

Los parámetros de TGTFET, UTFET y LTFET basados en silicio utilizados en las simulaciones son los siguientes:Hs =30 nm (altura de la región fuente), Hg =40 nm (altura de la puerta empotrada), Wg =6 nm (ancho de la región de la puerta), Hc =15 nm (altura de la región del canal), Tp =5 nm (espesor del bolsillo n +), ϕ =4 . 33 eV (función de trabajo de la puerta), Tox =2 nm (espesor del HfO 2 dieléctrico de puerta), N S =1 × 10 20 cm −3 (p + concentración de dopaje en la fuente), N D =1 × 10 19 cm −3 (concentración de dopaje de drenaje + n), N sub =1 × 10 17 cm −3 (p - concentración de dopaje de sustrato) y N P =5 × 10 18 cm −3 (concentración de dopaje n + bolsillo). El coeficiente de ancho en la simulación está predeterminado en 1 μm.

Las simulaciones de TGTFET, UTFET y LTFET se llevan a cabo en las herramientas Silvaco Atlas TCAD. El modelo BTBT no local se introduce en esta simulación para tener en cuenta la variación espacial de la banda de energía, lo que puede ayudar a facilitar la precisión del proceso de tunelización BTBT. Se considera que el modelo de movilidad de Lombardi hace que la movilidad del canal sea más precisa (considerando la dispersión en la superficie, incluido el campo transversal y la concentración de dopaje). Las estadísticas de Fermi y el modelo de estrechamiento de la banda prohibida se tienen en cuenta para ajustar el efecto de las regiones altamente dopadas. En este documento también se tiene en cuenta el modelo de recombinación Shockley-Read-Hall.

Resultados y discusión

Mecanismo del dispositivo y características de CC con diferentes parámetros

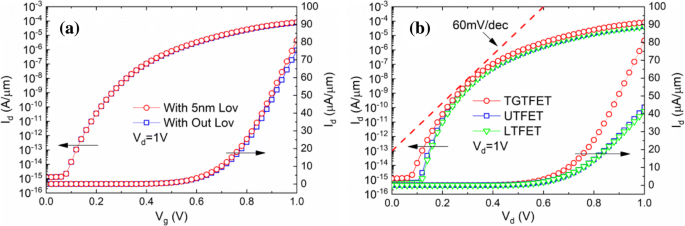

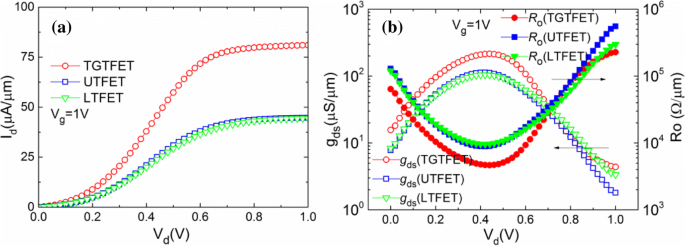

La Figura 3a muestra las características de transferencia del TGTFET con y sin la superposición de puertas. Con la superposición de la puerta adicional, el I ACTIVADO aumenta de 7,5 × 10 −5 a 8,1 × 10 −5 A / μ m en V g = V d =1 V. La Figura 3b muestra las curvas características de transferencia de TGTFET, UTFET y LTFET. Para que la comparación sea más precisa, los modelos de simulación y las dimensiones geométricas de estos tres dispositivos se configuran para que sean idénticos. Como resultado, el TGTFET tiene aproximadamente un aumento del doble en I ACTIVADO en comparación con LTFET y UTFET, como se muestra en la Fig. 3b. SS min de TGTFET es 24,4 mV / dec en V g =0,1 V y SS avg es 51,5 mV / dec cuando 0 V < V g <0,5 V. Las relaciones de conmutación ( I ACTIVADO / Yo APAGADO ) son 6,7 × 10 10 en V g = V d =1 V y 6,5 × 10 8 en V g = V d =0,5 V.

a simulado características de transferencia de TGTFET con / sin superposición de puerta y b características de transferencia de TGTFET, UTFET y LTFET

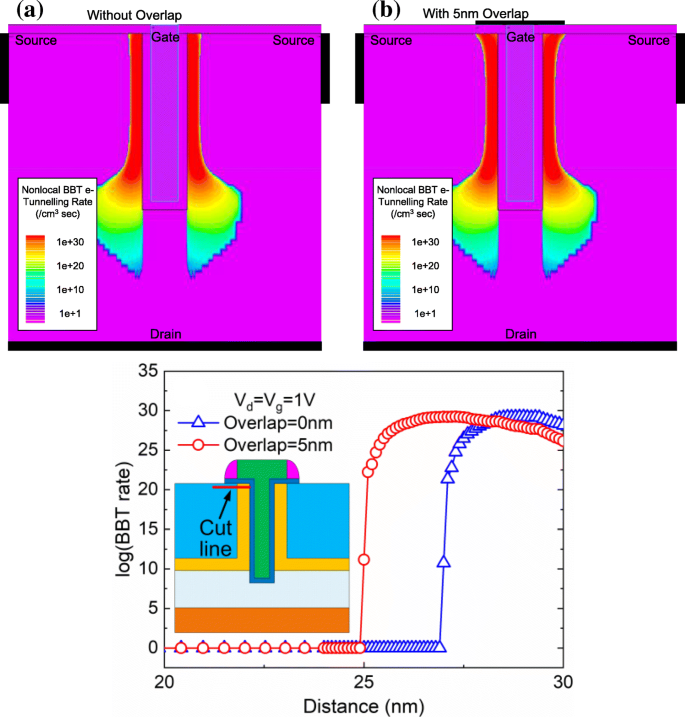

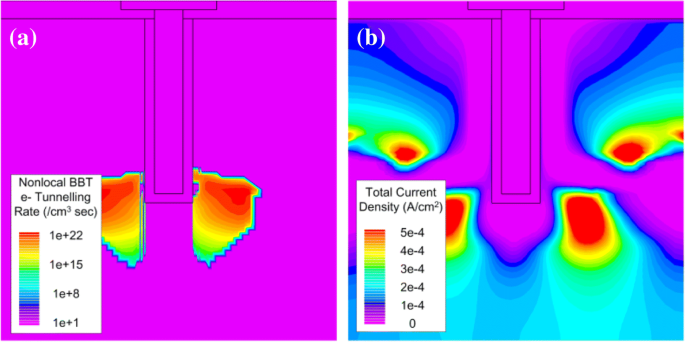

La Figura 4a, b muestra la tasa de BBT de TGTFET con y sin un solapamiento de puerta de 5 nm. En la Fig. 4c, podemos ver claramente que el dispositivo con una superposición de puerta de 5 nm tiene un área de túnel de electrones más amplia debajo de la superficie del dispositivo, lo que puede conducir a la I ACTIVADO aumentando.

Diagramas de velocidad de tunelización de electrones BBT simulados de a dispositivo sin superposición de puerta, b dispositivo con superposición de puerta de 5 nm y c la tasa de tunelización de electrones BBT de dos dispositivos, a 1 nm por debajo de la superficie del dispositivo; V g = V d =1 V

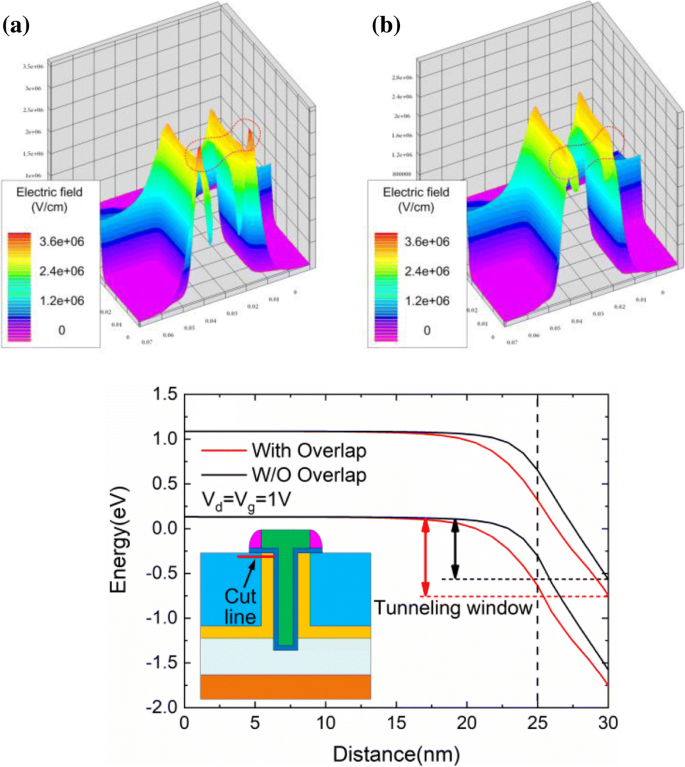

La Figura 5a, b muestra el diagrama 3D de campos eléctricos de TGTFET con y sin superposición de puertas. Aparecen dos picos de campo eléctrico en TGTFET con una superposición de puerta de 5 nm, como se muestra en el círculo punteado en la Fig. 5a. No aparece ningún pico de campo eléctrico en la Fig. 5b atribuido a las ausencias de la superposición de la puerta. La figura 5c muestra la estructura de la banda de energía debajo de la superficie del dispositivo. El recuadro de la Fig. 5c muestra la ubicación de la línea de corte. Con la superposición de la puerta, se puede obtener una ventana de túnel más grande. Por lo tanto, una tasa de BBT más alta y I ACTIVADO se puede lograr.

Diagrama esquemático 3D de campos eléctricos del dispositivo a con superposición y b sin superposición; c simulado diagramas de bandas de energía desde la fuente hasta la región de bolsillo (1 nm por debajo de la interfaz de óxido)

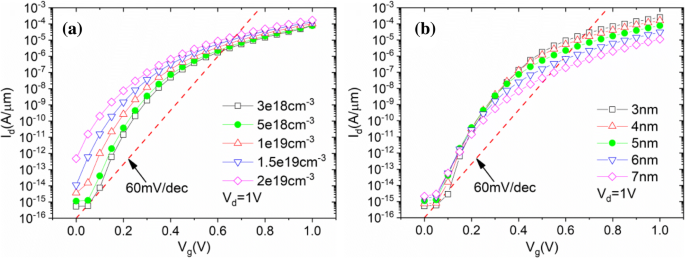

La Figura 6 muestra los efectos de n + bolsillo en el desempeño del TGTFET. El yo APAGADO aumenta rápidamente con el aumento de la concentración de dopaje de n + bolsas, como se muestra en la Fig. 6a. El SS más bajo y el I mayor ACTIVADO se puede obtener disminuyendo el grosor de n + bolsillo (Tp) de 7 a 3 nm cuando N P =5 × 10 18 cm −3 , como se muestra en la Fig. 6b. Al mismo tiempo, en la figura 6b no se observa ninguna corriente subumbral significativa. Se puede confirmar a partir de la Fig. 6a que una concentración de dopaje relativamente baja de n + bolsillo ayudará a suprimir la corriente subumbral.

Corrientes de drenaje simuladas con diferentes n + cavidades a concentraciones y b espesores en V d =1 V

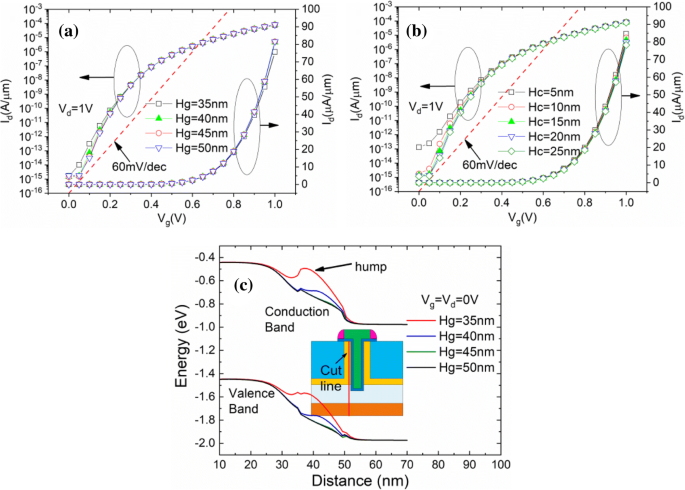

El impacto de la altura de la puerta (Hg) y el espesor del canal (Hc) se muestra en la Fig. 7a, b, por separado. Una pequeña I ACTIVADO y la mejora de la SS aparece cuando el Hg aumenta. Porque cuando Hg =35 nm, hay una joroba de banda de energía obvia en la ruta de la corriente en estado activo, convirtiéndose en un cierto obstáculo para los electrones afortunados (electrones que pasaron la unión tunelizadora), como se muestra en la Fig.7c, lo que puede resultar en yo en disminución. Cuando aumenta el Hg, la joroba de la banda de energía se debilita, lo que provoca que I ACTIVADO y mejora de SS. Un ligero I ACTIVADO la mejora se obtiene con Hc decreciente, como se muestra en la Fig. 7b. Sin embargo, se puede observar una degradación severa en la característica subumbral cuando Hc disminuye a 5 nm. Esto puede explicarse por el aumento de la corriente de tunelización subumbral en la esquina de la bolsa n +, como se muestra en la Fig. 8. La Figura 8a muestra el obvio fenómeno de tunelización banda a banda en el estado desactivado cuando Hc =5 nm mientras que la Fig. 8b muestra el yo APAGADO densidad de corriente cuando Hc =5 nm.

Características de transferencia simuladas de TGTFET con a diferente Hg, b diferente Hc y c la joroba de la banda de conducción en la ruta actual

Diagramas simulados de a fuera del estado Tasa de tunelización de electrones BTBT y b densidad de corriente cuando Hc =5 nm

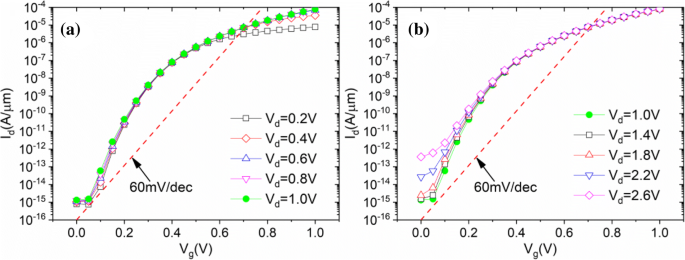

Como se muestra en la Fig.9, la influencia del drenaje al voltaje de la fuente ( V d ) también se tiene en cuenta en este documento. Para V d <0,6 V, I ACTIVADO aumenta obviamente con el aumento de V d , como se muestra en la Fig. 9a. Esto se explica por el hecho de que el potencial del canal p está creciendo lentamente en respuesta al aumento de V d y da como resultado la disminución de la resistencia del canal p. Para V d > 1.8 V, mostrado en la Fig. 9b, el I ACTIVADO casi no aumenta con el aumento de V d , pero yo APAGADO aumenta considerablemente. Esto se debe a que la corriente de tunelización subumbral en la esquina de la bolsa n + aumenta rápidamente con el aumento de V d . Finalmente, para 0.6 V < V d <1.8 V, TGTFET exhibe un desempeño bueno y estable. Como resultado, TGTFET es robusto para la reducción de barrera inducida por drenaje (DIBL) y exhibe un desempeño bueno y estable en un rango dinámico de voltaje aplicado más grande.

Corrientes de drenaje simuladas para a V d ≤ 1 V y b V d ≥ 1 V

Rendimiento analógico / RF de TGTFET, UTFET y LTFET

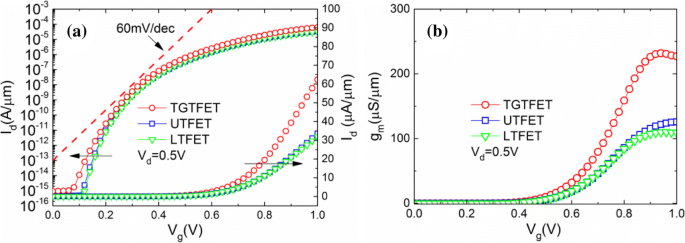

La Figura 10 muestra las características de transferencia y las curvas de transconductancia de TGTFET, UTFET y LTFET en V d =0,5 V. La transconductancia ( g m ) se puede obtener a partir de la primera derivada de la curva característica de transferencia, como se muestra en la Ec. (1) [27,28,29]:

$$ {g} _ {\ mathrm {m}} ={dI} _ {\ mathrm {d} s} / {dV} _ {\ mathrm {gs}} $$ (1)

un Transferir características y b curvas de transconductancia de TGTFET, UTFET y LTFET en V d =0,5 V

Como resultado, la transconductancia máxima de TGTFET (232 μS / μm) es aproximadamente dos veces mayor que la de UTFET (120 μS / μm) y LTFET (110 μS / μm), como se muestra en la Fig. 10. Esto se beneficia de la ganancia actual contribuida por la superposición de la puerta y la fuente dual.

La Figura 11 muestra las características de salida, conductancia de salida ( g ds ) e impedancia de salida ( R o ) curvas de TGTFET, UTFET y LTFET. Como se muestra en la Fig. 11a, se puede ver claramente que la corriente de salida del dispositivo aumenta con el aumento de V d , pero cuando V d alcanza por encima de 0,6 V, la corriente de salida tiende a saturarse. A través de la observación, es fácil encontrar que la corriente de salida de TGTFET es dos veces mayor que la de UTFET y LTFET. La Figura 11b muestra la conductancia de salida ( g ds ) e impedancia de salida ( R o ) curvas de TGTFET, UTFET y LTFET. El g ds se puede obtener mediante la derivación de la corriente de salida, como se muestra en la Ec. (2) [27, 29] mientras que R o se puede expresar como el recíproco de la conductancia de salida.

$$ {g} _ {\ mathrm {ds}} ={dI} _ {\ mathrm {ds}} / {dV} _ {\ mathrm {ds}} $$ (2)

un Características de salida, b conductancia de salida ( g ds ) y c impedancia de salida ( R o ) curvas de TGTFET, UTFET y LTFET

Debido a las ventajas de la corriente de salida, TGTFET obtiene la mayor cantidad de g ds y el mínimo de R o de estos tres dispositivos. Bajo condición de polarización de puerta de 1 V, TGTFET obtuvo el máximo g ds de 214 μS / μm y el mínimo de R o de 4,6 kΩ / μm por debajo de 0,45 V V d . Bajo la misma condición de polarización de puerta, UTFET y LTFET obtuvieron el máximo de g ds de 113 μS / μm y 105 μS / μm y el mínimo de R o de 9,0 kΩ / μm y 9,6 kΩ / μm por debajo de 0,4 V V d .

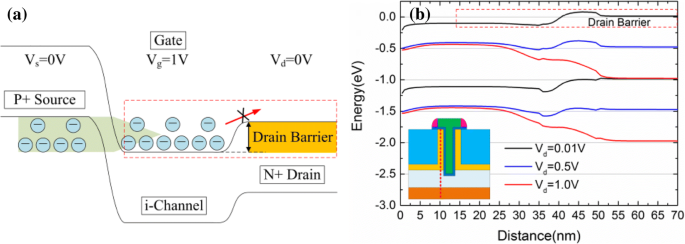

Además, en la figura 11, no es difícil descubrir que la región lineal de las características de salida del dispositivo muestra cierta no linealidad. Como se muestra en la Fig. 11a, R o disminuye primero y luego aumenta con el aumento de V d . Algunos grupos de investigación dan el proceso físico correspondiente sobre este fenómeno [7, 30] pero aún existen algunos problemas que no se han explicado con claridad. Como sabemos, R o está determinada por la resistencia de la región del canal y la unión de túneles. Cuando V d <0,4 V, R o disminuye con el aumento de V d . Considere las siguientes situaciones, cuando V d =0 V y V g =1 V, ninguno de los electrones afortunados puede ser arrastrado hacia el lado de drenaje, y casi todos los electrones quedan atrapados en la región del canal por una barrera de drenaje relativamente alta, como se muestra en el marco de la línea punteada roja en la Fig. 12a, b. Cuando 0 V < V d <0,4 V, con el aumento de V d , la barrera de drenaje se debilita (como se muestra en la Fig. 12b). Por lo tanto, los electrones atrapados en la región del canal pueden atravesar la barrera de drenaje y luego ser recogidos por el drenaje. Este es un proceso de excitación térmica de electrones desde el canal hasta el drenaje. Finalmente, como el cruce de túnel se ha activado por completo (cuando V g =1 V), la corriente de tunelización siempre está en un estado de exceso y la resistencia introducida por la unión de tunelización puede ignorarse. En este momento, R o está determinada por la resistencia del canal y R o se decide por el proceso de excitación térmica de electrones a través de la barrera de drenaje. Por lo tanto, R o disminuye con el aumento de V d . Cuando V d > 0,6 V, estos tres dispositivos entran gradualmente en el área de saturación y R o se vuelve más grande. Esto se debe a que cuando V d es grande, casi todos los electrones a través de la unión de túnel son arrastrados hacia el lado de drenaje por el campo eléctrico relativamente alto. La corriente de túnel se convierte en el límite de la corriente de drenaje. En esta condición, R o está determinada principalmente por el cruce de túneles. Sin embargo, la eficiencia de la tunelización no puede aumentar significativamente mientras V d esta incrementando. V d tiene un pequeño efecto en la estructura de la banda de energía de la unión de túnel (n + lado de la cavidad), como se muestra en la Fig. 12b. Como resultado, la corriente de túnel no puede aumentar obviamente, y casi no hay I ACTIVADO aumentar con el V en constante aumento d (cuando V d > 0,6 V), lo que significa que aumenta la impedancia. Además, cuando 0.4 V < V d <0,6 V, R o está determinada tanto por la resistencia del canal como por la unión del túnel.

un Diagrama esquemático de la banda de energía en V d =0 V y V g =1 V. b Resultados de la simulación del diagrama de bandas de energía con diferentes sesgos de V d

Se puede obtener del análisis anterior que la R o de TFET está influenciado tanto por el proceso de tunelización como por el proceso de excitación térmica de electrones del canal. Los principales mecanismos físicos pueden dominar R o cambia con V d variación. Finalmente, la R o disminuye primero y luego aumenta, lo que provoca la no linealidad de las características de salida. Por cierto, a través de la observación de la Fig. 11b, es fácil encontrar que la impedancia de salida de TGTFET es mucho menor que la de UTFET y LTFET. Esto se debe al mejor beneficio de eficiencia de tunelización de la estructura de superposición de puerta lateral y de doble fuente de TGTFET.

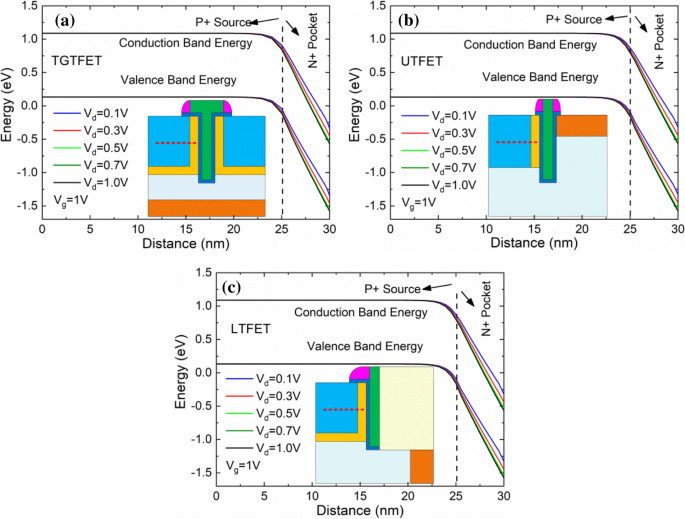

La Figura 13 muestra la estructura de la banda de energía de TGTFET, UTFET y LTFET con diferentes voltajes aplicados. Las líneas de puntos rojas en el recuadro representan la posición para dibujar la banda de energía (que está a 15 nm por debajo de la superficie, justo a la mitad de la altura de la región de la fuente). Se puede ver que con una V d aumenta de 0,1 a 0,5 V, la estructura de banda de TGTFET, UTFET y LTFET tiene una tendencia obvia a la flexión. Esto se debe a que el voltaje de drenaje puede reducir el potencial eléctrico de la unión de túnel cerca del lado del drenaje. Esto indica que, para TGTFET, UTFET y LTFET, el aumento de V d de 0,1 a 0,5 V es beneficioso para la eficiencia del túnel. Sin embargo, cuando V d > 0.5 V, el cambio de la banda de energía con V d aumento no es digno de mención. Esto es consistente con los resultados del análisis en la Fig. 12b.

La estructura de la banda de energía de a TGTFET, b UTFET y c LTFET en V g =1

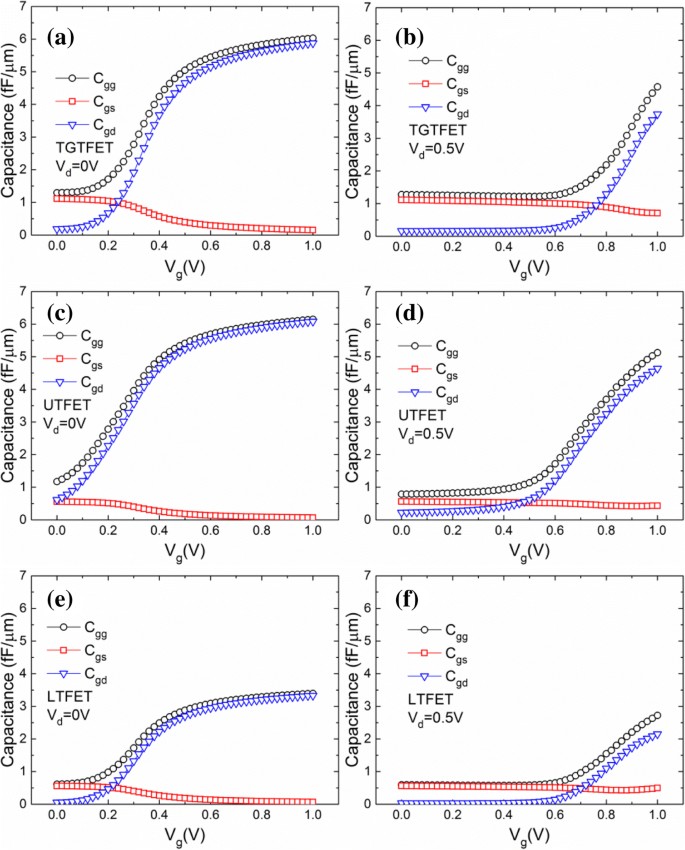

Como sabemos, la capacitancia de la puerta ( C gg ) del dispositivo puede afectar en gran medida las características de frecuencia de los circuitos integrados. Para TGTFET, UTFET y LTFET, C gg generalmente consta de C gs (capacitancia de la puerta a la fuente) y C gd (puerta para drenar capacitancia). Por tanto, la característica de C gg , C gs y C gd es de gran importancia para evaluar las características de frecuencia y la capacidad de aplicación analógica de los dispositivos. Especialmente para TFET, las características de capacitancia son bastante diferentes a las de MOSFET. Debido a la existencia de la unión de túnel en el área de origen, TFET generalmente tiene una pequeña C gs [1, 11]. Por lo tanto, la C gg de TFET está determinado principalmente por C gd . La Figura 14 muestra la capacitancia de TGTFET, UTFET y LTFET frente a V g debajo de V d =0,5 V y V d =0 V, por separado.

Capacitancia de TGTFET frente a V g bajo a V d =0 V y b V d =0.5 V. Capacitancia de UTFET versus V g debajo de c V d =0 V y d V d =0.5 V. Capacitancia de LTFET versus V g debajo de e V d =0 V y f V d =0,5 V

A través de la observación de la Fig. 14a, b, es fácil encontrar que la C gs de TGTFET bajo voltaje de compuerta de 1 V es 0.15 fF / μm a V d =0 V y 0,7 fF / μm en V d =0,5 V, que es mucho más pequeño que el de C gd (5,8 fF / μm en V d =0 V y 3,7 fF / μm en V d =0,5 V). Por lo tanto, la C gg de TGTFET está determinado principalmente por C gd . Cuando V d =0 V, C gg y C gd aumentar rápidamente con el aumento de V g , como se muestra en la Fig. 14a. Esto se debe a que con el aumento de V g , los electrones se agregan a la interfaz de la puerta en el canal del dispositivo, lo que hace que la capacitancia aumente rápidamente. Cuando V d =0,5 V, C gd no aumenta obviamente hasta V g aumenta a más de 0,6 V, como se muestra en la Fig. 14b. Esto se debe a que cuando V g es bajo, solo unos pocos electrones afortunados pueden pasar a través de la unión de túnel y entrar en el canal. Algunos de estos electrones afortunados participarán en el proceso de recombinación, y la mayoría de los demás serán recolectados rápidamente por drenaje debido al voltaje de drenaje de 0.5 V. Por lo tanto, es muy difícil que estos electrones afortunados permanezcan en el canal del dispositivo. Sin embargo, con V g aumenta, el número de electrones de la suerte aumenta rápidamente. En este momento, ni la colección de drenaje ni el proceso de recombinación de los huecos de electrones pueden agotar rápidamente estos electrones afortunados. Por tanto, la concentración de electrones en el canal aumenta y la capacitancia aumenta rápidamente. Como resultado, la curva característica de capacitancia tiende a desplazarse hacia la derecha mientras V d aumenta, como se muestra en la Fig. 14a, b. El análisis y los fenómenos anteriores también son aplicables a UTFET y LTFET, como se muestra en la Fig. 14c-f. Además, la capacidad de la puerta de UTFET a 0 V y 0,5 V V d alcanzó 6,2 fF / μm y 5,1 fF / μm, respectivamente, y la del LTFET alcanzó 3,4 fF / μm y 2,7 fF / μm, respectivamente.

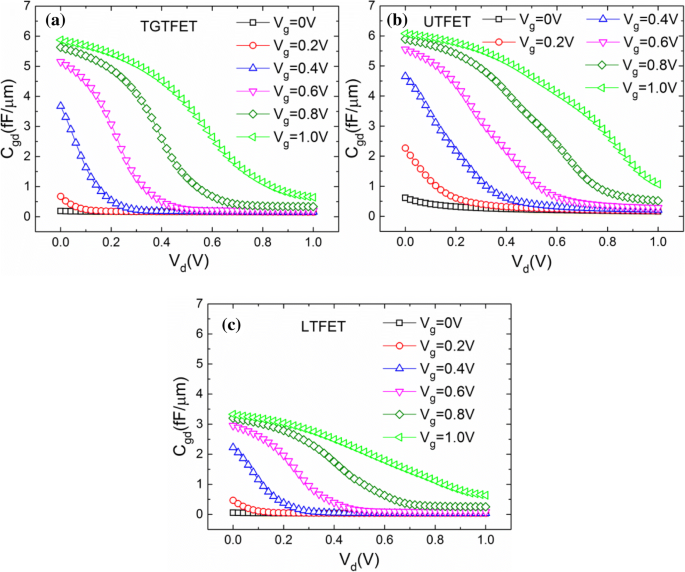

Dado que no hay una superposición directa entre la puerta y el drenaje de LTFET, y la distancia entre la puerta y el drenaje es relativamente grande, LTFET tiene las mejores características de capacitancia y el C más pequeño gg . Por el contrario, existe una superposición directa entre la puerta y el drenaje de UTFET. Por lo tanto, los electrones cerca del lado de drenaje se controlan más fácilmente mediante la puerta, lo que da como resultado una gran C gg de UTFET. Para TGTFET, aunque la distancia entre la puerta y el drenaje es cercana, hay una región de canal ligeramente dopada que puede aislar la puerta y el drenaje. Por lo tanto, la capacitancia de TGTFET es mejor que la de UTFET, pero ligeramente inferior a LTFET. La figura 15 muestra la C gd características de TGTFET, UTFET y LTFET frente a V d bajo diferentes V g . De la observación de la Fig. 15a-v, no es difícil encontrar que la C gd Las características de estos tres dispositivos son similares. Es decir, para una V fija g , C gd disminuye con el aumento de la V d . Por otro lado, para una V fija d , C gd aumenta con el aumento de V g .

C gd características de a TGTFET, b UTFET y c LTFET frente a V d bajo diferentes V g

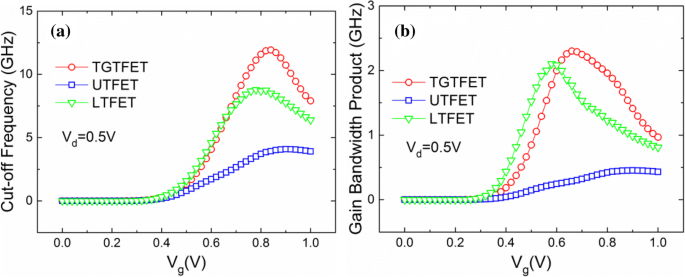

Como sabemos, tanto la frecuencia de corte ( f T ) y el ancho de banda de ganancia (GBW) son los criterios de evaluación para evaluar las características de frecuencia de los dispositivos. f T depende de la proporción de g m a C gg , como se muestra en la ecuación. (3) [30, 31]. Para una cierta ganancia de CC que es igual a 10, GBW se puede expresar por la proporción de g m a C gd , como se muestra en la ecuación. (4) [17]:

$$ {f} _T =\ frac {g _ {\ mathrm {m}}} {2 \ pi {C} _ {\ mathrm {gs}} \ sqrt {1 + 2 {C} _ {\ mathrm {gd} } / {C} _ {\ mathrm {gs}}}} \ approx \ frac {g _ {\ mathrm {m}}} {2 \ pi \ left ({C} _ {\ mathrm {gs}} + {C } _ {\ mathrm {gd}} \ right)} =\ frac {g _ {\ mathrm {m}}} {2 \ pi {C} _ {\ mathrm {gg}}} $$ (3) $$ \ mathrm {GWB} ={g} _ {\ mathrm {m}} / 2 \ pi 10 {C} _ {\ mathrm {gd}} $$ (4)La Figura 16 muestra las curvas características de la f T y GBW de TGTFET, UTFET y LTFET. Beneficiándose de las ventajas estructurales, como la superposición de puerta lateral y de fuente dual introducida por la puerta en forma de T, TGTFET obtiene las características de frecuencia más sobresalientes en comparación con UTFET y LTFET. Bajo la condición de V d =0,5 V, la f T y GBW de TGTFET alcanzaron los valores máximos de 11,9 GHz y 2,3 GHz, respectivamente. Aprovechando la gran distancia entre la puerta y el desagüe y sin superposición entre la puerta y el desagüe, LTFET obtiene una pequeña C gg y buenas características de frecuencia. La f T y GBW de LTFET alcanzan los 8,7 GHz y 2,1 GHz, por separado. Las características de capacitancia de UTFET son inferiores en comparación con las de TGTFET y LTFET. Esto se debe a que la puerta / drenaje directo se superpone. Como resultado, el valor máximo de f T and GBW of UTFET can only reach 4.1 GHz and 0.5 GHz separately.

The characteristic curves of a f T y b GBW of TGTFET, UTFET, and LTFET versus V g at V d = 0.5 V

Conclusiones

In this paper, a T-shape gate dual-source tunnel field-effect transistor (TGTFET) with good performance is proposed and investigated. The structure, mechanism, and the influence of device parameter on the characteristic of TGTFET are discussed. In addition, the characteristics of TGTFET, UTFET, and LTFET are discussed and compared in this paper. The dual-source regions are introduced to double the area of the tunneling junction. The gate overlap and the n+ pockets can obviously enhance the tunneling efficiency of the tunneling junction in TGTFET. Finally, the TGTFET with impressive characteristics (I ON = 8.1 × 10 −5 A/μm, I ON / Yo OFF = 6.7 × 10 10 and SSmin = 24.4 mV/dec) is obtained. At the same time, TGTFET is robust to DIBL, which means TGTFET can exhibit a good and stable performance in a larger applied voltage dynamic range. Furthermore, the analog/RF performance of TGTFET is studied and compared with UTFET and LTFET. The key parameter such as input/output characteristics, capacitance characteristics, GBW, and f T are analyzed. Benefiting from the no direct overlap between the gate and drain, TGTFET obtains a relatively small C gd y C gg . Finally, TGTFET with remarkable frequency characteristics (f T = 11.9 GHz and GBW = 2.3 GHz) is obtained. As a conclusion, it is expected that TGTFET can be one of the promising alternatives for the next generation of device in low-power and analog/RF applications.

Abreviaturas

- C gd :

-

Gate to drain capacitance

- C gs :

-

Gate to source capacitance

- f T :

-

Cut-off frequency

- GBW:

-

Gain bandwidth

- g ds :

-

Output conductance

- g m :

-

Transconductance

- Hc:

-

Height of the channel layer

- Hg:

-

Height of the gate electrode

- Hs:

-

Height of the source layer

- LTFET:

-

L-shape gate tunnel field-effect transistor

- N D :

-

Doping concentration of n+ drain

- N P :

-

Doping concentration of n+ pocket

- N S :

-

Doping concentration of p+ source

- N sub :

-

Doping concentration of p− substrate

- R o :

-

Output impedance

- TGTFET:

-

T-shape gate dual-source tunnel field-effect transistor

- Tox:

-

Thickness of the HfO2 gate dielectric

- Tp:

-

Thickness of n+ pocket

- UTFET:

-

U-shape gate tunnel field-effect transistor

- V d :

-

Drain to source voltage

- V g :

-

Gate to source voltage

- Wg:

-

Width of the gate electrode

Nanomateriales

- Transistores, efecto de campo de unión (JFET)

- Transistores, efecto de campo de puerta aislada (IGFET o MOSFET)

- Transistores de efecto de campo de unión

- Transistores de efecto de campo de puerta aislada (MOSFET)

- El transistor de efecto de campo de unión (JFET) como interruptor

- Túnel

- El primer transistor de temperatura ambiente ultrarrápido totalmente óptico del mundo

- Rendimiento fotocatalítico de luz visible de nanocompuestos de ZnO / g-C3N4 dopado con N

- Preparación y rendimiento fotocatalítico de fotocatalizadores LiNb3O8 de estructura hueca

- Un nuevo fotocatalizador de heterounión Bi4Ti3O12 / Ag3PO4 con rendimiento fotocatalítico mejorado

- Transistor de canal de vacío a nanoescala basado en grafeno