La optimización de programación de DRAM 1T sin capacitor basada en TFET de doble puerta

Resumen

El mayor volumen de condensador y la mayor corriente de fuga del transistor se han convertido en las desventajas inherentes de la memoria de acceso aleatorio dinámico (DRAM) tradicional de un transistor (1T) y un condensador (1C). Recientemente, el FET de tunelización (TFET) se aplica en la celda DRAM debido a la baja corriente en estado apagado y la alta relación de conmutación. La celda DRAM TFET (DG-TFET) de doble puerta con estructura sin condensador tiene un rendimiento superior:mayor tiempo de retención (RT) y una dependencia débil de la temperatura. Pero el rendimiento de la celda TFET DRAM es sensible a las condiciones de programación. En este artículo, la guía de optimización de la programación se analiza en detalle mediante el uso de la herramienta de simulación:Silvaco Atlas. Tanto las operaciones de escritura como de lectura de DG-TFET DRAM dependen de la tunelización banda a banda (BTBT). Durante la operación de escritura, los agujeros que provienen de BTBT gobernado por Gate2 se almacenan en un pozo de potencial debajo de Gate2. Se aplica un pequeño voltaje negativo en Gate2 para retener los orificios durante mucho tiempo mientras se mantiene presionado "1". El BTBT gobernado por Gate1 influye principalmente en la corriente de lectura. Usando la condición de programación optimizada, el DG-TFET DRAM obtiene la relación de corriente más alta de lectura "1" a lectura "0" (10 7 ) y RT de más de 2 s. El RT más alto reduce la frecuencia de actualización y el consumo dinámico de energía de la DRAM.

Antecedentes

La memoria dinámica de acceso aleatorio (DRAM) se ha convertido en una celda de memoria integral en el sistema móvil y de computación [1, 2, 3]. Con la contracción de la geometría del dispositivo, el gran volumen de condensador es una desventaja inherente para la celda DRAM tradicional de un transistor (1T) y un condensador (1C), lo que limita su aplicación a gran escala. La celda DRAM 1T sin condensador basada en el transistor de puerta flotante ha mostrado la ventaja potencial en comparación con la DRAM 1T-1C convencional para el empaquetado de memoria de alta densidad [4]. En el transistor de puerta flotante, las cargas en la región del sustrato se almacenan en la región de la puerta flotante mediante el túnel de Fowler-Nordheim. Y la operación de lectura depende de la emisión termoiónica [5, 6], que es la misma que la del transistor de efecto de campo semiconductor de óxido metálico (MOSFET). Como resultado, la corriente de lectura de la DRAM con el transistor de puerta flotante tiene una fuerte dependencia de la temperatura. Además, la emisión termoiónica hace que la oscilación del subumbral (SS) del transistor sea superior a 60 mV / dec, lo que hace que la alta corriente de fuga y el consumo de energía se conviertan en los principales desafíos [7,8,9].

Recientemente, el transistor de efecto de campo de efecto túnel (TFET) ha sido considerado como un candidato prometedor para los futuros dispositivos eléctricos de baja potencia [10, 11, 12]. El principal mecanismo de conducción de TFET es la tunelización banda a banda (BTBT) en lugar de la emisión termoiónica, lo que le permite obtener varias ventajas, como SS sub-60 mV / dec, baja corriente de fuga en estado apagado y dependencia débil de la temperatura. [13, 14]. Hasta ahora, una gran cantidad de trabajo de investigación sobre TFET se centra principalmente en el estudio del rendimiento del dispositivo de TFET único y algunos circuitos simples consisten en TFET. Sin embargo, el alto I en / Yo desactivado del TFET permite que sirva para la celda DRAM [15]. Especialmente, la corriente de fuga baja en estado apagado puede reducir la lectura de corriente "0" y el consumo de energía de la celda DRAM. Los investigadores han diseñado una DRAM TFET de doble puerta (DG-TFET) con estructura sin condensador [16]. En la DRAM DG-TFET, el almacenamiento de carga durante la operación de escritura se basa en el BTBT entre el canal y el drenaje, que es producido principalmente por Gate2. Al mismo tiempo, el efecto túnel de electrones promueve la acumulación de huecos en la región del canal debajo de Gate2. Gate1 es el principal responsable de la operación de lectura. La corriente de lectura de DGTFET DRAM se basa principalmente en el BTBT entre la región fuente y la región del canal. Hay algunos grupos de investigación que han demostrado que la corriente de lectura de DG-TFET DRAM tiene una dependencia débil de la temperatura. Y DG-TFET DRAM puede obtener un tiempo de retención superior al objetivo (64 ms) [17]. Pero la relación actual de lectura "1" a lectura "0" y RT no son el valor óptimo debido a la condición de programación no optimizada.

El rendimiento de TFET DRAM, especialmente la relación actual de lectura "1" a lectura "0", tiene una gran dependencia de la condición de programación. Gate2 influye principalmente en el BTBT durante la operación de escritura, que domina la región de almacenamiento de cargas y el potencial muy por debajo de Gate2. Gate1 gobierna el BTBT durante la operación de lectura, que influye principalmente en la corriente de lectura "1". Los sesgos adecuados de Gate1 y Gate2 pueden hacer que DGTFET DRAM obtenga la relación de corriente más alta. Existe poca literatura que estudia la influencia de la condición de programación en la lectura actual. En este documento, se propone una guía detallada de optimización de la programación, incluidas las operaciones de escritura, retención y lectura. Al aplicar la condición de programación optimizada, la DRAM DG-TFET obtiene el rendimiento óptimo:la relación de corriente de lectura de hasta 10 7 y el RT de más de 2 s. Y aplicando el voltaje de programación optimizado, la lectura de corriente “0” es mucho menor que la reportada en la referencia [16, 18], lo cual es útil para la reducción del consumo de energía.

Métodos

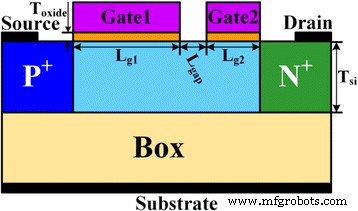

La estructura de DG-TFET investigada en este artículo se ilustra en la Fig. 1. La concentración de dopaje tanto de P + fuente y N + el drenaje es 1 × 10 20 / cm 3 . El canal intrínseco se divide en dos segmentos:Gate1 y Gate 2, y hay un pequeño espacio entre Gate1 y Gate2. Gate1 y Gate2 son N + polisilicio y P + polisilicio, respectivamente. El P + polysilicon Gate2 puede crear y mantener el pozo físico para el almacenamiento de carga y reemplazar la DRAM convencional basada en TFET que utiliza un P + región de bolsillo como área de almacenamiento. Mientras que para un N + polisilicio Gate1, la concentración de orificios en la región del traslapo entre Gate1 y Gate2 es baja, lo que es útil para la operación de lectura. Por lo tanto, una P + polysilicon Gate2 opta por tener una región de almacenamiento más profunda que podría facilitar una retención más prolongada, mientras que un N + Polysilicon Gate1 se selecciona para controlar el mecanismo de tunelización durante la operación de lectura [18].

Esquema de la celda DRAM DG-TFET. Esta figura muestra el esquema de la celda DRAM TFET (DGTFET) de doble puerta, que incluye Gate1, Gate2, fuente, drenaje y canal. En este diseño, la región de origen y la región de drenaje son P + dopaje y N + dopaje, respectivamente. Gate1 y Gate2 son N + polisilicio y P + polisilicio, respectivamente

Los parámetros detallados del dispositivo en las simulaciones son los siguientes:el espesor del silicio a granel ( T si ) es de 20 nm; las longitudes de Gate1 (Lg 1 ) y Gate2 (Lg 2 ) son 400 nm y 200 nm, respectivamente; la longitud del espacio ( L espacio ) entre Gate1 y Gate2 es 50 nm; el espesor del óxido de puerta (HfO 2 ) ( T óxido ) es de 3 nm. Las condiciones de programación optimizadas se muestran en la Tabla 1. Las pautas de optimización de las condiciones de programación se discutirán en detalle en las siguientes secciones.

Todo el análisis se lleva a cabo en la herramienta Silvaco-Atlas utilizando el modelo Nonlocal BTBT [19]. El BTBT no local tiene en cuenta la generación no local de electrones y huecos, por lo que puede modelar el proceso de tunelización con mayor precisión. Los parámetros del modelo de tunelización se calibran de acuerdo con los datos experimentales de la referencia [20]. Además, también se utilizan modelos físicos que incluyen la recombinación Shockley-Read-Hall, las estadísticas de Fermi, así como el dopaje y la movilidad dependiente del campo eléctrico. De acuerdo con los enfoques de [16, 18], la vida útil de los electrones y los huecos se establece en 100 ns. La temperatura predeterminada es 300 K.

Resultados y discusión

El principio de funcionamiento de la celda DRAM DG-TFET es diferente al de la DRAM tradicional. Tanto las operaciones de escritura como las de lectura se basan en el BTBT, pero cada una de ellas tiene una función diferente. El BTBT durante la escritura "1" hace que los agujeros se almacenen en el pozo de potencial debajo de Gate2, lo que puede elevar la corriente de lectura "1". Durante la operación de lectura, la corriente de drenaje depende principalmente del BTBT cerca del lado de la fuente. Además, las dos puertas también actúan como roles diferentes:Gate1 y Gate2 determinan principalmente la operación de lectura y escritura, respectivamente.

Operación de escritura

Durante la escritura "1", Gate2 con el sesgo negativo aumentará la banda de energía del canal debajo de Gate2, lo que disminuye el ancho de la barrera y produce el BTBT entre el canal y el drenaje. Y este sesgo negativo de Gate2 también induce un potencial profundo muy por debajo de Gate2. Debido al túnel de electrones del canal al drenaje, la región del canal debajo de Gate2 está completamente agotada y se acumulan muchos huecos en este pozo de potencial. Durante la escritura "0", Gate2 con el sesgo positivo hace que los agujeros se expulsen del pozo de potencial que se recombina en el lado del drenaje [21].

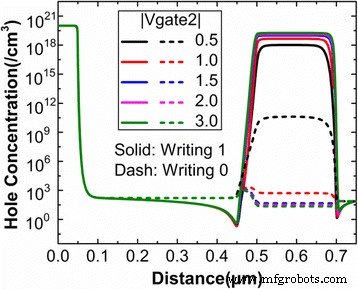

Generalmente, el valor absoluto del voltaje Gate2 se mantiene sin cambios para escribir "1" y escribir "0". La Figura 2 muestra la variación de la concentración de agujeros con el voltaje Gate2 después de la operación de escritura. Cuando el voltaje de Gate2 es 0.5 V, la concentración del agujero después de escribir "0" es mayor debido a la presencia de un pozo de potencial, lo cual es perjudicial para el estado "0". Cuando el valor absoluto del voltaje de Gate2 es superior a 1 V, la concentración del agujero después de escribir "0" y escribir "1" no tiene una variación obvia. Sugiere que BTBT está saturado para escribir "1" y que todos los agujeros acumulados durante la escritura "1" se expulsan del pozo de potencial después de escribir "0". Y la diferencia de concentración de huecos entre escribir "1" y escribir "0" es muy evidente, lo cual es beneficioso para distinguir entre el estado "1" y el estado "0".

Concentraciones de agujeros en la superficie del canal después de la operación de escritura. Esta figura muestra las variaciones de la concentración de agujeros con los diferentes voltajes de Gate2. La línea de corte se toma en la superficie del dispositivo desde la región de origen hasta la región de drenaje. En esta figura, la línea continua y la línea discontinua representan la concentración del agujero después de escribir "1" y escribir "0", respectivamente

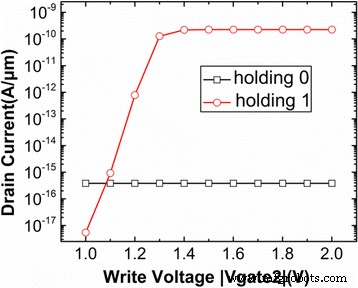

Pero el sesgo de Gate2 durante la operación de escritura no puede ser determinado únicamente por la concentración de agujeros. La Figura 3 indica que la polarización de Gate2 durante la operación de escritura tiene un efecto significativo en la corriente de drenaje después de la operación de retención. El conjunto de voltaje de programación durante la operación de retención se discutirá en la siguiente sección. La Figura 3 revela que la corriente de drenaje después de la operación de mantenimiento no tiene una variación obvia cuando el valor absoluto del voltaje de escritura es mayor que 1.3 V. Por lo tanto, los −1.3 y 1.3 V se consideran como el voltaje óptimo de Gate2 durante la escritura “1” y escribiendo "0", respectivamente.

Drene la corriente de DG-TFET después de mantener presionado "0" y mantener presionado "1". Esta figura muestra la variación de la corriente de drenaje después de mantener presionado "0" y mantener presionado "1" con respecto al voltaje de escritura

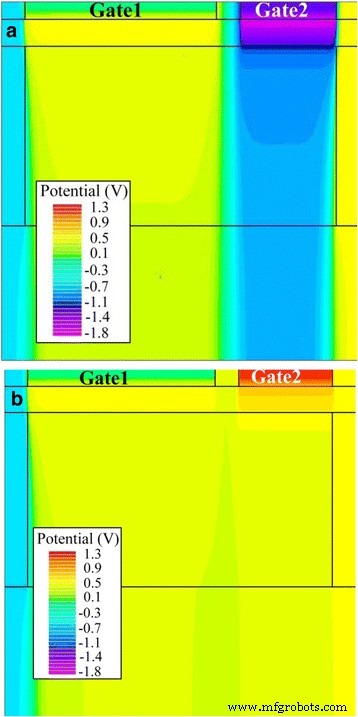

La Figura 4a, b indica respectivamente el contorno de potencial después de escribir "1" y escribir "0" cuando el valor absoluto del voltaje de escritura es 1.3 V. Obviamente, se crea un pozo de potencial muy profundo en la región del canal debajo de Gate2 después de escribir " 1 ”, como se muestra en la Fig. 4 a. Los agujeros acumulados se conservan en este pozo de potencial durante la escritura "1". Sin embargo, los agujeros acumulados escapan de este pozo potencial durante la escritura "0".

Contornos potenciales después de a escribiendo "1" y b escribir "0" cuando el valor absoluto del voltaje de Gate2 es 1.3 V. a , b Los contornos potenciales después de escribir "1" y escribir "0", respectivamente. Los contornos de potencial en esta figura se extraen cuando el valor absoluto del voltaje de Gate2 se establece en 1.3 V

Operación de retención

El proceso de retención se utiliza principalmente para modificar la retención de los cargos. Normalmente, la polarización cero se utiliza durante la operación de retención para reducir el consumo de energía [22]. Durante la operación de retención, los pozos acumulados en el pozo potencial se recombinan gradualmente debido a la disminución de la profundidad del pozo potencial. Por lo tanto, el objetivo principal de la optimización de la operación de retención es evitar la recombinación de agujeros durante la retención "1". En este diseño, se aplica un pequeño sesgo negativo en la Puerta2 para retener los agujeros en el pozo potencial después de mantener "1", mientras que el pozo potencial se agota después de mantener "0".

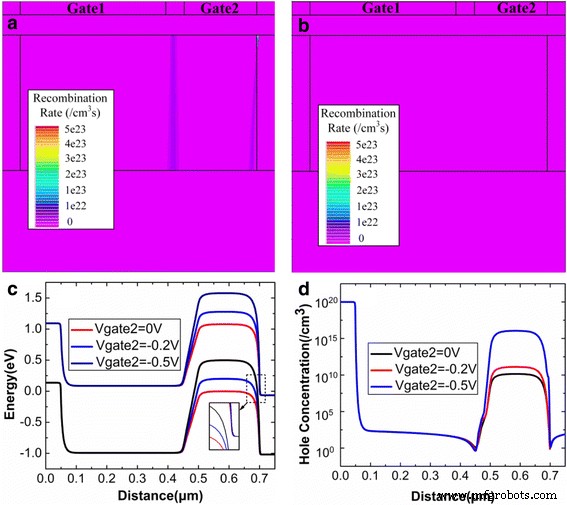

Con el voltaje Gate2 más negativo (−0,5 V) durante la operación de retención, la recombinación de agujeros se elimina después de mantener “1”, como se muestra en la Fig. 5a, b. La eliminación de la recombinación de huecos es beneficiosa para la retención de huecos durante la retención de "1". Se aplica un pequeño sesgo negativo en Gate2 para mejorar la profundidad del pozo potencial y retener los orificios durante mucho tiempo, lo que es beneficioso para el tiempo de retención de DGTFET DRAM. Mientras mantiene presionado "0", una polarización negativa de Gate2 puede tirar hacia arriba de la banda de energía de la región del canal debajo de Gate2, lo que puede evitar que los electrones provenientes de BTBT entre la fuente y el canal fluyan hacia el lado del drenaje. Por lo tanto, Gate2 con un negativo puede reducir la lectura de corriente "0". Sin embargo, Gate2 con más voltaje negativo (−0,5 V) disminuye la distancia de túnel cerca del lado del drenaje, como se muestra en la Fig. 5c. Esta menor distancia de túnel provoca el BTBT cerca del lado del drenaje durante el mantenimiento "0", lo que promueve la acumulación de agujeros en el pozo de potencial durante el mantenimiento "0", como se muestra en la Fig. 5d. Por lo tanto, el voltaje Gate2 más negativo (−0,5 V) durante el mantenimiento de "0" degradará el estado "0". Por lo tanto, para eliminar la recombinación de huecos y BTBT durante el mantenimiento de “1” y el mantenimiento de “0”, respectivamente, se considera que −0,2 V es la polarización óptima de Gate2 durante la operación de mantenimiento.

Tasa de recombinación en la celda DRAM DG-TFET después de mantener presionado "1" cuando el voltaje de Gate2 es a 0 V y b −0,5 V; c diagrama de bandas de energía y d concentración de agujeros después de mantener "0". un , b La tasa de recombinación después de mantener "1" cuando el voltaje de Gate2 se establece en 0 V y −0,5 V, respectivamente. c La banda de energía del dispositivo desde la región de origen a la región de drenaje. d La concentración de agujeros del dispositivo después de perforar "0". La banda de energía y la concentración del agujero se extraen a 3 nm por debajo del óxido de la puerta

Operación de lectura

Posteriormente, también se investiga la optimización de la operación de lectura. La operación de lectura se basa en gran medida en el BTBT entre P + fuente y canal. Durante la lectura “1”, Gate1 promueve principalmente el BTBT en el lado de la fuente, mientras que Gate2 con el alto voltaje reduce la barrera de energía que resiste el flujo de electrones del canal al drenaje. Pero durante la lectura "0", es necesario que Gate2 con el voltaje pequeño sea capaz de evitar que los electrones fluyan desde el canal para drenar. Por lo tanto, la optimización de los voltajes Gate1 y Gate2 es muy importante para la operación de lectura.

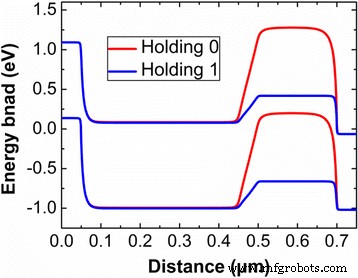

La Figura 6 muestra los diferentes diagramas de bandas de energía después de mantener presionado "1" y mantener presionado "0". Los mismos voltajes se aplican en los lados de la puerta durante la lectura "1" y la lectura "0". Dado que las polarizaciones positivas de la puerta se utilizarán durante la operación de lectura, la banda de energía se reducirá siempre que se lea "1" o "0". La banda de energía del canal debajo de Gate2 después de mantener presionado "0" es más alta que después de mantener presionado "1", y esta banda de energía también es más alta durante la lectura "0" en comparación con la de la lectura "1". La energía más alta del canal debajo de Gate2 creará una barrera efectiva para resistir los electrones que fluyen hacia el lado de drenaje, lo que disminuirá la lectura de corriente "0".

Diagrama de bandas de energía después de a sosteniendo "1" y b sosteniendo "0". un , b La banda de energía del dispositivo después de mantener presionado "1" y mantener presionado "0", respectivamente. La banda de energía se extrae a los 3 nm por debajo del óxido de la puerta

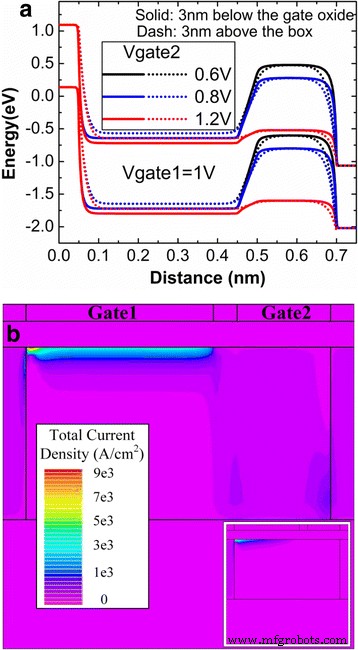

Durante la operación de lectura, la polarización de drenaje se establece en 1 V para que la corriente de drenaje se pueda leer en el DG-TFET. En primer lugar, manteniendo el voltaje de Gate1 de 1 V, cambie la polarización de Gate2 para elegir el voltaje óptimo de Gate2. Debido a que el voltaje Gate2 influye principalmente en la lectura de corriente "0", la optimización del voltaje Gate2 se analiza mediante el mecanismo de lectura "0". La Figura 7a traza la variación de la banda de energía con el voltaje de Gate2 después de leer "0". Cuando el voltaje de Gate2 es más bajo (0.6 o 0.8 V), el canal debajo de Gate2 se agota por completo. Pero cuando el voltaje de Gate2 aumenta a 1.2 V, la banda de energía desplegable del canal debajo de Gate2 no puede crear una barrera efectiva para evitar que los electrones fluyan hacia el lado del drenaje. La Figura 7b y su recuadro muestran respectivamente la densidad de corriente total después de leer "0" cuando el voltaje de Gate2 es 1V y 0.8 V. La densidad de corriente obvia se puede encontrar claramente en la región del canal debajo de Gate2 cuando el voltaje de Gate2 es 1 V, lo que dan lugar a la lectura más alta de corriente “0”. Por tanto, 0,8 V se considera el voltaje Gate2 óptimo para el proceso de lectura.

un Diagrama de bandas de energía y b densidad de corriente total después de leer "0". un , b La banda de energía y la densidad de corriente total después de leer "0", respectivamente. La banda de energía se extrae a los 3 nm por debajo del óxido de la puerta

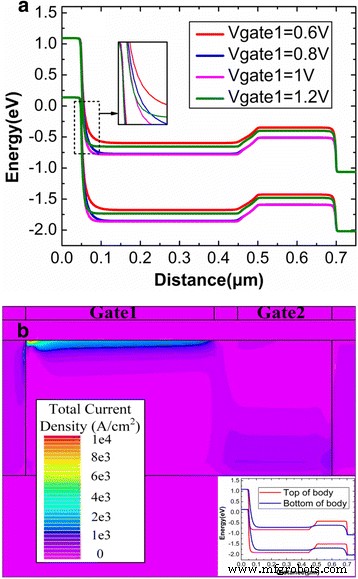

Finalmente, también se lleva a cabo la optimización del sesgo Gate1. La Figura 8a muestra la variación de la banda de energía superior con el voltaje de Gate1. El ancho de la barrera BTBT en el lado de la fuente disminuye gradualmente con el aumento del voltaje de Gate1, pero esta tendencia decreciente comienza a saturarse cuando el voltaje de Gate1 es mayor que 1 V. Y el voltaje de Gate1 de 1 V no puede tener una influencia severa en la lectura “0 ”, Que ha sido demostrado por la Fig. 7b. Por lo tanto, 1 V se considera el sesgo óptimo de Gate1 durante la operación de lectura.

un Diagrama de bandas de energía y b densidad de corriente total después de leer "1". un , b La banda de energía y la densidad de corriente total después de leer "1", respectivamente. La banda de energía se extrae a los 3 nm por debajo del óxido de la puerta

A través del análisis anterior, el pozo de potencial profundo solo se forma en la parte superior del canal debajo de Gate2 después de escribir “1”. Por lo tanto, en la región del canal debajo de Gate2, la banda de energía en la parte superior del canal es mucho más alta que en la parte inferior del canal. Esto demuestra que habrá una barrera en la parte superior del canal debajo de Gate2 durante la lectura “1”. El recuadro de la Fig. 8b traza la banda de energía en la parte superior e inferior del canal después de leer “1”. Se puede encontrar claramente que existe una barrera de canal más alta entre Gate1 y Gate2 en la parte superior del canal, pero esta barrera no existe en la parte inferior del canal. Por lo tanto, la ruta de conducción está en la parte superior del canal debajo de la Puerta 1 y la parte inferior del canal debajo de la Puerta 2 durante la lectura “1”, lo que se puede demostrar claramente por la densidad de corriente en la Fig. 8.

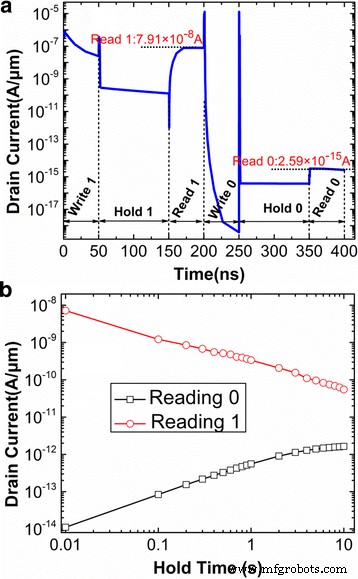

Aplicando la condición de programación optimizada anterior, la respuesta transitoria de la celda DRAM DG-TFET se muestra en la Fig. 9. Los tiempos de escritura y lectura se establecen en 50 ns, y el tiempo de retención se establece en 100 ns. En la Fig. 9a, la relación actual de lectura "1" a lectura "0" es tan alta como 10 7 , que es mucho mayor que 10 2 ~ 10 3 en la referencia [16, 18, 23]. Además, cuando el tiempo de retención aumenta a 10 s, la relación de corriente aún excede 10. En la referencia [16], cuando el tiempo de retención aumenta a 2 s, la relación de corriente es solo de aproximadamente 10. Por lo tanto, el RT de DG-TFET La DRAM con la condición de programación optimizada es superior a 2 s. Por lo tanto, la condición de programación optimizada hace que la celda DRAM DG-TFET obtenga no solo la relación de corriente de lectura más alta, sino también el RT más grande. Es más, la lectura de corriente "0" con voltaje de programación optimizado es mucho menor que la de la referencia [16, 18, 22, 23], lo que le permite cumplir con la aplicación de menor potencia.

un Corrientes de drenaje transitorias en la secuencia de la operación; b variación de la corriente de lectura con el tiempo de retención. un La corriente transitoria de la celda DGTFET DRAM durante las operaciones de escritura, retención y lectura. b Las variaciones de la lectura "1" y la lectura "0" de la corriente con los diferentes tiempos de vaciado

Conclusiones

La pauta de optimización detallada de la condición de programación para la DRAM DG-TFET se propone en este documento utilizando la herramienta de simulación Silvaco-Atlas. Durante la escritura "1", Gate2 con el voltaje negativo (−1,3 V) crea un pozo de potencial, y el BTBT entre el canal y el drenaje hace que los agujeros se acumulen en este pozo de potencial. Durante la escritura "0", Gate2 con el voltaje positivo (1.3 V) hace que los agujeros escapen del pozo de potencial. Para la operación de retención, se aplica una pequeña tensión negativa (−0,2 V) en la puerta 2 para retener los orificios, lo que puede mejorar la corriente de lectura "1". Después de mantener presionado "0", la barrera del canal debajo de Gate2 puede resistir los electrones que fluyen hacia el lado de drenaje para reducir la lectura "0" de corriente. Para optimizar la operación de lectura, el voltaje Gate1 más grande (1 V) se usa principalmente para mejorar el BTBT en el lado de la fuente durante la lectura "1", mientras que se usa un voltaje Gate2 apropiado (0.8 V) para resistir los electrones que fluyen hacia el drenaje durante la lectura. "0". La condición de programación optimizada hace que la DRAM DG-TFET obtenga la relación de corriente más alta (10 7 ) de lectura “1” a lectura “0” y tiempo de retención de más de 2 s. Y la lectura de corriente "0" extremadamente baja es útil para reducir el consumo de energía.

Nanomateriales

- Los beneficios del monitoreo remoto, la programación remota y el mantenimiento predictivo

- Dominar los desafíos de la programación y depuración multinúcleo

- Breadboard y programación del ATmega328P y ATtiny45 en Atmel Studio 7

- Aprenda el lenguaje de programación C integrado:comprensión del objeto de datos de unión

- Aprovechamiento de tecnologías basadas en IoT en el lugar de trabajo de construcción

- Sistema de seguridad biométrico basado en el latido del corazón humano

- Comentario:comprensión de los métodos de programación de robots

- El proceso de diseño e implementación de la automatización de la planta

- Rellene el espacio en blanco Ejercicio de programación CNC Arcos múltiples

- Complete el ejercicio de fresado de programación CNC en blanco

- Rellene el ejercicio de programación CNC en blanco