Detector de amplio rango de efecto de carga inducido por plasma para procesos CMOS BEOL avanzados

Resumen

Este trabajo propuso un detector de carga inducida por plasma (PID) modificado para ampliar el rango de detección, para monitorear el posible daño del plasma a través de una oblea durante los procesos CMOS BEOL avanzados. Se investigan nuevos diseños de antenas para patrones de daño inducidos por plasma con capacitores extendidos. Al adaptar los nuevos detectores PID, se han mejorado los niveles máximos de carga de los detectores.

Introducción

En los últimos años, la evolución de la tecnología de procesos de semiconductores continúa reduciendo la dimensión crítica en los circuitos integrados a gran escala [1, 2, 3]. Los procesos lógicos avanzados de FinFET se han vuelto más complejos para realizar transistores más compactos en chips Si multifuncionales y más potentes. Los pasos de grabado de iones reactivos mejorados por plasma [4, 5] se vuelven inevitables en procesos avanzados de nanoescala para lograr estructuras de alta relación de aspecto que son esenciales para circuitos de alta densidad de empaquetamiento [6]. Para los nodos de tecnología CMOS de más de 45 nm, las puertas del transistor cambiaron de la puerta convencional de polisilicio con dióxido de silicio a pilas de puertas metálicas de alto k [7, 8]. Este cambio hace que los dispositivos sean más susceptibles al daño inducido por el plasma y podría provocar daños latentes imprevistos en las capas dieléctricas de alta k. [9]. En los procesos de fabricación de última generación de FinFET, son inevitables numerosos pasos de plasma de RF, como los procesos de grabado, deposición y limpieza, que crean frecuencias más altas de eventos de carga inducidos por plasma [10]. Pueden producirse cargas tanto positivas como negativas en estructuras metálicas. A medida que estas cargas fluyen a través de las rutas conductoras hechas de líneas metálicas preexistentes, vías y contactos, la descarga indeseable a través de partes vulnerables de los circuitos, particularmente a través del dieléctrico de la puerta del transistor, puede conducir a problemas de confiabilidad significativos. Por ejemplo, en la etapa de grabado en seco, la dispersión de los iones que inciden y los materiales pulverizados en la superficie de reacción provocan más defectos en las aletas a granel [11, 12]. Para evitar el evento de carga de plasma que conduce a daños irreversibles a los circuitos, se dan reglas de diseño que limitan el tamaño de las estructuras metálicas. Otro ejemplo de alivio de la PID incluye el uso de diodos protectores, que podrían desviar la corriente de carga de plasma lejos de los circuitos sensibles [13]. La introducción del óxido de compuerta de generación de vapor in situ (ISSG) informó que ha mejorado su tolerancia al daño del plasma [14]. Además, también se encontró que recortar la cámara y modificar el proceso de deposición de PECVD-Ti aliviaba el daño inducido por el plasma [15]. Sin embargo, la mayoría de estos métodos dan como resultado limitaciones indeseables en la flexibilidad del diseño del circuito o en las compensaciones de procesamiento.

Convencionalmente, se han utilizado patrones de prueba en oblea para controlar los niveles de daño inducido por plasma (PID) [16]. El parámetro más común y ampliamente utilizado para monitorear el PID en la oblea son las características de tiempo de ruptura (TDDB) de las puertas de transistores con grandes estructuras de antena. El daño latente en los dieléctricos de la puerta se puede revelar midiendo la degradación de la capa dieléctrica de la puerta bajo pruebas de tensión de tensión o corriente. Por lo tanto, estos patrones no pueden proporcionar información en tiempo real sobre los procesos del plasma [17]. En nuestros trabajos anteriores, se demuestra un detector de efecto de carga inducida por plasma en oblea en tecnologías avanzadas de FinFET. El detector PID utiliza una estructura de acoplamiento capacitivo para inducir una respuesta en la puerta flotante [18,19,20]. Por lo tanto, no hay daño en la capa dieléctrica de la puerta como ocurre en un detector PID convencional. En estos nuevos detectores, se miden las curvas I – V cambiantes para averiguar tanto la intensidad, la duración como la polaridad de las cargas en la puerta de la antena. Se encuentra que estos detectores pueden estar sujetos a un efecto de saturación ya que la intensidad del plasma en ciertos sitios de registro excede los niveles críticos. Para ampliar el rango dinámico del detector PID, en este trabajo se han investigado nuevos diseños de puertas de antena, donde se demuestra con éxito la ampliación de los rangos de detección.

Métodos

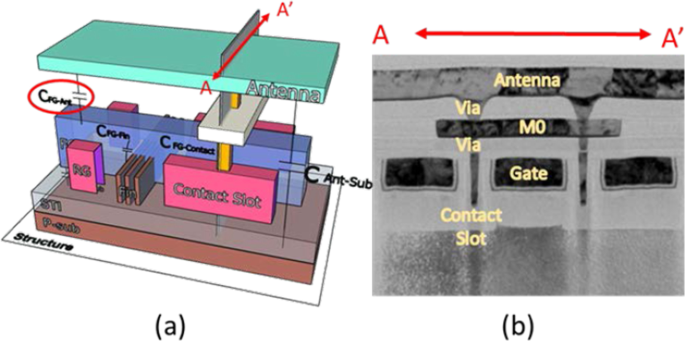

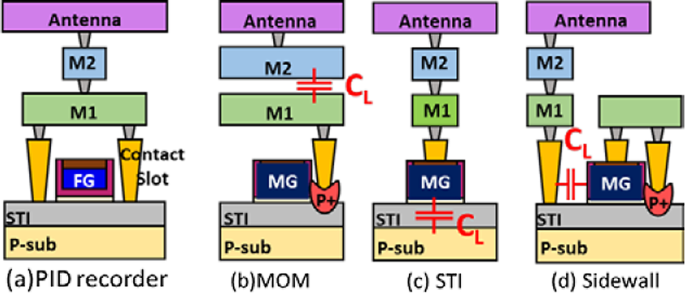

El esquema 3D del detector de daño inducido por plasma (PID) con un condensador parásito conectado al nodo de la antena se muestra en la Fig. 1a. A diferencia de la estructura de monitoreo PID, este detector utiliza una ranura de contacto larga para acoplar el voltaje de la antena en la puerta flotante. La fotografía TEM en sección transversal se muestra en la Fig. 1b. Como se muestra en la figura, las ranuras de contacto que recolectan cargas están acopladas capacitivamente a la puerta flotante.

un Las ilustraciones en 3D del detector PID in situ y el condensador de la antena informados anteriormente se destacan en esta estructura. b La foto TEM del detector PID, donde la longitud de la puerta de este detector es de 140 nm

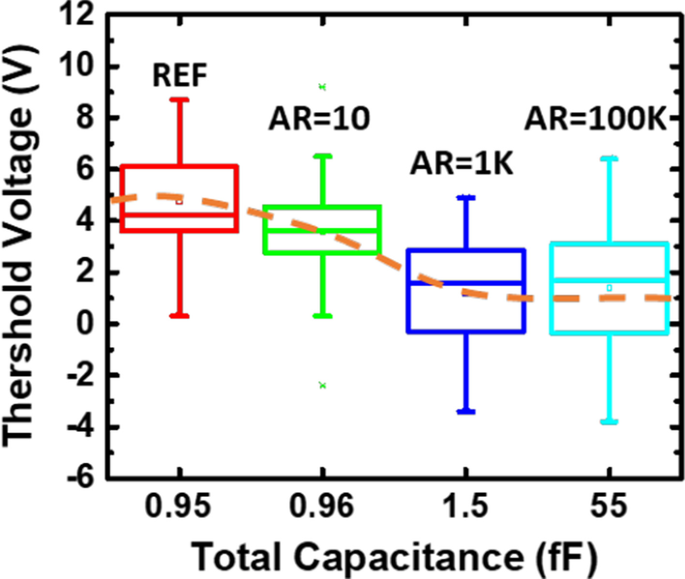

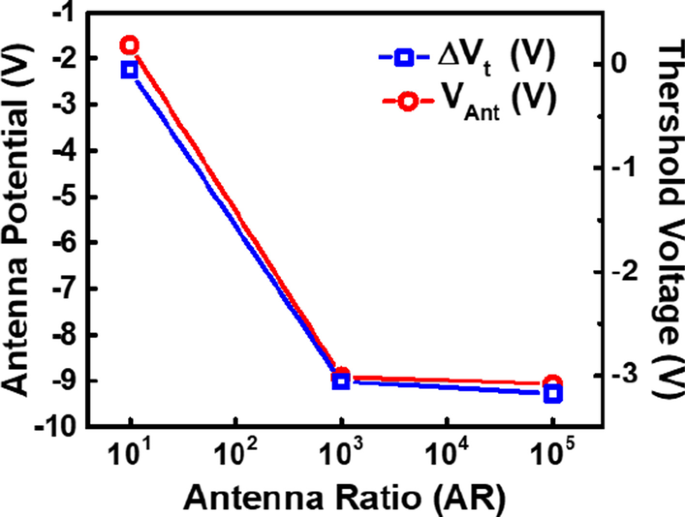

La Figura 2 compara las distribuciones de voltaje de umbral registradas de estos detectores en una oblea de 12 pulgadas. El cambio de voltaje de umbral negativo indica que se acumularon cargas negativas en la antena, lo que atrae cargas positivas hacia la puerta flotante, lo que resulta en cambios de voltaje de umbral negativos. Se encuentra que a medida que aumenta el área de la antena, la capacitancia total en aumento conduce a la disminución de los voltajes generales de la antena, por lo tanto, el cambio en V es menor. t .

Rango de voltaje de umbral de muestras con diferentes tamaños de antena y la capacitancia total correspondiente en la antena

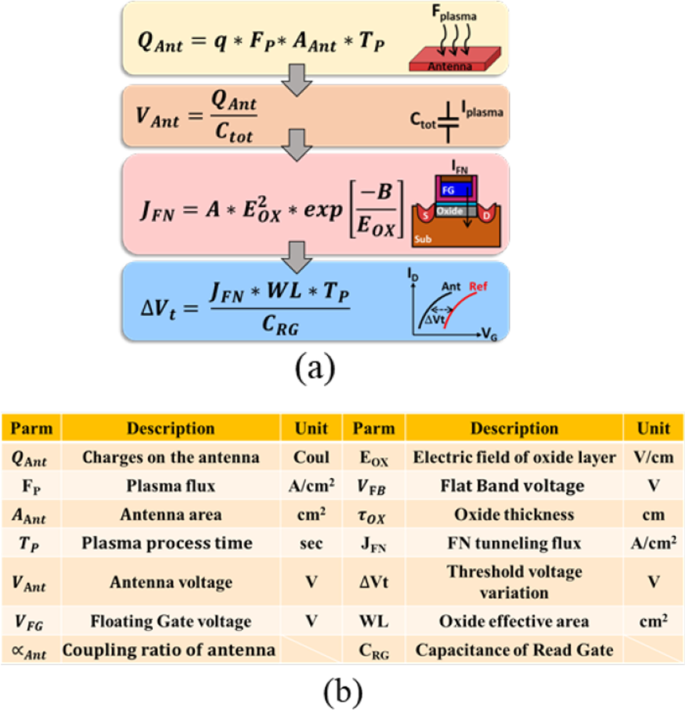

Aquí, en la figura 3a, se describe el diagrama de flujo que explica los principios básicos de funcionamiento del detector PID. Como la carga de plasma ( Q Hormiga ) se recogen en la antena, el potencial de la puerta de la antena, V Hormiga , varía. V Hormiga luego se acopla a la puerta flotante (FG), lo que promueve el túnel de electrones dentro o fuera de FG. Después de los procesos de plasma, V t de estos detectores pueden volverse más negativos o más positivos según la polaridad de Q Hormiga . V t se puede calcular mediante el modelo de corriente de tunelización FN con el parámetro enumerado en la Fig. 3b.

un El diagrama de flujo de las cargas de plasma ( Q Hormiga ) recogido en la antena para cambiar V t . Basado en el modelo de tunelización FN, Δ V t se puede calcular. b La lista de parámetros con sus definiciones

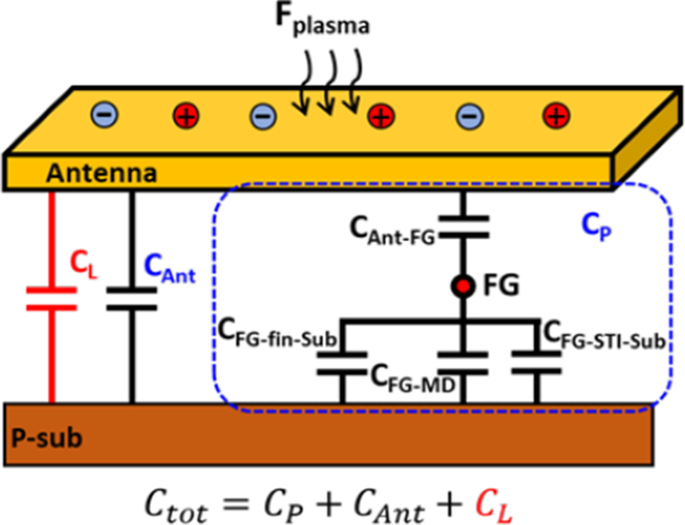

La Figura 4 ilustra toda la capacitancia posible en el detector PID basado en FG. De la Fig.5, se encuentra que a medida que aumenta el área de la antena, Δ V t tiende a saturarse. Como V Hormiga alcanza los niveles máximos, Q Hormiga comienza a filtrarse cuando el nivel de voltaje es demasiado alto. Para evitar que el nivel de flujo de plasma exceda la limitación del detector, la capacitancia de la antena se aumenta deliberadamente agregando capacitores de carga que podrían reducir la proporción de capacitancia de la antena en la capacitancia total.

Composición de la capacitancia en la estructura de la antena con el capacitor de carga adicional, que está diseñado para modificar la sensibilidad de los detectores PID. Donde C P es la capacitancia parásita total en la puerta flotante

Tanto el nivel de voltaje de umbral como el nivel de voltaje de antena proyectado se saturan en patrones con área de antena aumentada

La Figura 6a muestra la estructura 2D del detector PID in situ del que se informó anteriormente, y se presentan tres estructuras de realización de condensadores adicionales. Son condensadores MOM, que utilizan el área de superposición más grande de las capas metálicas para aumentar la capacitancia total en la Fig.6b, capacitores STI, que aumentan la capacitancia ajustando la longitud de la puerta metálica en la Fig.6c, y capacitores de pared lateral, que usan el área de superposición de la puerta de metal y el contacto para formar un condensador adicional Fig. 6d.

Ilustración en sección transversal de a el detector PID in situ, y aquellos con un condensador adicional de carga realizado por b MAMÁ, c ITS y d pared lateral, respectivamente

Discusión y resultados experimentales

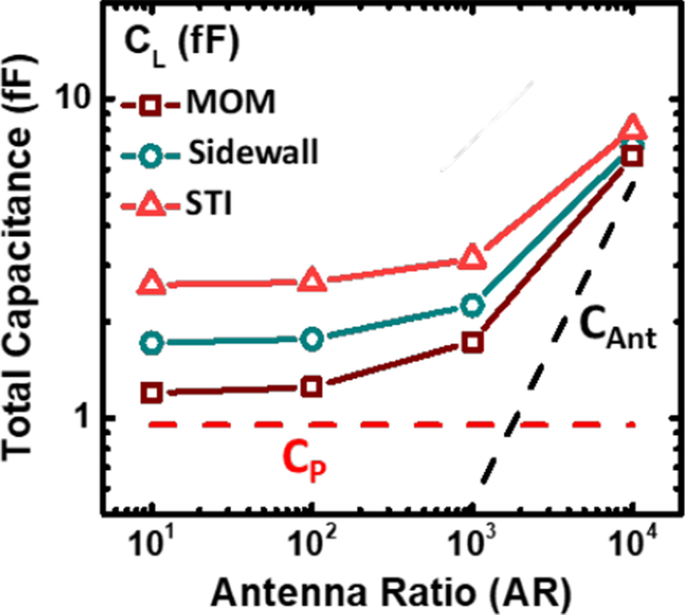

La Figura 7 compara la capacitancia total versus las relaciones de antena cuando se agregan diferentes tipos de capacitores de carga. La capacitancia total está dominada por la capacitancia de la antena cuando la relación de la antena es superior a 1 K.

Comparación de la capacitancia total frente a las relaciones de antena a medida que se agregan los tres tipos de capacitores de carga

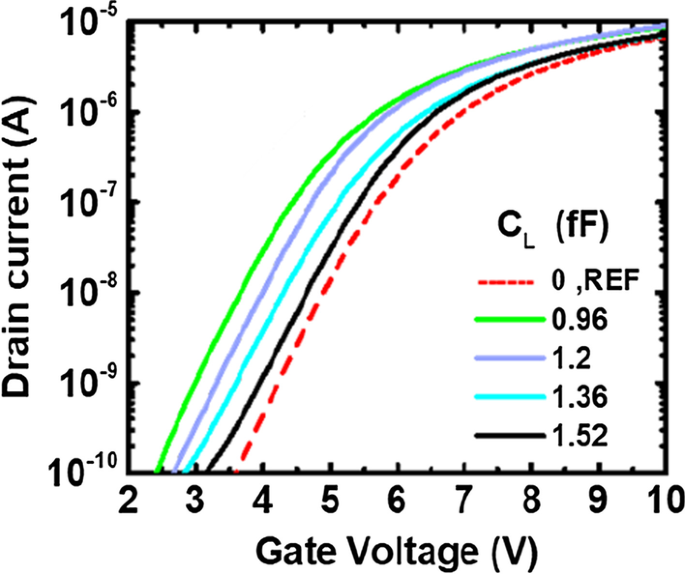

Cuando la capacitancia de carga agregada se vuelve comparable a la capacitancia de la antena, la capacitancia total podría verse afectada por los capacitores de carga. Dado que la cantidad máxima de cargas recolectadas por la antena es fija; aumentando la capacitancia total, Δ V se espera que disminuya, de acuerdo con Δ Q = C Δ V . Por lo tanto, la sensibilidad del rango de detección podría suprimirse, evitando el efecto de saturación cuando el nivel de carga de plasma excede sus límites originales. Las características de corriente de drenaje para dispositivos de AR =10 con diferentes capacitores STI se comparan en la Fig. 8. Cuando se agrega un capacitor de carga más grande, el porcentaje de capacitancia de la antena en capacitancia total se reduce. Bajo el mismo flujo de carga de plasma, las cargas totales de plasma después de un período son proporcionales al área de la antena. Por lo tanto, cuando aumenta la capacitancia general, V Hormiga Se espera que se reduzca, lo que permite la detección de altos niveles de flujo plasmático. Como se muestra en la Fig. 8, se encuentran cambios más pequeños en las curvas I – V para las muestras con capacitores de carga adicionales.

Curva I – V de diferentes tamaños de condensador STI con AR =10. Cuando la capacitancia externa es mayor, la curva I – V está más cerca de la de las celdas de referencia

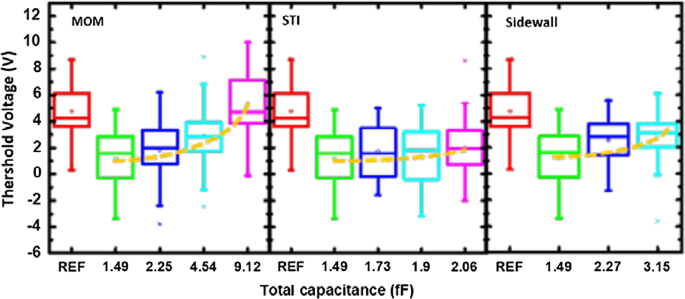

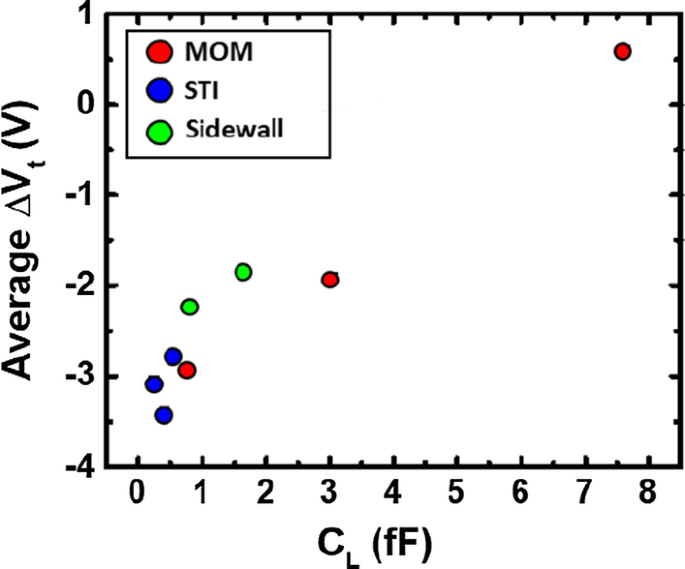

Los gráficos de caja de los voltajes de umbral medidos a partir de muestras con AR =1 K y diferentes tamaños de condensadores MOM, STI y de pared lateral se comparan en la Fig.9 Cuando se aumenta la capacitancia de carga, se observa menos cambio de voltaje de umbral en promedio. En el diseño experimental, C L por estructura de STI es demasiado pequeño para mostrar el impacto del nivel de carga. La comparación en la Fig. 10 sugirió que tres formas de agregar condensadores de carga también pueden reducir efectivamente la respuesta promedio a la carga de plasma. El condensador de carga adicional puede ampliar con éxito el rango de detección del detector PID, mientras que se reduce la sensibilidad de los detectores. Para lograr una detección de amplio rango del nivel de carga de plasma, una serie de detectores PID con diferentes niveles de C L se puede diseñar en una matriz 1-D para detectar niveles de carga de plasma tanto en el extremo alto como en el bajo.

Se comparan los voltajes de umbral medidos en muestras con diferentes tamaños de condensadores MOM, STI y Sidewall. Todos los dispositivos tienen el mismo AR de 1 K

Comparación de la media Δ V t versus C L implementado por los tres tipos de estructuras de condensadores, donde Δ V t se define como la V t diferencia entre una celda detectora y la celda de referencia. Los datos sugieren que se puede obtener una sensibilidad reducida como C L aumentado

Conclusiones

Este estudio investiga un nuevo diseño de puerta de antena para extender el rango de detección de niveles de carga inducidos por plasma en los detectores de monitoreo PID. Al agregar un capacitor de carga, se puede prevenir un voltaje alto en la puerta de la antena sujeto a fugas de carga, lo que permite registrar un nivel más alto de nivel de carga en los detectores PID. Este novedoso diseño amplía efectivamente el rango de detección de niveles de carga de plasma en procesos CMOS BEOL avanzados.

Disponibilidad de datos y material

No aplica.

Abreviaturas

- PID:

-

Daño inducido por plasma

- V t :

-

Voltaje umbral

- Q Hormiga :

-

Cargas en la antena

- V Hormiga :

-

Voltaje de la antena

- MAMÁ:

-

Metal-óxido-metal

- AR:

-

Relación de antena

- C L :

-

Capacidad de carga

- C P :

-

Capacitancia parasitaria

- C Hormiga :

-

Capacitancia de la antena

Nanomateriales

- Circuito de puerta CMOS

- Python para bucle

- Los investigadores de IBM se llevan el premio a la innovación en investigación de semiconductores

- Tecnologías avanzadas de deposición de capas atómicas para micro-LED y VCSEL

- Nanopartículas de quitosano cargadas con genisteína y bioflavonoides dirigidas al receptor de folato para un efecto anticancerígeno mejorado en los cánceres de cuello uterino

- El efecto del plasma de no equilibrio por contacto sobre las propiedades estructurales y magnéticas de Mn Х Fe3 - X О4 Espinelas

- Grabador in situ de división de carga (CSIR) para el examen en tiempo real del efecto de carga de plasma en procesos FinFET BEOL

- Efecto de campo ferroeléctrico Inducido por efecto de conmutación asimétrica resistiva en BaTiO3 / Nb:Heterouniones epitaxiales SrTiO3

- Síntesis e investigación de nanocables de CuGeO3 como materiales anódicos para baterías avanzadas de iones de sodio

- Diseño de patrón de prueba para daño inducido por plasma en dieléctrico inter-metálico en procesos FinFET Cu BEOL

- Efecto del tratamiento activado criogénico profundo sobre el carbón derivado del tallo de cáñamo utilizado como ánodo para baterías de iones de litio