Circuito de puerta CMOS

Hasta este punto, nuestro análisis de los circuitos lógicos de transistores se ha limitado al TTL paradigma de diseño, mediante el cual se utilizan transistores bipolares, y la estrategia general de entradas flotantes es equivalente a "alto" (conectado a V cc ) entradas y, en consecuencia, se mantiene la tolerancia de las etapas de salida de “colector abierto”. Sin embargo, esta no es la única forma en que podemos construir puertas lógicas.

Transistores de efecto de campo

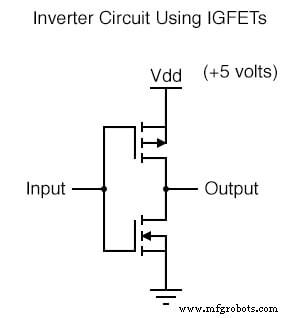

Los transistores de efecto de campo, particularmente la variedad de puerta aislada, se pueden usar en el diseño de circuitos de puerta. Al ser dispositivos controlados por voltaje en lugar de controlados por corriente, los IGFET tienden a permitir diseños de circuitos muy simples. Tomemos, por ejemplo, el siguiente circuito inversor construido con IGFET de canal P y N:

Observe el "V dd ”Etiqueta en el terminal positivo de la fuente de alimentación. Esta etiqueta sigue la misma convención que "V cc ”En circuitos TTL:representa el voltaje constante aplicado al drenaje de un transistor de efecto de campo, en referencia a tierra.

Transistores de efecto de campo en circuitos de puerta

Entrada baja

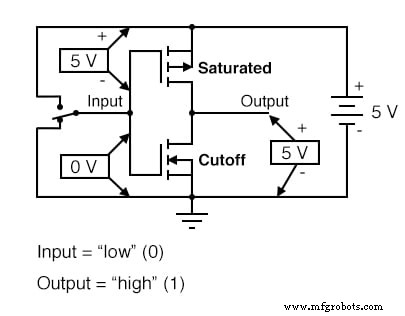

Conectemos este circuito de puerta a una fuente de alimentación y un interruptor de entrada, y examinemos su funcionamiento. Tenga en cuenta que estos transistores IGFET son de tipo E (modo de mejora), por lo que son normalmente desactivados dispositivos.

Se necesita un voltaje aplicado entre la puerta y el drenaje (en realidad, entre la puerta y el sustrato) de la polaridad correcta para polarizarlos en .

El transistor superior es un IGFET de canal P. Cuando el canal (sustrato) se hace más positivo que la puerta (puerta negativa en referencia al sustrato), el canal se mejora y se permite la corriente entre la fuente y el drenaje.

Entonces, en la ilustración anterior, el transistor superior está encendido. El transistor inferior, que tiene voltaje cero entre la puerta y el sustrato (fuente), está en su modo normal: apagado .

Por lo tanto, la acción de estos dos transistores es tal que el terminal de salida del circuito de la puerta tiene una conexión sólida a V dd y una conexión a tierra de muy alta resistencia. Esto hace que la salida sea "alta" (1) para el estado "bajo" (0) de la entrada.

Entrada alta

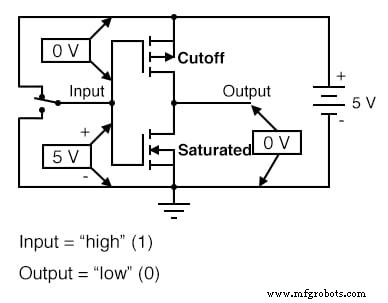

A continuación, moveremos el interruptor de entrada a su otra posición y veremos qué sucede:

Ahora el transistor inferior (canal N) está saturado porque tiene suficiente voltaje de la polaridad correcta aplicada entre la puerta y el sustrato (canal) para encenderlo (positivo en la puerta, negativo en el canal). El transistor superior, que tiene cero voltaje aplicado entre su puerta y sustrato, está en su modo normal: apagado .

Por lo tanto, la salida de este circuito de puerta ahora es "baja" (0). Claramente, este circuito exhibe el comportamiento de un inversor, o NO puerta.

Semiconductores complementarios de óxido metálico (CMOS)

El uso de transistores de efecto de campo en lugar de transistores bipolares ha simplificado enormemente el diseño de la puerta del inversor. Tenga en cuenta que la salida de esta puerta nunca flota como es el caso del circuito TTL más simple:tiene una configuración natural de "tótem-polo", capaz de generar y absorber corriente de carga.

La clave del elegante diseño de este circuito de puerta es el complementario uso de IGFET de canal P y canal N. Dado que los IGFET se conocen más comúnmente como MOSFET ( M etal- O xide- S emiconductor F campo E efecto T ransistor), y este circuito usa transistores de canal P y N juntos, la clasificación general dada a los circuitos de puerta como este es CMOS : C M complementario etal O xide S emiconductor.

Puertas CMOS:desafíos y soluciones

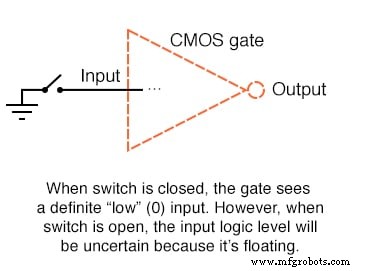

Los circuitos CMOS no están plagados de las no linealidades inherentes de los transistores de efecto de campo, porque como circuitos digitales, sus transistores siempre operan en el saturado o corte modos y nunca en el activo modo. Sin embargo, sus entradas son sensibles a los altos voltajes generados por fuentes electrostáticas (electricidad estática), e incluso pueden activarse en estados "alto" (1) o "bajo" (0) por fuentes de voltaje falso si se dejan flotando.

Por esta razón, no es aconsejable permitir que una entrada de puerta lógica CMOS flote bajo ninguna circunstancia. Tenga en cuenta que esto es muy diferente del comportamiento de una puerta TTL donde una entrada flotante se interpretó de manera segura como un nivel lógico "alto" (1).

Problemas de CMOS con entradas flotantes

Esto puede causar un problema si la entrada a una puerta lógica CMOS es impulsada por un interruptor de un solo tiro, donde un estado tiene la entrada conectada sólidamente a V dd o tierra y el otro estado tiene la entrada flotante (no conectada a nada):

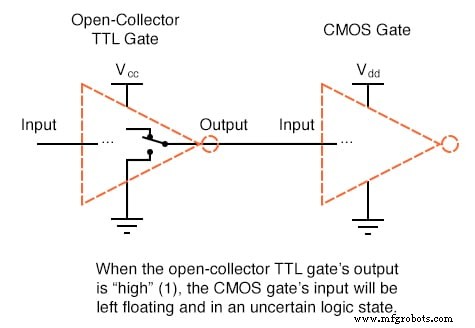

Además, este problema surge si una entrada de puerta CMOS está siendo impulsada por un colector abierto Puerta TTL. Debido a que la salida de una puerta TTL de este tipo flota cuando se pone "alta" (1), la entrada de la puerta CMOS se dejará en un estado incierto:

Solución para entradas flotantes

Resistencias pullup

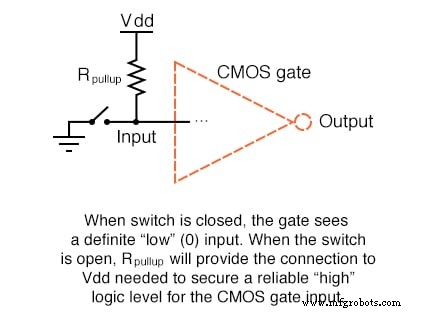

Afortunadamente, existe una solución fácil para este dilema, una que se usa con frecuencia en los circuitos lógicos CMOS. Siempre que un interruptor de un solo tiro (o cualquier otro tipo de salida de puerta incapaz de ambos fuente y sumidero de corriente) se utiliza para impulsar una entrada CMOS, una resistencia conectada a V dd o tierra se puede utilizar para proporcionar un nivel lógico estable para el estado en el que la salida del dispositivo de conducción está flotando.

El valor de esta resistencia no es crítico:10 kΩ suele ser suficiente. Cuando se utiliza para proporcionar un nivel lógico "alto" (1) en el caso de una fuente de señal flotante, esta resistencia se conoce como resistencia pullup :

Resistencias pulldown

Cuando se utiliza una resistencia de este tipo para proporcionar un nivel lógico "bajo" (0) en el caso de una fuente de señal flotante, se conoce como una resistencia pulldown . Nuevamente, el valor de una resistencia pulldown no es crítico:

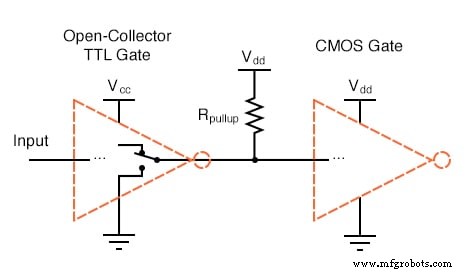

Debido a que las salidas TTL de colector abierto siempre se hunden, nunca generan, actualizan, suben hacia arriba Las resistencias son necesarias cuando se conecta una salida de este tipo a una entrada de puerta CMOS:

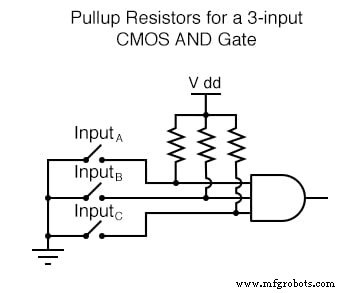

Varias resistencias pullup y pulldown

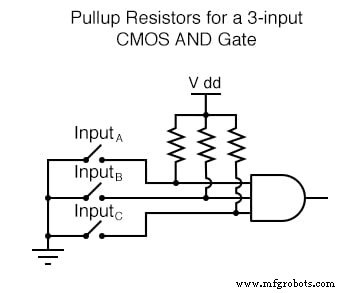

Aunque las puertas CMOS utilizadas en los ejemplos anteriores eran todas inversores (entrada única), el mismo principio de resistencias pullup y pulldown se aplica a las puertas CMOS de múltiples entradas. Por supuesto, se requerirá una resistencia pullup o pulldown separada para cada entrada de puerta:

Esto nos lleva a la siguiente pregunta:¿cómo diseñamos puertas CMOS de múltiples entradas como AND, NAND, OR y NOR? No es sorprendente que la (s) respuesta (s) a esta pregunta revelen una simplicidad de diseño muy similar a la del inversor CMOS sobre su equivalente TTL.

Puertas NAND CMOS

Por ejemplo, aquí está el diagrama esquemático de una puerta CMOS NAND:

Observe cómo los transistores Q 1 y Q 3 parecerse al par complementario conectado en serie del circuito inversor. Ambos están controlados por la misma señal de entrada (entrada A), el transistor superior se apaga y el transistor inferior se enciende cuando la entrada es "alta" (1), y viceversa.

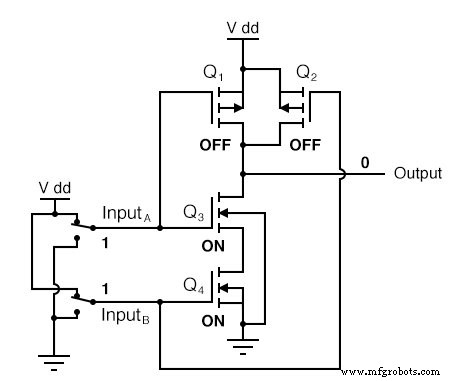

Observe también cómo los transistores Q 2 y Q 4 son controlados de manera similar por la misma señal de entrada (entrada B), y también exhibirán el mismo comportamiento de encendido / apagado para los mismos niveles lógicos de entrada. Los transistores superiores de ambos pares (Q 1 y Q 2 ) tienen sus terminales de fuente y drenaje en paralelo, mientras que los transistores inferiores (Q 3 y Q 4 ) están conectados en serie.

Lo que esto significa es que la salida será "alta" (1) si o el transistor superior se satura y pasará a "bajo" (0) solo si ambos los transistores inferiores se saturan.

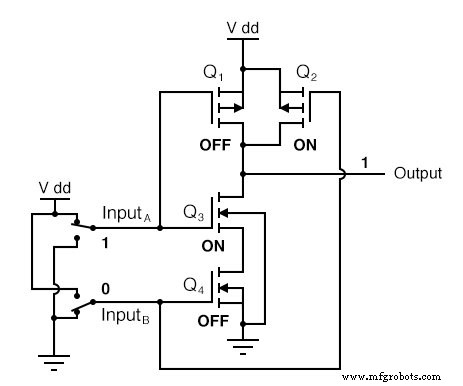

Comportamientos del circuito CMOS para todas las entradas lógicas

La siguiente secuencia de ilustraciones muestra el comportamiento de esta puerta NAND para las cuatro posibilidades de niveles lógicos de entrada (00, 01, 10 y 11):

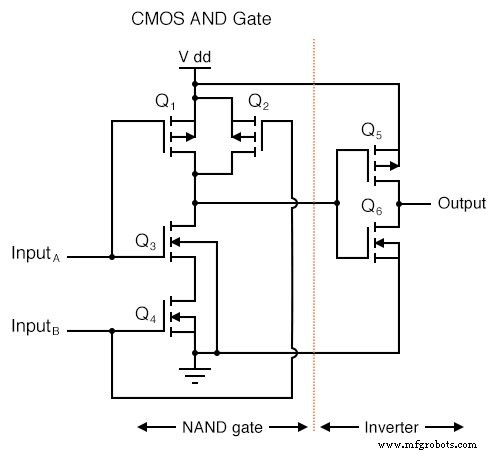

CMOS Y puerta

Al igual que con la puerta TTL NAND, el circuito de puerta CMOS NAND se puede utilizar como punto de partida para la creación de una puerta AND. Todo lo que necesita agregar es otra etapa de transistores para invertir la señal de salida:

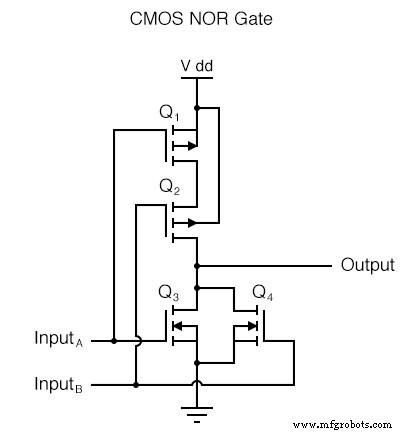

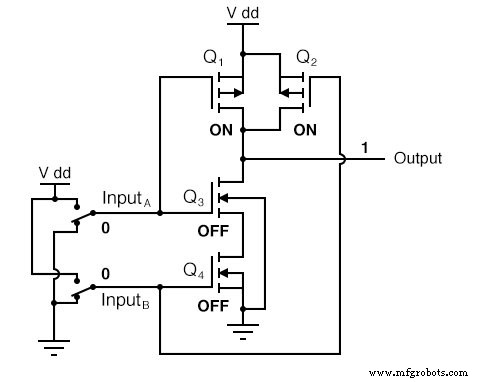

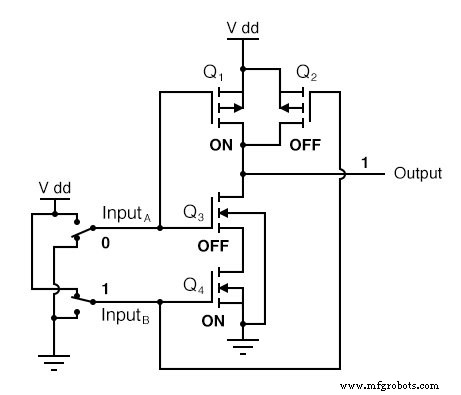

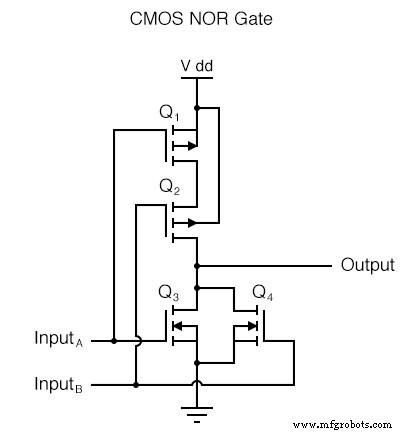

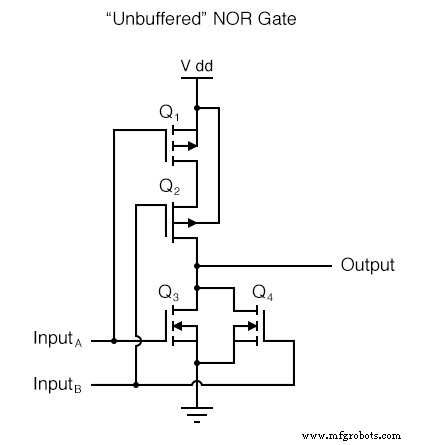

Puertas NOR CMOS

Un circuito de puerta CMOS NOR usa cuatro MOSFET al igual que la puerta NAND, excepto que sus transistores están dispuestos de manera diferente. En lugar de dos abastecimiento en paralelo transistores (superiores) conectados a V dd y dos hundimiento conectados en serie transistores (inferiores) conectados a tierra, la puerta NOR utiliza dos transistores de origen conectados en serie y dos transistores de hundimiento conectados en paralelo como este:

Al igual que con la puerta NAND, los transistores Q 1 y Q 3 funcionan como un par complementario, al igual que los transistores Q 2 y Q 4 . Cada par está controlado por una única señal de entrada. Si cualquiera ingrese A o entrada B son "altas" (1), al menos uno de los transistores inferiores (Q 3 o Q 4 ) se saturará, lo que hará que la salida sea "baja" (0).

Solo en el caso de ambos Si las entradas son “bajas” (0), ambos transistores inferiores estarán en modo de corte y ambos transistores superiores estarán saturados, las condiciones necesarias para que la salida sea “alta” (1). Este comportamiento, por supuesto, define la función lógica NOR.

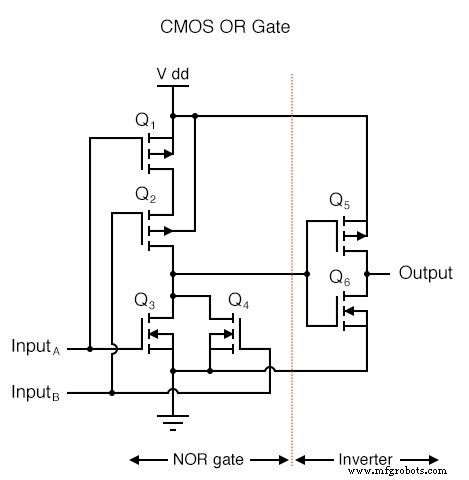

Puertas OR CMOS

La función OR puede construirse a partir de la puerta NOR básica con la adición de una etapa inversora en la salida:

TTL frente a CMOS:ventajas y desventajas

Dado que parece que cualquier puerta posible de construir usando tecnología TTL se puede duplicar en CMOS, ¿por qué estas dos "familias" de diseño lógico todavía coexisten? La respuesta es que tanto TTL como CMOS tienen sus propias ventajas únicas.

En primer lugar, en la lista de comparaciones entre TTL y CMOS está la cuestión del consumo de energía. En esta medida de desempeño, CMOS es el vencedor indiscutible. Debido a que los pares MOSFET complementarios de canal P y N de un circuito de compuerta CMOS (idealmente) nunca conducen al mismo tiempo, el circuito extrae poca o ninguna corriente del V dd fuente de alimentación, excepto la corriente necesaria para suministrar corriente a una carga. TTL, por otro lado, no puede funcionar sin algo de corriente consumida en todo momento, debido a los requisitos de polarización de los transistores bipolares de los que está hecho.

Sin embargo, hay una salvedad sobre esta ventaja. Mientras que la disipación de potencia de una puerta TTL permanece bastante constante independientemente de su (s) estado (s) de funcionamiento, una puerta CMOS disipa más potencia a medida que aumenta la frecuencia de su (s) señal (es) de entrada. Si una puerta CMOS se opera en una condición estática (sin cambios), disipa energía cero (idealmente).

Sin embargo, los circuitos de compuerta CMOS consumen corriente transitoria durante cada cambio de estado de salida de "bajo" a "alto" y viceversa. Por lo tanto, cuanto más a menudo cambia de modo una puerta CMOS, más a menudo extraerá corriente del V dd suministro, por lo tanto, una mayor disipación de potencia a mayores frecuencias.

Ventajas de CMOS

Una puerta CMOS también consume mucha menos corriente de una salida de puerta de conducción que una puerta TTL porque los MOSFET son dispositivos controlados por voltaje, no controlados por corriente. Esto significa que una puerta puede manejar muchas más entradas CMOS que entradas TTL. La medida de cuántas entradas de puerta puede impulsar una salida de puerta única se llama fanout .

Otra ventaja que disfrutan los diseños de compuertas CMOS sobre TTL es un rango permisible mucho más amplio de voltajes de fuente de alimentación. Mientras que las puertas TTL están restringidas a la fuente de alimentación (V cc ) voltajes entre 4,75 y 5,25 voltios, las compuertas CMOS normalmente pueden operar con cualquier voltaje entre 3 y 15 voltios.

La razón detrás de esta disparidad en los voltajes de la fuente de alimentación son los requisitos de polarización respectivos de MOSFET frente a los transistores de unión bipolar. Los MOSFET están controlados exclusivamente por voltaje de puerta (con respecto al sustrato), mientras que los BJT son controlados por corriente dispositivos.

Las resistencias del circuito de puerta TTL se calculan con precisión para las corrientes de polarización adecuadas, asumiendo una fuente de alimentación regulada de 5 voltios. Cualquier variación significativa en ese voltaje de la fuente de alimentación dará como resultado que las corrientes de polarización del transistor sean incorrectas, lo que luego dará como resultado un funcionamiento poco confiable (impredecible).

El único efecto que tienen las variaciones en el voltaje de la fuente de alimentación en una puerta CMOS es la definición de voltaje de un estado "alto" (1). Para una puerta CMOS que opera a 15 voltios de voltaje de fuente de alimentación (V dd ), una señal de entrada debe estar cerca de los 15 voltios para ser considerada “alta” (1). El umbral de voltaje para una señal "baja" (0) sigue siendo el mismo:cerca de 0 voltios.

Desventajas de CMOS

Una clara desventaja de CMOS es la velocidad lenta, en comparación con TTL. Las capacitancias de entrada de una puerta CMOS son mucho, mucho mayores que las de una puerta TTL comparable, debido al uso de MOSFET en lugar de BJT, por lo que una puerta CMOS responderá más lentamente a una transición de señal (de baja a alta o viceversa) que una puerta TTL, todos los demás factores son iguales.

La constante de tiempo RC formada por las resistencias del circuito y la capacitancia de entrada de la puerta tienden a impedir los rápidos tiempos de subida y bajada de un nivel lógico digital, degradando así el rendimiento de alta frecuencia.

Estrategias para combatir las desventajas

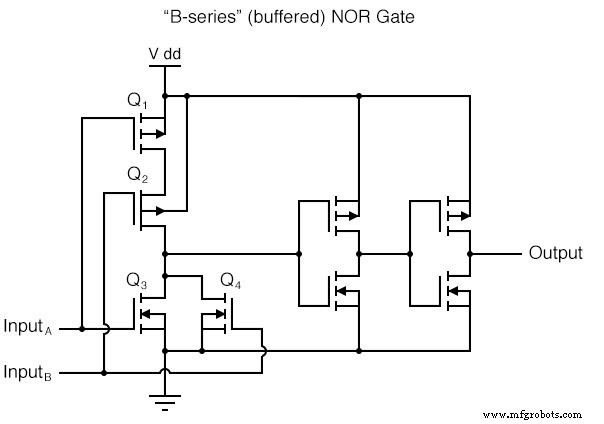

Una estrategia para minimizar esta desventaja inherente de los circuitos de compuerta CMOS es "amortiguar" la señal de salida con etapas de transistor adicionales, para aumentar la ganancia de voltaje general del dispositivo. Esto proporciona un voltaje de salida de transición más rápida (de alto a bajo o de bajo a alto) para un voltaje de entrada que cambia lentamente de un estado lógico a otro.

Considere este ejemplo, de una puerta NOR "sin búfer" frente a una "serie B" o serie B , Puerta NOR:

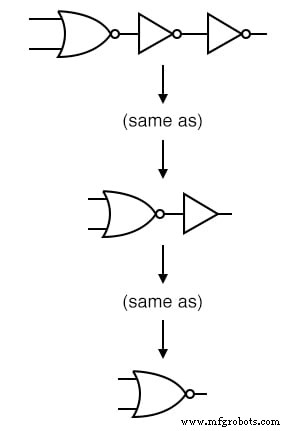

En esencia, la mejora del diseño de la serie B agrega dos inversores a la salida de un circuito NOR simple. Esto no tiene ningún propósito en lo que respecta a la lógica digital, ya que dos inversores en cascada simplemente se cancelan:

Sin embargo, agregar estas etapas de inversor al circuito tiene el propósito de aumentar la ganancia de voltaje general, haciendo que la salida sea más sensible a los cambios en el estado de entrada, trabajando para superar la lentitud inherente causada por la capacitancia de entrada de la puerta CMOS.

REVISAR:

- Las puertas lógicas CMOS están hechas de transistores IGFET (MOSFET) en lugar de transistores de unión bipolar.

- Las entradas de la puerta CMOS son sensibles a la electricidad estática. Pueden dañarse con altos voltajes y pueden asumir cualquier nivel lógico si se dejan flotando.

- Pullup y desplegable Las resistencias se utilizan para evitar que la entrada de una compuerta CMOS flote si es impulsada por una fuente de señal capaz solo de generar o absorber corriente.

- Las puertas CMOS disipan mucha menos energía que las puertas TTL equivalentes, pero su disipación de potencia aumenta con la frecuencia de la señal, mientras que la disipación de potencia de una puerta TTL es aproximadamente constante en una amplia gama de condiciones de funcionamiento.

- Las entradas de compuerta CMOS consumen mucha menos corriente que las entradas TTL, porque los MOSFET son dispositivos controlados por voltaje, no controlados por corriente.

- Las compuertas CMOS pueden operar en un rango mucho más amplio de voltajes de suministro de energía que TTL:típicamente de 3 a 15 voltios versus 4.75 a 5.25 voltios para TTL.

- Las puertas CMOS tienden a tener una frecuencia de operación máxima mucho más baja que las puertas TTL debido a las capacitancias de entrada causadas por las puertas MOSFET.

- Serie B Las puertas CMOS tienen salidas "con búfer" para aumentar la ganancia de voltaje de entrada a salida, lo que da como resultado una respuesta de salida más rápida a los cambios de señal de entrada. Esto ayuda a superar la lentitud inherente de las compuertas CMOS debido a la capacitancia de entrada del MOSFET y la constante de tiempo RC generada.

HOJAS DE TRABAJO RELACIONADAS:

-

Hoja de trabajo de transistores de efecto de campo de puerta aislada

-

Hoja de trabajo de puertas lógicas CMOS

Tecnología Industrial

- Cómo construir un circuito espejo actual

- Función de puerta básica

- Pestillo S-R de la puerta NOR

- Transistores, bipolares

- Transistores, efecto de campo de unión (JFET)

- Transistores, efecto de campo de puerta aislada (IGFET o MOSFET)

- Transistores, híbridos

- Circuitos integrados

- La puerta NOT

- Introducción a los transistores de efecto de campo de puerta aislada

- Modelado de nivel de puerta