Un modulador Delta-Sigma de tiempo continuo de rango dinámico de 80 dB de ancho de banda de 100 Mhz con una frecuencia de reloj de 2.4 Ghz

Resumen

El ancho de banda de un Δ Σ El modulador está limitado por la frecuencia de reloj debido al requisito de relación de sobremuestreo. Dado que los procesos CMOS a nanoescala se desarrollan rápidamente, es posible diseñar un ancho de banda amplio y un rango dinámico alto en tiempo continuo Δ Σ moduladores para aplicaciones de alta frecuencia. Este documento propone una Δ de tiempo continuo de 4 bits de tercer orden Σ modulador con una topología feedforward de bucle único. Este modulador está diseñado en un proceso CMOS de 40 nm y alcanza un rango dinámico de 80 dB y un ancho de banda de 100 MHz a una frecuencia de reloj de 2,4 GHz. El modulador consume 69,7 mW de una fuente de alimentación de 1,2 V.

Introducción

Impulsados por las crecientes demandas en las aplicaciones de comunicación inalámbrica, como los estándares celulares, los convertidores de analógico a digital (ADC) evolucionan rápidamente para admitir un mayor ancho de banda de señal (BW) y rango dinámico (DR). El requisito de BW en el estándar de comunicación Long-Term-Evolution Advanced (LTE-A) se ha elevado a 100 MHz. Los ADC de Nyquist, típicamente ADC de canalización [1, 2], se han utilizado en estaciones de base macro por su alto BW. Sin embargo, los búferes de entrada indispensables para activar los condensadores de entrada conmutados limitados por ruido térmico y el filtro anti-aliasing provocan un consumo de energía significativo y una complejidad de diseño. Además, el hecho de que los ADC de tubería se basan en una ganancia entre etapas precisa, que determina el amplificador de residuos de banda ancha de alta ganancia y la tecnología de calibración, conduce a la complejidad y la disipación de potencia. Δ Σ Los ADC son conocidos por su alto rendimiento y eficiencia energética que emplean tecnología de sobremuestreo y modelado de ruido. Sin embargo, el requisito de relaciones de sobremuestreo (OSR), que normalmente es superior a 16 [3–6], determina la frecuencia de muestreo más allá de GHz. Recientemente, Δ Σ Se han propuesto ADC que superan los 50 MHz de ancho de banda utilizando procesos CMOS a nanoescala, que permiten una frecuencia de reloj de varios GHz. Anteriormente, alta frecuencia Δ Σ Los ADC suelen adoptar realizaciones de tiempo continuo (CT) [3–9] en lugar de realizaciones de tiempo discreto (DT). Este último se implementa mediante un circuito de condensador conmutado, y su precisión se basa en la adaptación del condensador, lo que significa que se ofrece una operación robusta bajo la variación del proceso. Además, se proporciona una inmunidad superior a la fluctuación del reloj, ya que las constantes de tiempo de los condensadores e interruptores son suficientemente pequeñas. Sin embargo, como la operación de muestreo se ejecuta antes que el modulador, se necesita el filtro anti-aliasing. Por otro lado, debido al requisito de asentamiento para asegurar la estabilidad en las etapas, los amplificadores operacionales en los moduladores DT se implementan con un ancho de banda de ganancia unitaria (UGBW) más amplio que los moduladores CT. En resumen, los moduladores DT pueden proporcionar alta precisión pero una señal estrecha [10, 11] y se utilizan ampliamente para implementar aplicaciones de medición como sensores inteligentes e imágenes biomédicas. Por el contrario, ha habido un esfuerzo más generalizado para diseñar moduladores de TC para aplicaciones de alta frecuencia que los de TD con complejidad y consumo de energía comparables.

El objetivo de diseño exigente de un BW más alto en un proceso determinado determina un OSR más bajo debido a la frecuencia de reloj limitada por el proceso. Para lograr un DR suficiente, se requiere un modelado de ruido agresivo implementado por un orden de función de transferencia de ruido alto, que se realiza convencionalmente mediante cascada de filtro de bucle y generalmente igual o mayor que 3 en trabajos anteriores. Sin embargo, el aumento de los pedidos de filtros de bucle causa consumo de energía, inestabilidad y complejidad de diseño. La arquitectura de modelado de ruido de múltiples etapas (MASH) [6, 8], implementada por Δ locales de orden bajo en cascada Σ Se emplearon moduladores sin ruta de retroalimentación entre sí para aliviar los problemas de estabilidad, pero con sensibilidad al desajuste. Además, un modulador con un cuantificador de múltiples bits obtiene un DR condicionalmente alto con una cantidad de comparador que aumenta exponencialmente.

Este artículo describe un modulador de CT en CMOS de 40 nm que alcanza 80 DR sobre 100 MHz BW con un consumo de 69,7 mW utilizando un proceso CMOS de 40 nm. Este artículo está organizado de la siguiente forma:La sección "Método" describe la topología del modulador y la implementación del circuito. La sección "Resultados y discusión" muestra resultados simulados, y la sección "Conclusión" proporciona un resumen de este trabajo.

Método

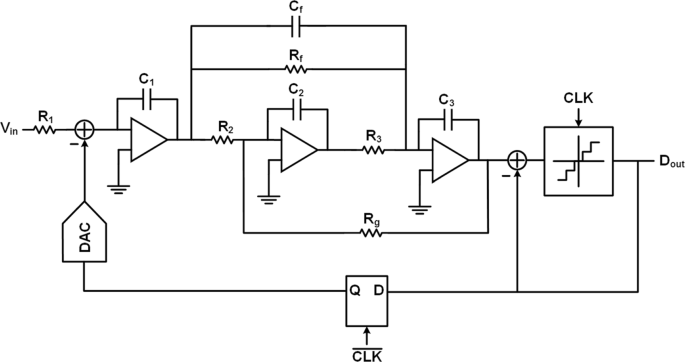

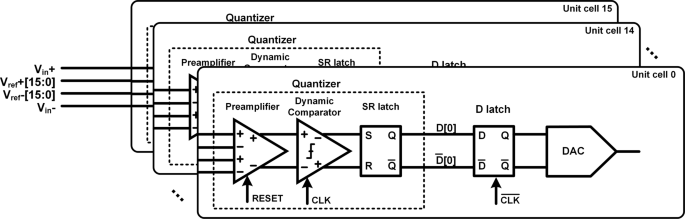

La Figura 1 ilustra el esquema general del CT de tercer orden propuesto Δ Σ modulador con la estructura de un solo extremo para simplificar. El modelado de ruido de tercer orden consigue un gran compromiso entre el DR y la estabilidad del bucle. El modulador propuesto tiene una frecuencia de muestreo de 2,4 GHz con un OSR de 12. El OSR relativamente alto en Δ Σ moduladores excedidos de 100 MHz BW asegura un alto DR. El modulador contiene tres integradores RC, un cuantificador de 4 bits y un DAC de control de corriente de 4 bits. Los integradores se implementan mediante innovadores amplificadores feedforward de disipación de baja potencia para una alta eficiencia energética. El DAC de retroalimentación tiene un retardo adicional de duración de medio período de muestreo para relajar el requisito de metaestabilidad del cuantificador. Una ruta de retroalimentación rápida implementada por un sumador pasivo e impulsada directamente por el cuantificador realiza la compensación de retardo de bucle excesivo (ELD). Se emplea una topología de alimentación directa para la eficiencia energética a expensas de la función de transferencia de señal fuera de banda.

Esquema general del CT de 4 bits de tercer orden de bucle único propuesto Δ Σ modulador con topología feedforward

Diseño del amplificador

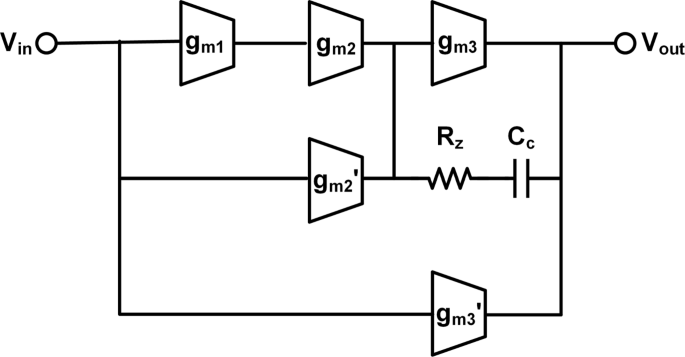

Se requiere una alta ganancia del amplificador en Δ Σ moduladores para asegurar la función de transformación de ruido deseada. Sin embargo, las tecnologías a nanoescala utilizadas para lograr una frecuencia de reloj de varios GHz sufren una baja ganancia intrínseca. Por lo tanto, se adopta un amplificador de tres etapas para implementar suficiente ganancia de CC, como se muestra en la Fig. 2. La topología de avance y la compensación de Miller se combinan para mejorar el margen de fase sin reducción de ancho de banda de ganancia unitaria. Los amplificadores feedforward han sido una solución popular para lograr una alta ganancia con UGBW y margen de fase (PM) adecuados. Se supone que el cero del semiplano izquierdo causado por la trayectoria de alimentación hacia adelante cancela efectivamente el cambio de fase negativo de los polos. Requiere una alta transconductancia de los amplificadores en la ruta de alimentación y consume una potencia significativa. El esquema ventajoso de reutilizar la corriente de polarización ahorra energía mientras que limita g m valores. g insuficiente m normalmente provoca el cero más allá del UGBW y no puede proporcionar un margen de fase adecuado. Se proporciona un cero optimizado ubicado debajo del UGBW general agregando un condensador de compensación Miller y una resistencia de anulación.

Topología del amplificador feedforward de tres etapas propuesto con compensación Miller

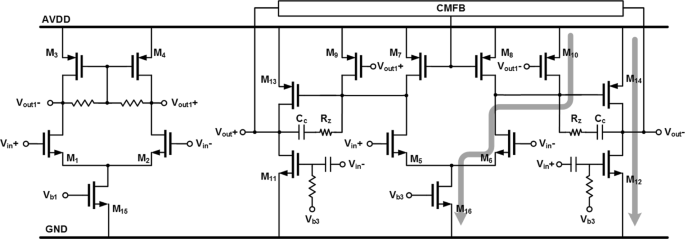

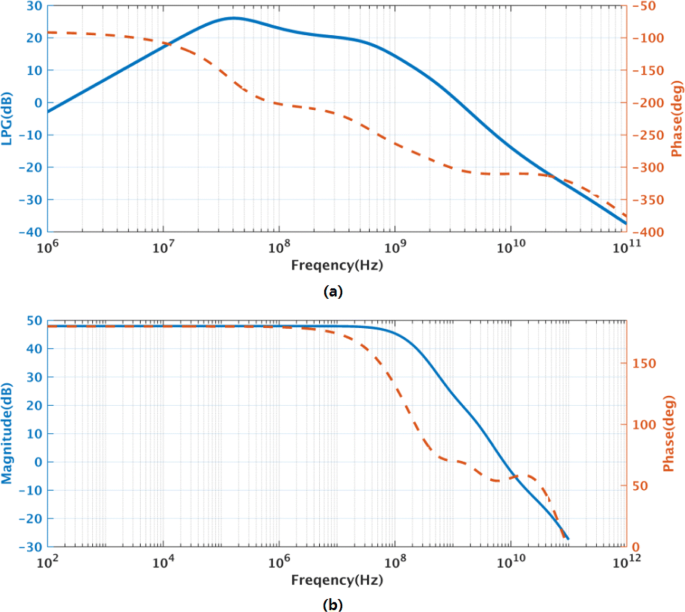

La Figura 3 muestra el esquema a nivel de transistor del amplificador utilizado en el primer integrador. Transistores M 1−4 forman la etapa de entrada del amplificador, mientras que los transistores M 9,10 y M 13,14 forman la segunda y tercera etapa, respectivamente. Transistores M 5−8 y M 11,12 Cree dos rutas de avance de alta velocidad entre la entrada y la salida mientras comparte las corrientes de polarización con los amplificadores de segunda y tercera etapa. El modo común de salida (CM) de la primera etapa se fija localmente. El CM de salida de la segunda y la tercera etapa se fija mediante una ruta de retroalimentación de la segunda etapa a través de un amplificador CMFB, M 7,8 y M 13,14 . La figura 4a muestra la respuesta de bucle abierto posterior al diseño simulado del amplificador del primer integrador con toda la carga, mientras que la figura 4b muestra la respuesta de bucle cerrado. El primer integrador alcanza 3,6 GHz de UGBW y 57,8 ∘ de PM con todo el efecto de carga mientras consume 10,5 mW de un suministro de 1,2 V. El segundo y tercer integradores adoptan la misma topología pero con corrientes de polarización escaladas, logrando UGBW de 4.7 y 3.3 GHz y PM de 58.0 y 57.8 ∘ mientras consume 4,3 y 17,3 mW, respectivamente.

Esquema de nivel de transistor del amplificador

El diseño posterior simuló los resultados del amplificador en el primer integrador. un Respuesta de CA de lazo abierto; b Respuesta de CA de circuito cerrado

Cuantizador y DAC

Como se muestra en el esquema del cuantificador y DAC en la Fig. 5, cada uno consta de 16 celdas unitarias. El cuantificador se realiza como un ADC flash de 4 bits con codificador de 16 niveles generado a partir de una escalera resistiva de 17 tomas. El cuantificador, cuya duración de operación es exigida por ELD a menos de la mitad de un período de muestreo para garantizar la estabilidad del bucle, es un bloque clave como limitación del BW máximo.

El esquema simplificado de los cuantificadores y los DAC

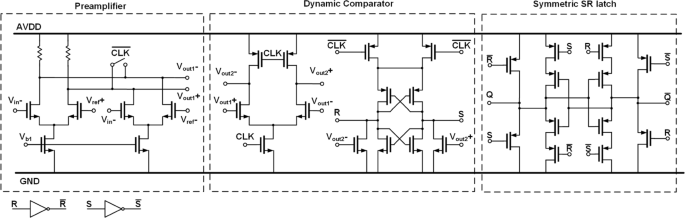

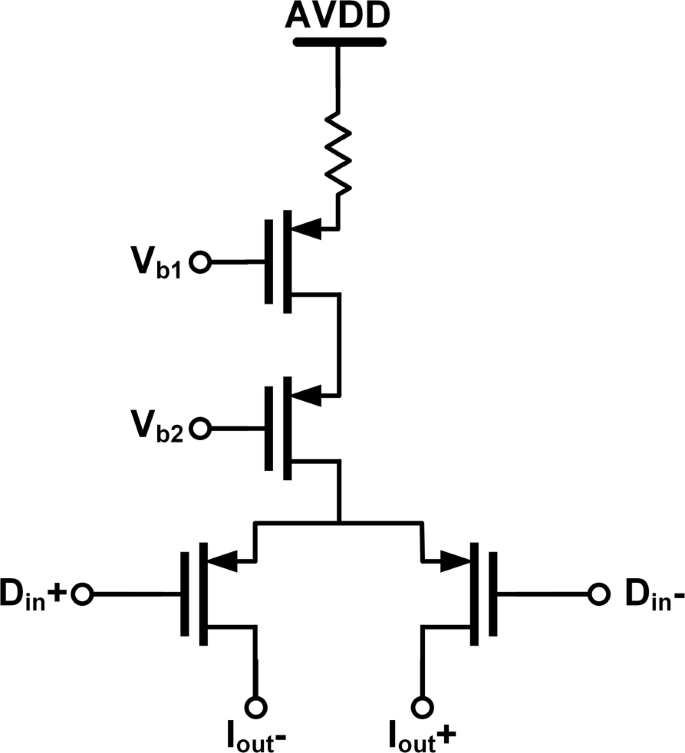

Para implementar ADC flash de alta velocidad, se emplea una arquitectura de comparador de tres etapas que consta de una etapa de preamplificador, una etapa de comparador dinámico y un pestillo simétrico de activación y desactivación (SR) [12], ilustrado en la figura 6. El preamplificador para la reducción de compensación referida a la entrada son dos pares diferenciales de carga resistiva con un interruptor de reinicio que se conecta a través de las salidas para permitir una recuperación rápida. A diferencia de los comparadores dinámicos convencionales, el par diferencial y los inversores de acoplamiento cruzado se dividen en dos partes para minimizar la cantidad de transistor en cada ruta de corriente para suministros de bajo voltaje. Cuando el reloj cambia al nivel alto, los comparadores dinámicos comienzan a tomar la decisión de comparación dependiente de la entrada. Luego, las dos salidas de cada comparador dinámico se restablecen a 0 a medida que el retorno del reloj pasa de alto a bajo, lo que activa la regeneración y el enclavamiento del pestillo SR simétrico. Dado que solo un transistor en cada rama está activo, la estructura de enclavamiento SR simétrica conduce a una fuerte capacidad de conducción de carga. Permite un tamaño de transistor pequeño con una velocidad de apagado significativa y un bajo consumo de energía. Además, da como resultado retrasos iguales de ambas señales de salida. Los pestillos D antes de las unidades DAC son sensibles al nivel bajo con respecto al nivel de la señal del reloj, lo que garantiza la mitad de la duración del ELD. El circuito de nivel de transistor de la unidad DAC de dirección actual se muestra en la Fig. 7.

Circuito a nivel de transistor de un elemento unitario del cuantificador propuesto

El elemento de unidad DAC de dirección actual de PMOS

Resultados y discusión

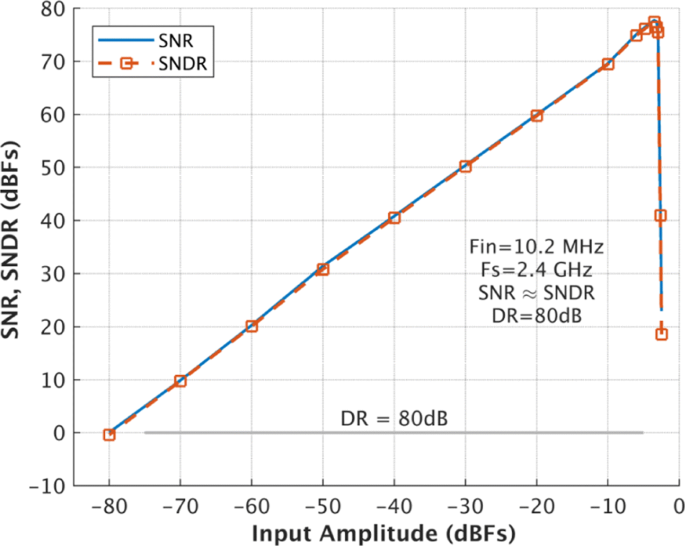

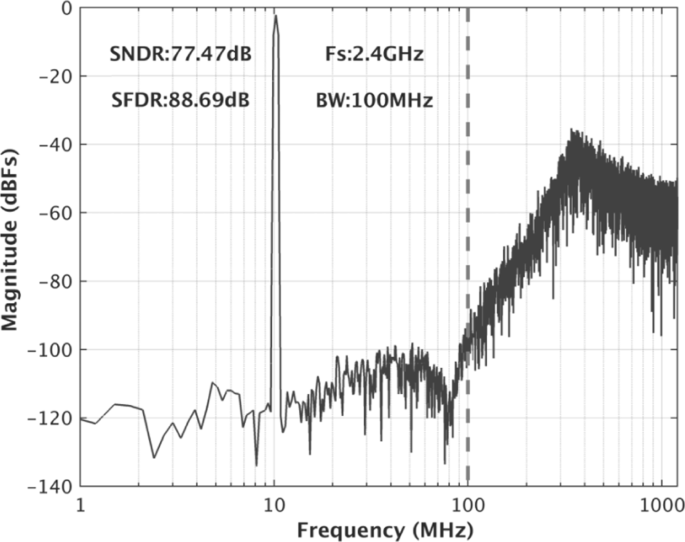

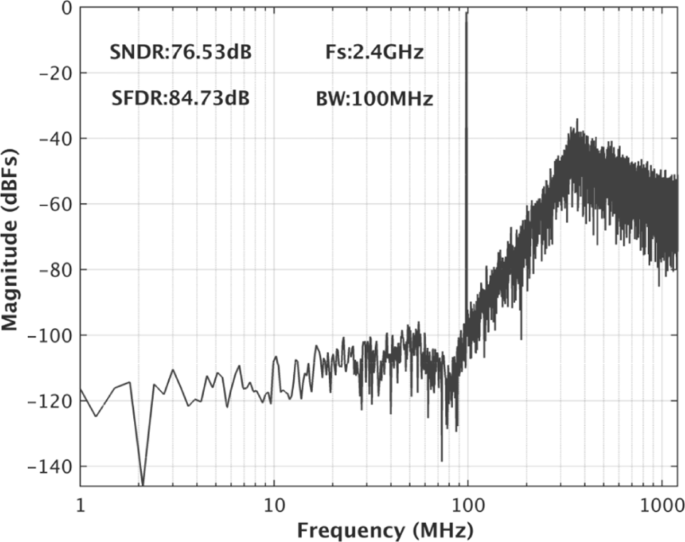

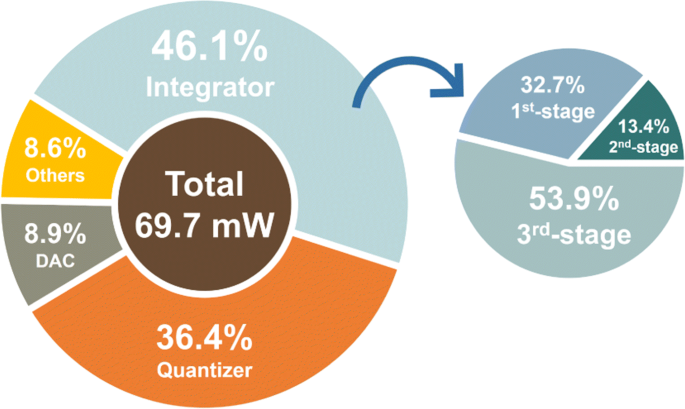

El prototipo Δ Σ El modulador está integrado en un proceso CMOS de 40 nm. Como los resultados post-simulados de la SNR y SDNR frente a la amplitud de entrada a 10,2 MHz que se muestran en la Fig. 8, se logra una DR de 80 dB. Las Figuras 9 y 10 muestran los espectros simulados con una entrada de tono único de - 3,52 dBF a 10,2 MHz y 97 MHz, respectivamente, ya que 0 dBF corresponde a la escala completa del modulador de 2,4 Vpp. La SNDR es 77,47 dB y 76,53 dB, respectivamente. Como el consumo de avería que se muestra en la Fig. 11, el modulador cuesta 69,7 mW de consumo de energía. El integrador, el cuantificador y el DAC consumen respectivamente 32,1 mW, 25,4 mW y 6,2 mW. Las otras corrientes consumen 6,0 mW de potencia, incluidos los búferes de reloj, las polarizaciones de corriente y las referencias de voltaje. El modulador alcanza un Schreier FOM de 171,6 dB basado en DR. La Tabla 1 compara este trabajo con varios trabajos publicados anteriormente. El modulador propuesto logra un ancho de banda amplio con la mayor FOM.

SNR y SNDR post-simulados frente a la amplitud de la señal de entrada con una entrada de 10,2 MHz

Los espectros post-simulados con una entrada de tono único a 10,2 MHz

Los espectros post-simulados con una entrada de tono único a 97 MHz

El desglose del consumo de energía post-simulado

Conclusión

En este trabajo, propusimos un CT de 4 bits de tercer orden Δ Σ modulador con una topología feedforward de bucle único. Este modulador está diseñado en un proceso CMOS de 40 nm y alcanza una DR de 80 dB en un BW de 100 MHz a una frecuencia de reloj de 2,4 GHz. La construcción del amplificador de disipación de baja potencia ofrece una alta eficiencia energética, y el modulador consume 69,7 mw de una fuente de alimentación de 1,2 V y alcanza una FOM Schreier de 171,6 dB.

Disponibilidad de datos y materiales

Todos los datos generados o analizados durante este estudio se incluyen en este artículo publicado.

Abreviaturas

- ADC:

-

Convertidores de analógico a digital

- BW:

-

Ancho de banda

- CT:

-

Tiempo continuo

- DR:

-

Rango dinámico

- DT:

-

Tiempo discreto

- ELD:

-

Retardo de bucle excesivo

- LTE-A:

-

Avanzado de evolución a largo plazo

- OSR:

-

Ratios de sobremuestreo

- PM:

-

Margen de fase

- UGBW:

-

Ancho de banda de ganancia unitaria

Nanomateriales

- El reloj IV9 Numitron más simple de bricolaje con Arduino

- Impresión 3D de alta velocidad con AION500MK3

- Control completo de polarización de terahercios con ancho de banda ampliado a través de metauperficies dieléctricas

- Fabricación de pozos a nanoescala con alto rendimiento en película delgada de polímero utilizando litografía de arado dinámico basada en puntas AFM

- RGO y redes de grafeno tridimensionales co-modificadas TIM con alto rendimiento

- Aerogel de grafeno / polianilina con superelasticidad y alta capacitancia como electrodo supercondensador altamente tolerante a la compresión

- Convertidor de polarización con birrefringencia controlable basado en metauperficie híbrida de grafeno totalmente dieléctrico

- Célula solar híbrida de silicio nanoestructurado orgánico de alto rendimiento con estructura de superficie modificada

- La respuesta fotocorriente extremadamente mejorada en nanohojas de aislante topológico con alta conductividad

- Dispositivo multifuncional con funciones conmutables de absorción y conversión de polarización en el rango de terahercios

- Una referencia de voltaje sin resistencia de baja potencia a nanoescala con PSRR alto