Ge pMOSFET de alta movilidad con dieléctrico de ZrO2:impactos del recocido posterior

Resumen

Este artículo investiga los impactos del recocido posterior al metal (PMA) y el recocido posterior a la deposición (PDA) en el rendimiento eléctrico de los transistores de efecto de campo semiconductores de óxido metálico de tipo p (pMOSFET) con ZrO 2 dieléctrico. Para los transistores sin PDA, corriente en estado ( I ACTIVADO ), la oscilación del subumbral (SS) y las características de espesor equivalente de capacitancia (CET) se mejoran con un aumento de la temperatura de PMA de 350 a 500 ° C. Cristalización de ZrO 2 dieléctrico a la temperatura más alta de PMA contribuye al aumento de la permitividad de ZrO 2 y la disminución de la densidad de estados de la interfaz ( D eso ), lo que da como resultado un CET reducido y una alta movilidad efectiva del agujero ( μ ef ). Está demostrado que los pMOSFET de Ge con un tratamiento con CAP a 400 ° C tienen un CET más bajo y un SS más pronunciado pero un μ más bajo ef en comparación con dispositivos sin PDA.

Antecedentes

El germanio (Ge) ha sido considerado como uno de los materiales de canal p atractivos para CMOS avanzados porque ofrece una movilidad de agujero mucho mayor que el Si [1, 2, 3]. Un dieléctrico de puerta de alta calidad y una pasivación efectiva de la superficie de Ge son las claves para lograr la movilidad superior efectiva del portador ( μ ef ) y alta corriente de excitación en el transistor Ge [4, 5, 6, 7]. Varios materiales con alto contenido de kappa como HfO 2 [8], ZrO 2 [7, 9], La 2 O 3 [10] e Y 2 O 3 [11] se han estudiado como los dieléctricos de puerta alternativos para los transistores de efecto de campo semiconductores de óxido metálico de tipo p (pMOSFET) para lograr una escalabilidad de espesor equivalente de capacitancia (CET) hacia sub-1 nm. Entre estos, ZrO 2 el dieléctrico ha atraído la mayor atención debido al valor κ mucho más alto [12, 13] y la mejor calidad interfacial [14] en comparación con los basados en Hf. Se ha informado ampliamente que la cristalización de ZrO 2 puede mejorar aún más el rendimiento eléctrico de Ge pMOSFET, por ejemplo, reduciendo el CET y aumentando μ ef [15, 16]. Sin embargo, hay una falta de estudio sobre los impactos de los pasos del proceso para ZrO 2 cristalización en el rendimiento del dispositivo de los transistores Ge.

En este artículo, investigamos los impactos del recocido posterior al metal (PMA) y el recocido posterior a la deposición (PDA) en el rendimiento eléctrico de los pMOSFET de Ge con ZrO 2 dieléctrico. μ significativamente mejorado ef y se puede lograr una CET reducida en dispositivos con una temperatura de PMA más alta.

Métodos

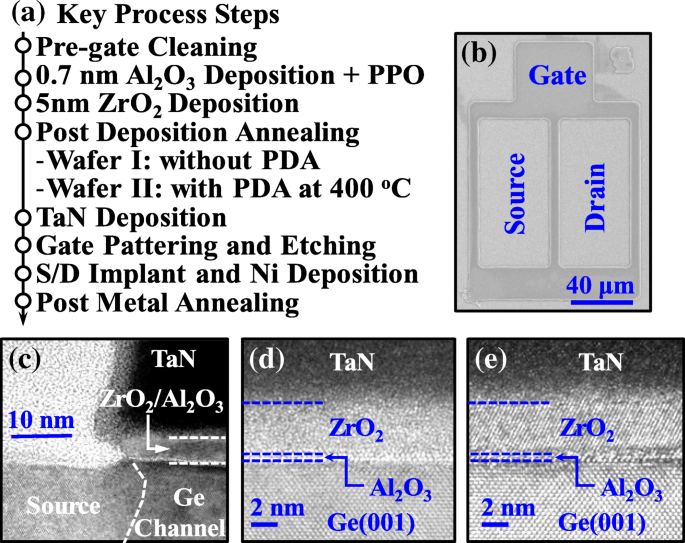

Pasos clave del proceso para fabricar Ge pMOSFET con ZrO 2 dieléctrico se muestran en la Fig. 1a. Los pMOSFET de Ge se fabricaron en una oblea de Ge (001) de tipo n con una resistividad de 0.088-0.14 Ω ∙ cm. Después de varios ciclos de limpieza química en la solución diluida de HF (1:50) y enjuague con agua desionizada. La oblea de Ge se cargó en una cámara de deposición de capa atómica (ALD). La superficie de Ge fue pasivada por una posoxidación de ozono (OPO), es decir, un Al 2 ultrafino O 3 La capa se depositó a 300 ° C, y luego, la OPO in situ se llevó a cabo a 300 ° C durante 15 min. Después de eso, un ZrO 2 de 5 nm de espesor se depositó a 250 ° C en la misma cámara ALD usando TDMAZr y H 2 O como precursores de Zr y O, respectivamente. Durante la deposición, Zr [N (CH 3 ) 2 ] 4 La fuente se calentó a 85 ° C. El proceso PDA se llevó a cabo en una muestra a 400 ° C durante 60 s utilizando el recocido térmico rápido. Las muestras con y sin PDA se denominaron oblea II e I, respectivamente. Luego, se depositó un electrodo de puerta de TaN de 100 nm de espesor mediante pulverización catódica reactiva. Después del modelado y grabado de la puerta, las regiones de fuente / drenaje (S / D) fueron formadas por BF 2 + implantación a una energía de 30 keV y una dosis de 1 × 10 15 cm −2 . Los contactos S / D de níquel de quince nanómetros se formaron mediante un proceso de despegue. Finalmente, se llevó a cabo la PMA a 350, 400, 450 y 500 ° C durante 30 s para la activación del dopante y la metalización S / D.

un Pasos clave del proceso para fabricar Ge pMOSFET con ZrO 2 dieléctrico. b Imagen SEM del transistor fabricado. c Imagen XTEM de Ge pMOSFET que muestra la puerta y las regiones S / D. d , e Imágenes HRTEM de pilas de compuertas de Ge pMOSFET en la oblea I recocidas a 400 ° C y 500 ° C, respectivamente

La Figura 1b muestra la imagen del microscopio electrónico de barrido (SEM) de un Ge pMOSFET fabricado. La Figura 1c muestra la imagen de microscopio electrónico de transmisión de sección transversal (XTEM) de Ge pMOSFET, que muestra la región de fuente / drenaje, la puerta de metal y ZrO 2 dieléctrico. Las figuras 1d y e muestran las imágenes TEM de alta resolución (HRTEM) de las pilas de puertas de Ge pMOSFET con un PMA a 400 y 500 ° C, respectivamente, en la oblea I. Se observa que el ZrO 2 El dieléctrico se cristalizó completamente y se sometió a PMA a 500 ° C. El espesor de Al 2 O 3 La capa interfacial es de aproximadamente 0,7 nm.

Resultados y discusión

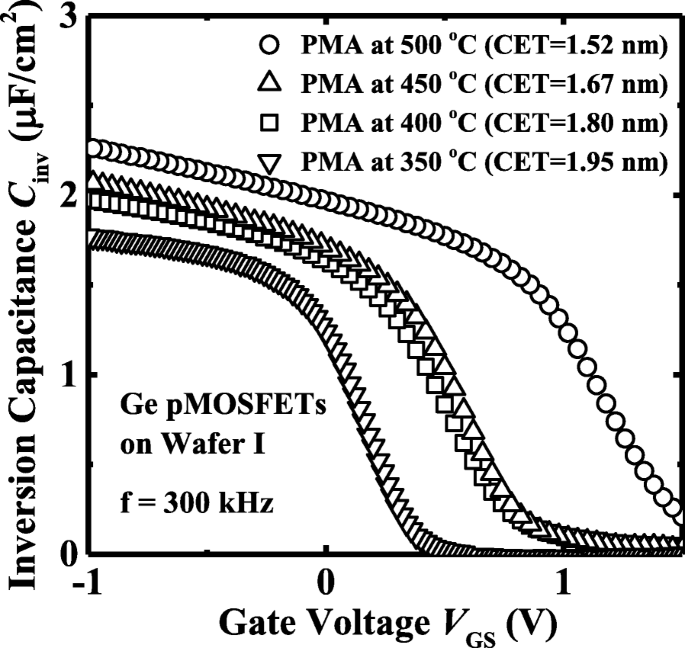

Capacitancia de inversión C inv frente a V GS Las curvas medidas a una frecuencia de 300 kHz para los dispositivos en la oblea I se muestran en la Fig. 2. Los valores CET se extraen para ser ∼ 1.95, 1.80, 1.67 y 1.52 nm para los dispositivos con PMA a 350, 400, 450, y 500 ° C, respectivamente. El CET más pequeño se logra a una temperatura de PMA más alta debido a la cristalización de ZrO 2 . En general, los valores de κ para ZrO 2 amorfo y cristalino son alrededor de 20-23 y 28-30, respectivamente. Un ZrO 2 cristalino de 5 nm de espesor aporta un EOT de ~ 0,7 nm. El cambio de C-V Las curvas con varias temperaturas de PMA se deben al hecho de que la cristalización reduce la densidad de las trampas a granel en ZrO 2 dieléctrico.

Inversión C inv - V GS curvas para los Ge pMOSFET en la oblea I con un PMA a 350 ° C, 400 ° C, 450 ° C y 500 ° C

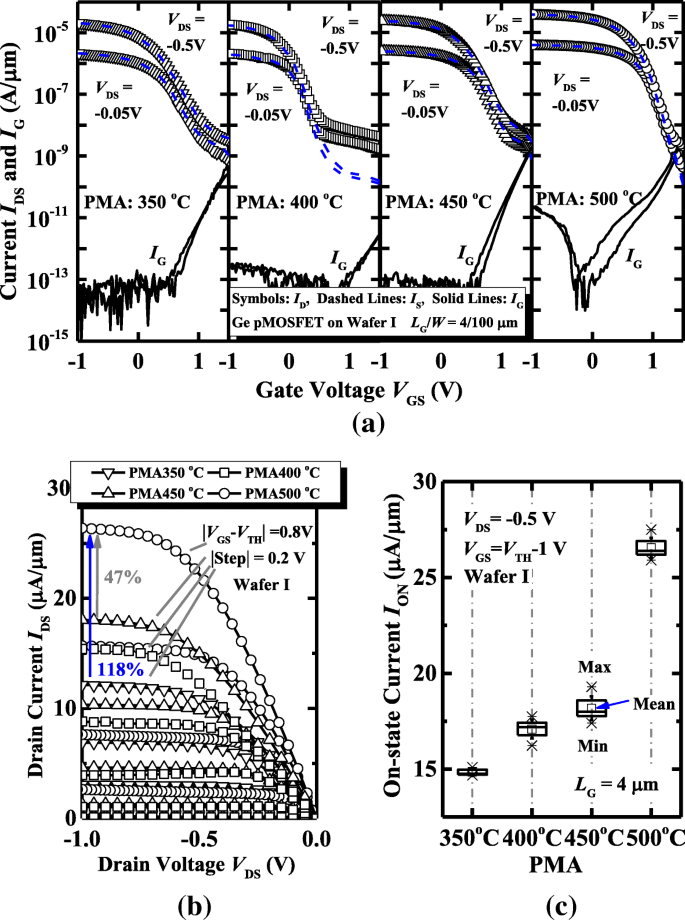

La Figura 3a muestra las características de transferencia medidas y las corrientes de fuga de la compuerta I G de Ge pMOSFETs en la oblea I con las diferentes temperaturas de PMA. Todos los dispositivos tienen una longitud de puerta L G de 4 μm y un ancho de puerta W de 100 μm. Los pMOSFET de Ge exhiben un I mucho más bajo G en comparación con yo DS para todas las temperaturas PMA. Un yo ACTIVADO / Yo APAGADO proporción superior a 10 4 se logra para el dispositivo con un PMA a 500 ° C. El yo DS - V DS curvas de los dispositivos medidos en las diferentes puertas de sobremarcha | V GS - V TH | se muestran en la Fig. 3b. Se observa que el voltaje umbral V TH se define como la V GS en I DS de 10 −7 A / μm. El transistor Ge con un PMA a 500 ° C obtiene una mejora de la corriente de excitación de ~ 47% y 118% en comparación con los dispositivos recocidos a 450 ° C y 350 ° C, respectivamente, a V DS de - 1.0 V y una | V GS - V TH | de 0,8 V. La figura 3c muestra el gráfico estadístico de I ACTIVADO en una V DS de - 0,5 V y una V GS - V TH de - 1 V para Ge pMOSFET con las distintas temperaturas PMA. Todos los transistores de este gráfico tienen una L G de 4 μm y un W de 100 μm. Los dispositivos con PMA a 500 ° C presentan una I mejorada ACTIVADO en comparación con aquellos con temperaturas de PMA más bajas, lo que se atribuye a la disminución de la resistencia S / D, la reducción del CET y la mayor μ ef , que se discutirá más adelante.

un Medido I D , yo S y yo G vs. V GS curvas de Ge pMOSFET en la oblea I con el PMA a 350, 400, 450 y 500 ° C. b yo DS - V DS curvas medidas en los diferentes V GS - V TH para los dispositivos. c El dispositivo recocido a 500 ° C tiene una corriente en estado más alta I ACTIVADO en comparación con los transistores con PMA a temperaturas más bajas

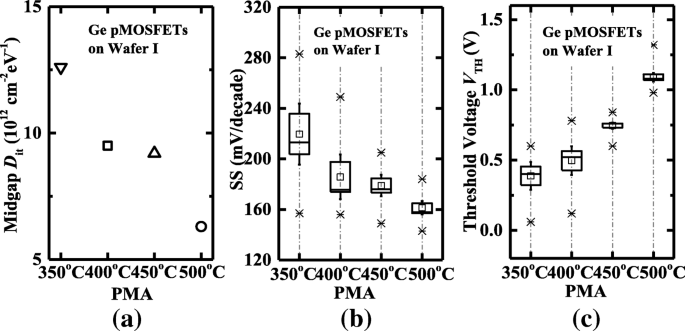

La Figura 4 muestra los gráficos estadísticos de midgap D eso , SS y V TH características de los dispositivos con las diferentes temperaturas PMA. Como se muestra en la Fig. 4a, basado en el método de conductancia máxima [17], el intervalo medio D eso los valores se extraen para que sean 1,3 × 10 13 , 9,5 × 10 12 , 9,2 × 10 12 y 6,3 × 10 12 cm −2 eV −1 para los dispositivos con PMA a 350, 400, 450 y 500 ° C, respectivamente. La Figura 4b presenta que los pMOSFET de Ge recocidos a 500 ° C tienen las características SS mejoradas que los transistores recocidos a temperaturas más bajas, debido al intervalo medio más pequeño D eso y CET. Los valores de D eso y SS de los pMOSFET de Ge con PMA son aún más altos que los de los transistores de Ge mejor informados. Posiblemente podría reducirse optimizando el módulo de pasivación OPO, por ejemplo, Al 2 O 3 espesor y temperatura y duración de la oxidación del ozono. V TH cambia a la V positiva GS con el aumento de la temperatura de PMA, que se origina a partir del CET reducido y D eso . Se concluye que el mejor rendimiento eléctrico se logra para Ge pMOSFET con un PMA a 500 ° C.

Comparación de a medio espacio D eso , b SS y c V TH para Ge pMOSFET en oblea I con el PMA a 350, 400, 450 y 500 ° C

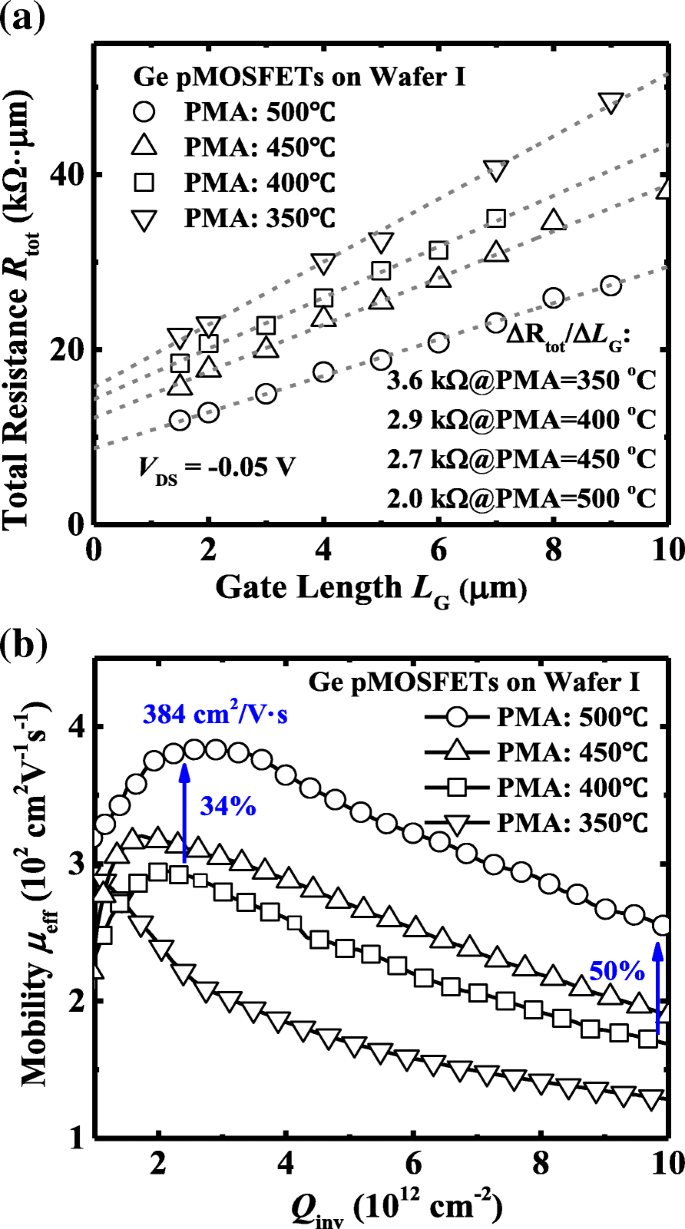

μ ef , como un factor crucial que afecta la corriente de excitación del dispositivo y la transconductancia en los pMOSFET de Ge, se midió utilizando Δ R tot / Δ L G método [18]. Se midió una gran cantidad de dispositivos con L G que van desde 1,5 a 9 μm. La figura 5a ilustra la resistencia total R tot extraído en un | V GS - V TH | de - 1 V y una V DS de - 0,05 V en función de L G . La R SD es el valor en el que la línea ajustada se cruza en la y -eje. La R SD los valores se estimaron aproximadamente en 7,85, 7,15, 6,10 y 4,35 kΩ · μm para dispositivos con PMA a 350, 400, 450 y 500 ° C, respectivamente. Esto es indicativo de la mejor activación del dopante de S / D a una temperatura de PMA más alta. μ ef se puede extraer con μ ef =1 / [ WQ inv (Δ R tot / Δ L G )], donde Q inv es la densidad de carga de inversión en el canal de Ge y Δ R tot / Δ L G es la pendiente de la R tot frente a L G como se muestra en la Fig. 5a. El Δ R más pequeño tot / Δ L G para dispositivos con PMA a 500 ° C indica una mejora en μ ef en comparación con transistores con PMA a 450 ° C. La figura 5b muestra μ ef en función de Q inv curvas, extraídas usando la división C - V método. La movilidad máxima del agujero es de 384 cm 2 / V · s para dispositivos con un PMA a 500 ° C, que es un 31% más alto que el de los dispositivos con un PMA a 400 ° C. Con un Q alto inv de 1 × 10 13 cm −2 Los pMOSFET de Ge que se sometieron a un PMA a 500 ° C logran una mejora de la movilidad en comparación con los dispositivos recocidos a 400 ° C. Transistores Ge con ZrO 2 cristalino tienen la menor densidad de carga de la trampa a granel, lo que resulta en una menor dispersión remota de los orificios de Coulomb, en comparación con los dispositivos con ZrO 2 amorfo . Debido a la interfaz suave entre ZrO 2 cristalino y los dispositivos Ge, Ge recocidos a 500 ° C tienen una dispersión de rugosidad superficial más baja y muestran un cambio de movilidad máxima a la Q más alta inv .

un R tot en función de L G en una V GS - V TH de - 1 V y una V DS de - 0.05 V para dispositivos en la oblea I con varias temperaturas PMA. b μ ef vs. Q inv extraído por la división C - V método. La mayor movilidad se obtiene en dispositivos con PMA a 500 ° C

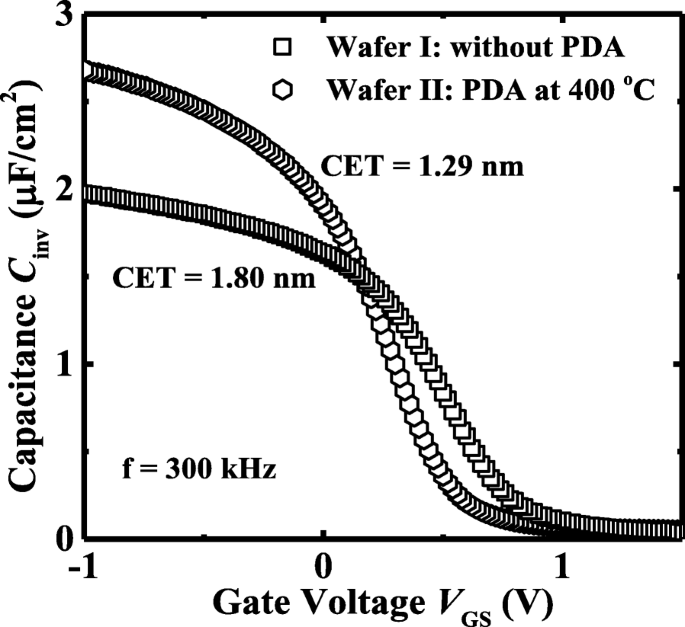

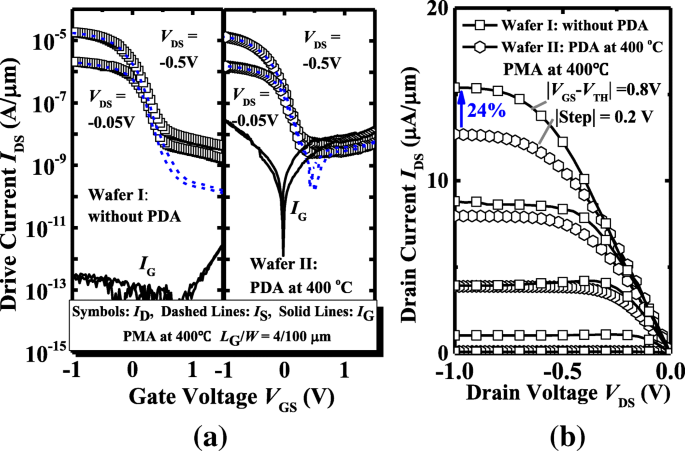

A continuación, discutimos los impactos de PDA en las características eléctricas de Ge pMOSFET. La Figura 6 muestra la C medida inv frente a V GS de los Ge pMOSFET en la oblea I y la oblea II con un PMA a 400 ° C. El dispositivo que se sometió a una PDA a 400 ° C tiene un valor CET mucho más bajo de 1,29 nm en comparación con el dispositivo sin PDA, 1,80 nm. La figura 7a muestra el I D , yo S y yo G - V GS curvas características de Ge pMOSFET en la oblea I y la oblea II, y los dispositivos que se sometieron a una PMA a 400 ° C. Se obtiene una corriente de fuga de puerta mayor para el dispositivo con PDA en comparación con el transistor sin PDA, lo que se debe al CET más bajo. El I correspondiente DS - V DS curvas de los dispositivos medidos en diferentes compuertas overdrive V GS - V TH se muestran en la Fig. 7b. El transistor Ge sin PDA muestra una mejora de ~ 24% en la corriente de excitación con respecto al que tiene PDA a 400 ° C con la misma sobremarcha de - 0,8 V en la región de saturación.

C inv -V GS gráficos para los dispositivos en la oblea I y II con un PMA a 400 ° C

un yo D , yo S y yo G vs. V GS curvas de Ge pMOSFET en la oblea I y II con PMA a 400 ° C. b yo DS - V DS curvas medidas a diferentes V GS - V TH para los dispositivos

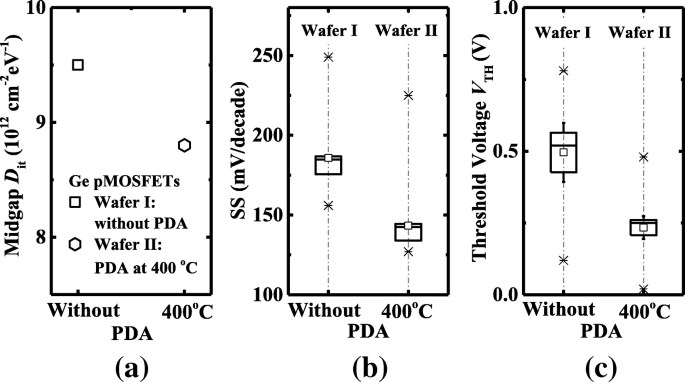

La Figura 8 traza los resultados estadísticos de midgap D eso , SS y V TH de los Ge pMOSFET con y sin PDA. La figura 8a muestra que la D más pequeña eso se consigue en Ge pMOSFET con PDA a 400 ° C en comparación con dispositivos sin PDA. En la Fig. 8b, el valor más bajo de la oscilación media del subumbral de 142 mV / década se logra para dispositivos con PDA a 400 ° C, correspondiente al CET más bajo y el D más bajo. eso . Indica que los dispositivos con PDA a 400 ° C tienen un ZrO 2 superior / Ge interfaz. La Figura 8c muestra que los dispositivos con y sin PDA tienen una V diferente TH ; puede atribuirse a la densidad de trampas en la mitad inferior de la banda prohibida dominante en la V TH .

Comparación de a medio espacio D eso , b SS y c V TH para Ge pMOSFET en obleas I y II con PMA a 400 ° C

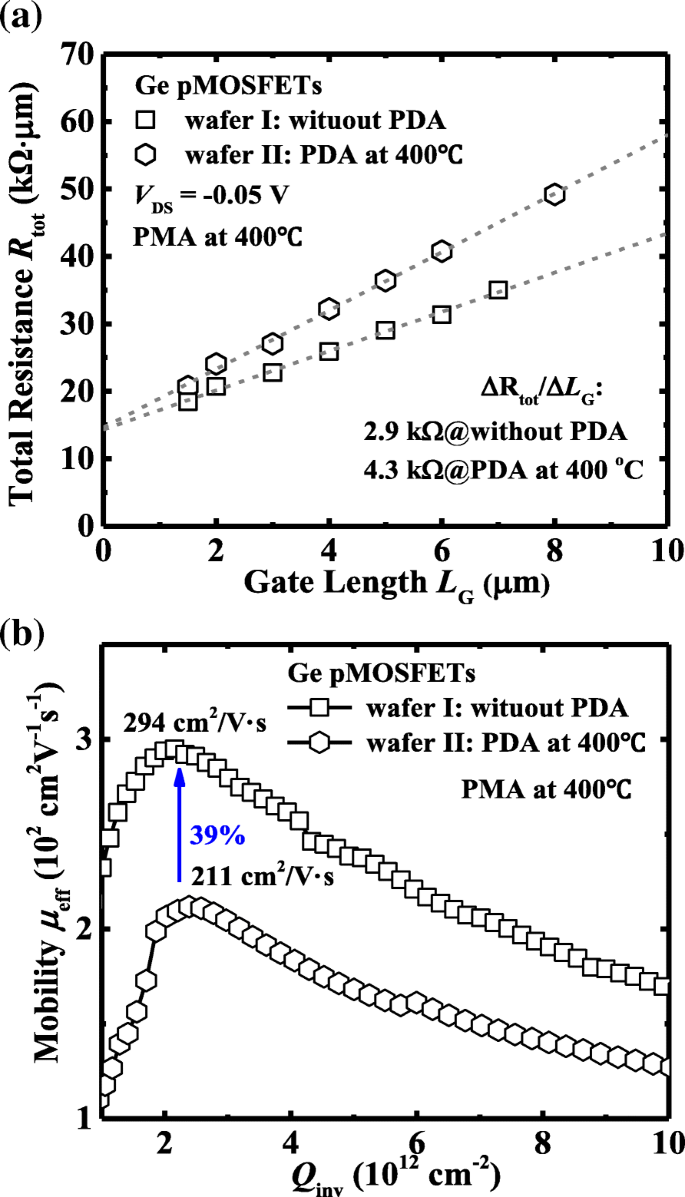

La figura 9a muestra la R tot frente a L G curvas en una sobremarcha de puerta de - 1 V y V DS de - 0,05 V para dispositivos con PMA a 400 ° C. La R SD los valores se estiman aproximadamente en 7,15 y 7,30 kΩ · μm para dispositivos sin y con PDA a 400 ° C, respectivamente. Como se muestra en la Fig. 9b, un pico notablemente más alto μ ef se logra para Ge pMOSFET sin PDA, correspondiente al Δ R más pequeño tot / Δ L G en la Fig. 9a, en comparación con dispositivos con PDA. Los dispositivos con PDA a 400 ° C presentan un pico μ ef de 211 cm 2 / V · s; la movilidad del pozo inferior podría atribuirse principalmente a la fuerte dispersión remota de Coulomb contribuida por la carga fija en ZrO 2 dieléctrico.

un R tot frente a L G curvas para dispositivos en oblea I y oblea II con PMA a 400 ° C. b Movilidad del agujero μ ef frente a Q inv para dispositivos con y sin PDA

Conclusiones

En resumen, los impactos de PMA y PDA en Ge pMOSFET con ZrO 2 dieléctrico fueron ampliamente investigados. Cristalización de ZrO 2 El dieléctrico de la compuerta proporciona una movilidad de pozo significativamente mejorada y una CET reducida en comparación con los dispositivos a la temperatura de PMA más baja. Una movilidad máxima del agujero de 384 cm 2 / V · sy una corriente de excitación mejorada se han logrado en dispositivos con PMA a 500 ° C. Los dispositivos con PDA a 400 ° C exhibieron el CET más bajo y el D más pequeño eso pero la movilidad deficiente del orificio y la corriente de fuga más grande en comparación con los transistores sin PDA.

Disponibilidad de datos y materiales

Los conjuntos de datos que respaldan las conclusiones de este artículo se incluyen en el artículo.

Abreviaturas

- ALD:

-

Deposición de la capa atómica

- BF 2 + :

-

Ión de fluoruro de boro

- CET:

-

Espesor efectivo capacitivo

- Ge:

-

Germanio

- HF:

-

Ácido fluorhídrico

- HRTEM:

-

Microscopio electrónico de transmisión de alta resolución

- IL:

-

Capa interfacial

- MOSFET:

-

Transistores de efecto de campo semiconductores de óxido metálico

- Ni:

-

Níquel

- PDA:

-

Recocido posterior a la deposición

- PMA:

-

Post recocido de metales

- SS:

-

Oscilación del subumbral

- TaN:

-

Nitruro de tantalio

- TDMAZr:

-

Tetrakis (dimetilamido) hafnio

- ZrO 2 :

-

Dióxido de circonio

- μ ef :

-

Movilidad eficaz del transportista

Nanomateriales

- KUHMUTE rediseña la movilidad con la impresión 3D SLS

- Impresión 3D de alta velocidad con AFPM

- Impresión 3D de alta velocidad con AION500MK3

- Control completo de polarización de terahercios con ancho de banda ampliado a través de metauperficies dieléctricas

- Memoria resistiva ZrO2 / ZrO2 - x / ZrO2 sin cumplimiento con comportamiento de conmutación multiestado interfacial controlable

- Convertidor de polarización con birrefringencia controlable basado en metauperficie híbrida de grafeno totalmente dieléctrico

- Célula solar híbrida de silicio nanoestructurado orgánico de alto rendimiento con estructura de superficie modificada

- Mejora dieléctrica de capacitores MIM de Al2O3 / ZrO2 / Al2O3 depositados en capas atómicas mediante recocido por microondas

- Una referencia de voltaje sin resistencia de baja potencia a nanoescala con PSRR alto

- Ge pMOSFET de alta movilidad con pasivación de Si amorfo:impacto de la orientación de la superficie

- Pasivación de Si mejorada y eficiencia de células solares PERC mediante óxido de aluminio depositado en capa atómica con recocido posterior en dos pasos