Supresión del crecimiento excesivo de filamentos en la memoria de acceso aleatorio del puente conductor mediante la estructura de dos capas Ta2O5 / TaOx

Resumen

La estructura de dos capas se ha adoptado ampliamente para mejorar la confiabilidad de la memoria de acceso aleatorio de puente conductor (CBRAM). En este trabajo, propusimos una solución conveniente y económica para lograr un Ta 2 O 5 / TaO x estructura de dos capas mediante el uso de un proceso de recocido a baja temperatura. La adición de un TaO x La capa actuó como una resistencia externa suprimiendo la corriente de desbordamiento durante la programación del set, logrando así la conmutación de autocumplimiento. Como resultado, las distribuciones de estados de alta resistencia y estados de baja resistencia mejoran debido a la supresión del fenómeno de desbordamiento. Además, la retención de LRS del CBRAM se mejora obviamente debido a la recuperación de defectos en la película de conmutación. Este trabajo proporciona un método simple y económico para mejorar la confiabilidad de CBRAM.

Introducción

La memoria de conmutación resistiva de puente conductor (CBRAM) es una tecnología innovadora y se considera memoria no volátil (NVM) de próxima generación debido a su alta escalabilidad, estructura simple, facilidad de integración 3D y operación de alta velocidad [1,2, 3]. Para una aplicación práctica, los problemas de confiabilidad, incluida la retención y la resistencia de los datos, dificultan la introducción definitiva de estos dispositivos de memoria en el mercado de la memoria. La ingeniería de estructuras es el enfoque más popular para mejorar la confiabilidad de CBRAM [4, 5, 6, 7]. Zhao y col. Inyección de cationes confinados para mejorar el rendimiento de CBRAM mediante una capa de grafeno con nanoporos [8]. Aunque la confiabilidad del dispositivo ha mejorado mucho, dificulta los costos en el control de materiales y no se puede usar en un proceso CMOS estándar. Para abordar este problema, Gong et al. propuso un método compatible con CMOS y autoalineado para formar una capa interfacial de CuSiN en un electrodo de Cu para mejorar la retención del estado de baja resistencia (LRS) [9]. Cao y col. propuso una capa de barrera de TiN para mejorar la confiabilidad del dispositivo en dispositivos CBRAM al eliminar el fenómeno de sobrecrecimiento de nanofilamentos y el comportamiento de SET negativo [10]. Los métodos anteriores utilizaron la estructura de dos capas para optimizar la confiabilidad de CBRAM de manera efectiva. Sin embargo, generan costos de flujo de proceso complejo o velocidad de programación.

En este trabajo, proponemos un método compatible con CMOS para formar un dispositivo de dos capas mediante un sencillo proceso de recocido a baja temperatura. El dispositivo de doble capa de Ta 2 O 5 / TaO x La estructura se formó espontáneamente, lo que muestra mejores características de confiabilidad en comparación con el dispositivo no recocido. La fiabilidad mejorada del dispositivo recocido puede explicarse por los filamentos concentrados formados a lo largo del límite de grano durante la programación. Además, para un dispositivo de recocido de dos capas, debido a la existencia de TaO x , el comportamiento de autocumplimiento se logra porque el TaO x La capa sirve como una resistencia en serie con un Ta 2 O 5 -capa resistiva. Este resultado proporciona un método simple compatible con CMOS para formar un dispositivo de doble capa y mejorar la confiabilidad de CBRAM.

Métodos

El tapón W con un diámetro de 1 μm después de CMP sirve como electrodo inferior (BE). Después de depositar una capa de Ta de 5 nm por pulverización catódica con magnetrón de CC, el Ta 2 O 5 se formó mediante un proceso de oxidación térmica, por debajo de 350 ° C, en plasma O 2 durante 300 s mediante deposición química en fase de vapor mejorada con plasma (PECVD). Luego, el electrodo superior (TE) de Cu de 40 nm se pulveriza catódicamente y se modela mediante litografía. Las celdas de memoria se modelan a través del proceso de grabado con una mezcla de gas SF 6 y C 3 F 8 utilizando el TE como máscara dura. Posteriormente, la almohadilla de Al extrae el BE. Finalmente, el dispositivo se completa con un proceso de recocido a baja temperatura compatible con CMOS por debajo de 400 ° C durante 30 min. El tamaño del dispositivo está definido por el área del electrodo inferior, que es 1 μm 2 . Como referencia, también se prepara el dispositivo sin el proceso de recocido. Las medidas eléctricas de CC se llevan a cabo utilizando un analizador de parámetros de semiconductores Keithley 4200-SCS. Para todas las mediciones, el voltaje se aplica al Cu TE con el W BE conectado a tierra.

Resultados y discusión

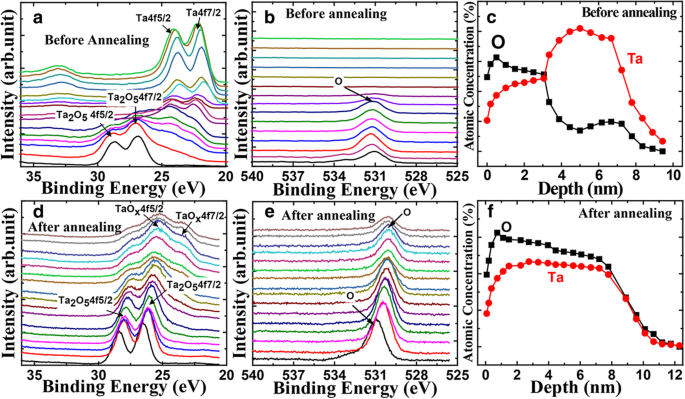

Para una visión profunda del proceso de recocido, la composición y el estado de enlace químico en el Ta 2 O 5 Las películas antes y después del proceso de recocido se analizan mediante espectroscopía de fotoelectrones de rayos X (XPS). La velocidad de grabado de la muestra es de 0,5 nm / punto. En la Fig. 1a, los picos de Ta 2 O 5 Doblete 4f con energías de enlace máximas de 26,70 eV (Ta 2 O 5 4f 7/2 ) y 28,60 eV (Ta 2 O 5 4f 5/2 ) con una separación de picos de 1,9 eV se observan en la superficie [11,12,13]. Este caso demuestra la existencia de Ta 2 O 5 capa.

El XPS muestra el perfil de profundidad de Ta antes ( a ) y después ( d ) recocido. b , e Perfil de profundidad de O antes y después del recocido, respectivamente. c, f Perfil de concentración atómica de O y Ta con profundidad antes y después del recocido, respectivamente

Con el aumento de profundidad, los picos de Ta 2 O 5 El doblete 4f desaparece y los picos a 22,33 eV, 23,96 eV correspondientes a Ta 4f 7/2 , Ta 4f 5/2 aparecer. La Figura 1b verifica que no haya señal O a la misma profundidad donde Ta 4f 7/2 y Ta 4f 5/2 existe. En otras palabras, hay Ta metálico en la superficie de Ta 2 O 5 para el dispositivo no recocido. Las profundidades del Ta 2 O 5 y Ta analizados de la Fig. 1c son 4 nm y 2,5 nm, respectivamente. Además, existe el pico de la concentración atómica de O en la profundidad de 7 nm, lo que indica la existencia del oxígeno absorbido. Las figuras 1d y e muestran los perfiles de profundidad de los espectros XPS de Ta 2 O 5 películas después del proceso de recocido. Los picos de Ta 4f doblete y Ta 2 O 5 El doblete 4f existen juntos a una cierta profundidad. La intensidad de Ta 5+ El estado de oxidación se debilita gradualmente a medida que aumenta la profundidad. Combinado con la señal de oxígeno general a lo largo de la profundidad de la película, confirmamos que el TaO x existe en la superficie de Ta 2 O 5 [11, 14]. Calculado a partir de la Fig. 1f, el espesor de Ta 2 O 5 es de 4 nm y TaO x es de 3,5 nm. Por lo tanto, el TaO x se forma cambiando el oxígeno adsorbido por oxígeno reticulado en el proceso de recocido. La redistribución de oxígeno alcanzaría un punto de saturación saturado después del proceso de recocido. El espesor de TaOx y el voltaje de formación no aumentarán aunque el tiempo de recocido aumente, lo que demuestra el gran margen de proceso de este proceso de recocido.

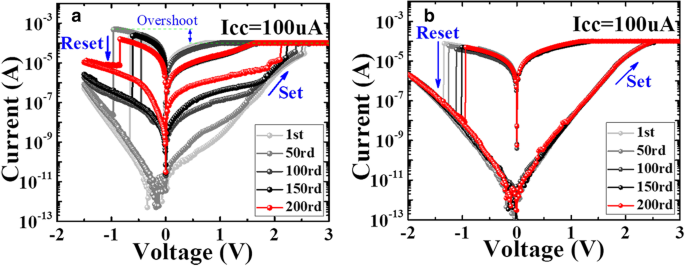

Las figuras 2a yb son las características de conmutación resistiva de Cu / Ta 2 O 5 / W antes y después del recocido en el modo de barrido de CC. Las resistencias iniciales ( R inicial ) de los dos dispositivos están en estado de alta resistencia (HRS) con valores de ~ 10 9 Ω y 10 10 Ω, respectivamente. Cuanto mayor sea la R inicial del dispositivo recocido se debe a la película de óxido más gruesa formada bajo el proceso térmico. En particular, este dispositivo no necesita un proceso de formación, lo que es bastante esperado en la aplicación práctica. Para el dispositivo no recocido, cambia a LRS abruptamente cuando el voltaje aplicado alcanza un valor crítico durante el barrido de voltaje positivo. Se produjo una LRS ultrabaja durante el proceso de fraguado. La corriente de RESET en tal caso es mucho más alta que la corriente de cumplimiento preestablecida, lo que indica que el fenómeno de sobreimpulso ocurrió en este dispositivo. La Figura 3b muestra el LRS y HRS inestables dentro de 200 ciclos para el dispositivo no recocido. La gran variación entre un ciclo y otro conduce a que la ventana de memoria se reduzca a tan solo 20. La figura 2b muestra el comportamiento de conmutación de los dispositivos recocidos. La corriente que fluye a través de la celda aumenta gradualmente y alcanza la corriente de cumplimiento. No se observa ningún punto de conmutación obvio, evitando el fenómeno de sobreimpulso ocurrido en los dispositivos no recocidos. Una ventana de memoria de hasta 10 4 se logró durante los ciclos de conmutación, debido a la distribución uniforme de HRS y LRS.

Curvas I-V típicas de dispositivos Cu / TaOx / W antes del recocido ( a ) y después del recocido ( b ) con 200 ciclos

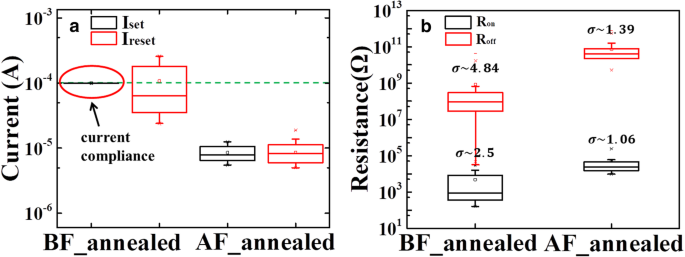

un Establezca y REINICIE las distribuciones de corriente antes y después del recocido, respectivamente. b La distribución de resistencia de HRS y LRS antes / después del recocido

La supresión del fenómeno de desbordamiento en el dispositivo recocido también podría verificarse mediante la distribución mejorada de la corriente de RESET ( I REINICIAR ) y Establecer actual ( I Establecer ) en el dispositivo recocido, como se muestra en la Fig. 3a. El yo Establecer del dispositivo no recocido está atascado en el I CC pero yo REINICIAR distribuye ampliamente. Por el contrario, para el dispositivo recocido, el I REINICIAR es similar a I Establecer . La uniformidad de dispositivo a dispositivo se evalúa analizando la R en y R desactivado en 20 dispositivos diferentes en modo DC. Como se muestra en la Fig. 3 (b), la R en extraído bajo V leer de 0,1 V para el dispositivo no recocido distribuye desde 10 2 Ω a 10 5 Ω, mientras que R en del dispositivo recocido distribuye de 10 4 Ω a 10 5 Ω. La R relativamente más alta en del dispositivo recocido resultó de la resistencia en serie del TaO x capa. Además, la distribución HRS del dispositivo recocido también se mejora mucho. Como se muestra en la Fig. 3b, la desviación estándar (SD) de R desactivado se reduce de 4.84 a 1.39.

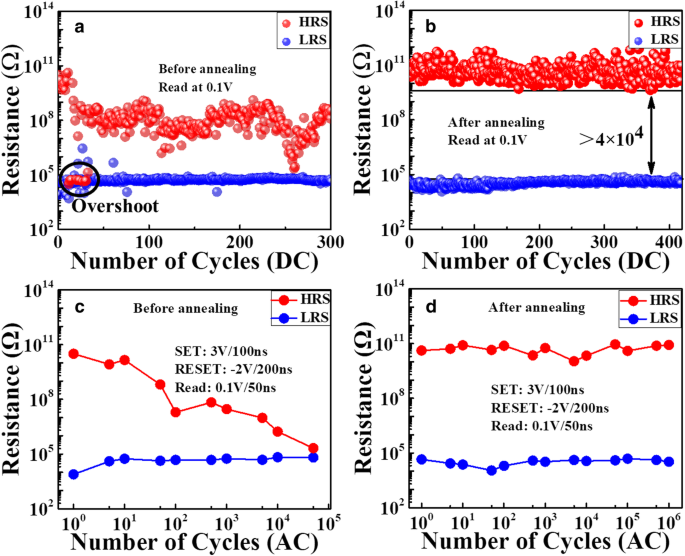

Los resultados del ciclo bajo barrido de CC se muestran en la Fig. 4a y b. Para el dispositivo no recocido, la relación HRS / LRS es de alrededor de 10 5 al principio, luego disminuye gradualmente y finalmente se mantiene en LRS. Tenga en cuenta que se pueden observar algunos errores leves durante el ciclismo, en forma de HRS (puntos rojos) y LRS (puntos azules) que se ejecutan de un lado a otro ocasionalmente. Para el dispositivo recocido, la relación HRS / LRS permanece estable (~ 10 4 ) sin ninguna degradación. Durante las mediciones de pulsos, las condiciones adecuadas de programación de pulsos se optimizan como 3 V / 100 ns para la operación de ajuste, - 2 V / 200 ns para la operación de RESET y 0,1 V / 50 ns para la operación de lectura. El tiempo de detección para la operación Set / RESET / Read es 15 ns / 12 ns / 25 ns, respectivamente. Como puede verse en la Fig. 4c, la resistencia del dispositivo no recocido suele ser inferior a 5 × 10 4 ciclos de conmutación. Sin embargo, de la Fig. 4d, es sorprendente que el dispositivo recocido todavía funcione bien sin fallas después de más de 10 6 ciclos de conmutación. Con base en nuestro estudio anterior [15], la falla de resistencia en CBRAM está relacionada con la operación RESET inestable resultante del crecimiento excesivo del filamento en el contraelectrodo. Por un lado, el filamento demasiado crecido necesita más energía para romperse y tiende a provocar un RESET incompleto y una frecuencia cardíaca más baja. Por otro lado, el crecimiento excesivo del filamento en el contraelectrodo conduce a iones de Cu residuales en el contraelectrodo, que podrían servir como depósito de iones metálicos y producir un SET negativo inesperado. Para el dispositivo recocido, el crecimiento excesivo del filamento se suprime bien mediante la incorporación de TaO x capa y da como resultado una operación de RESET más estable. Como resultado, la ventana de memoria se mantiene bien y la característica del ciclo se mejora mucho.

Los resultados de ciclismo de a los dispositivos sin recocido bajo 300 ciclos DC y b los dispositivos con recocido por debajo de 400 ciclos DC. c, d Características de resistencia en modo CA con la configuración de funcionamiento optimizada:ajuste 3 V / 100 ns; REINICIO - 2 V / 200 ns. Hasta 10 6 Se obtuvieron ciclos para el dispositivo después del recocido

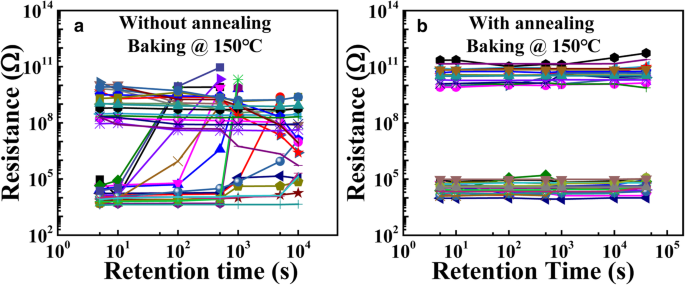

La consideración de la característica de retención juega un papel crucial para la aplicación práctica de CBRAM [16]. Las características de retención se miden por debajo de 150 ° C usando el horno de vacío. La resistencia de cada celda se verifica después de enfriarse a temperatura ambiente en cada intervalo de décadas. Las figuras 5a yb muestran la dependencia de R HRS / R LRS en el tiempo de horneado para el dispositivo sin recocido y con recocido, respectivamente. Para los dispositivos no recocidos (Fig. 5a), a medida que aumenta el tiempo, los dispositivos fallaron gradualmente dentro de los 10 4 s. Sin embargo, para el dispositivo recocido (Fig. 5b), entre los 20 dispositivos registrados, las resistencias del LRS y HRS no muestran ninguna degradación a medida que aumenta el tiempo de horneado. Es decir, la retención de los dispositivos se mejora mucho mediante el proceso de recocido. La vida útil del dispositivo recocido a 85 ° C podría extraerse como 10 años mediante el diagrama de Arrhenius, que está en buena conformidad con los CBRAM informados [17, 18]. El logro de una mejor característica de retención para el dispositivo recocido se debe a que el proceso de recocido recupera algunos defectos en la película de conmutación, lo que ralentizaría la difusión de las especies de Cu.

Características de retención del HRS / LRS para a dispositivo no recocido y b dispositivo recocido a 150 ° C

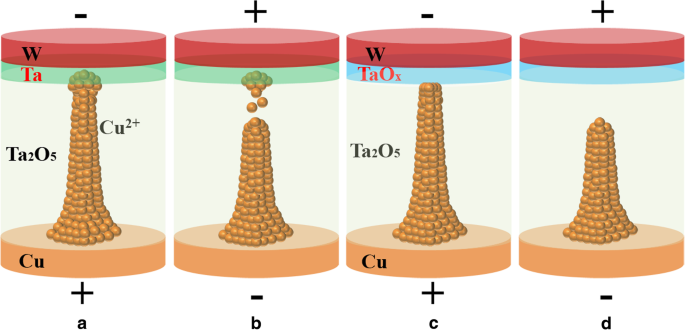

Con base en los resultados anteriores, en la Fig. 6a-d se ilustra un modelo físico para el comportamiento de conmutación de los dispositivos recocidos y no recocidos. El crecimiento de filamentos en CBRAM está asociado con el transporte de iones Cu en la red de electrolitos [19]. El fenómeno de sobreimpulso que ocurrió en el dispositivo no recocido hace que el filamento crezca en exceso en el contraelectrodo. Durante la operación RESET, los iones de Cu residuales almacenados en el contraelectrodo se desplazarán hacia el espacio del túnel entre la punta del filamento y el contraelectrodo, dando como resultado el Cu + residual al final de la operación RESET y variación grave de HRS. Como el coeficiente de difusión de Cu en TaO x (4,9 × 10 - 20 cm 2 / s) es mucho menor que en Ta (1.0 × 10 - 6 cm 2 / s), el Cu se difunde en TaO x es mucho más difícil bajo el campo eléctrico durante la operación Set en la muestra de Cu / Ta 2 O 5 / TaO x / W [20, 21]. Por lo tanto, el comportamiento de desbordamiento y el crecimiento excesivo del filamento podrían suprimirse bien y la operación RESET se vuelve más estable.

El modelado físico del comportamiento de conmutación de los dispositivos recocidos y no recocidos. El a Establecer y b Proceso de RESET para el dispositivo no recocido con la estructura de Cu / Ta 2 O 5 / Ta / W. c Establecer y d Proceso de RESET para el dispositivo recocido con la estructura de Cu / Ta 2 O 5 / TaO x / W. El crecimiento excesivo del filamento es suprimido por el TaO x capa formada durante el proceso de recocido

Conclusiones

En esta carta, investigamos las características de conmutación de un TaO x -dispositivo CBRAM basado en. A Ta 2 O 5 / TaO x La pila de dos capas se formó después de un tratamiento de recocido térmico posterior. El TaO x La capa podría actuar como una resistencia externa suprimiendo la corriente de desbordamiento durante la operación de ajuste. Tanto la distribución de HRS como la de LRS se mejoran en gran medida debido a la supresión del fenómeno de desbordamiento. Además, la retención de datos del CBRAM se mejora debido a la recuperación de defectos en la película de conmutación durante el recocido térmico. Este trabajo proporciona la solución más conveniente y económica para lograr la estructura de dos capas y mejorar la confiabilidad de CBRAM.

Abreviaturas

- CBRAM:

-

Memoria de acceso aleatorio de puente conductor

- HRS:

-

Estados de alta resistencia

- LRS:

-

Estados de baja resistencia

- NVM:

-

Memoria no volátil

- PECVD:

-

Deposición de vapor químico mejorada con plasma

- TE:

-

Electrodo superior

Nanomateriales

- FPGA de grado de defensa debuta con acceso anticipado

- Nano grafema, memoria transparente flexible basada en silicio

- Presentación de la estructura atómica y electrónica de las nanofibras de carbono de copa apilada

- Estructura y propiedades electrónicas de la nanoarcilla de caolinita dopada con metal de transición

- Preparación y rendimiento fotocatalítico de fotocatalizadores LiNb3O8 de estructura hueca

- Un estudio colectivo sobre modelado y simulación de memoria resistiva de acceso aleatorio

- Estructura electrónica y características I-V de las nanocintas InSe

- Estructura electrónica dependiente de espín y valle en silicene bajo potenciales periódicos

- Un estudio de la variabilidad en la memoria de acceso aleatorio resistivo de contacto por modelo de vacante estocástico

- Efecto de la morfología y la estructura cristalina en la conductividad térmica de los nanotubos de titania

- Consideraciones de abastecimiento de dispositivos de acceso remoto para la seguridad