Mejora del rendimiento del dispositivo a-IGZO TFT mediante un proceso de interfaz limpia a través de nanocapas Etch-Stopper

Resumen

Para superar los obstáculos tecnológicos y económicos de la placa posterior de pantalla amorfa basada en indio-galio-óxido de zinc (a-IGZO) para la producción industrial, se desarrolla un proceso limpio de tapón de ataque (CL-ES) para fabricar un delgado a base de a-IGZO Transistor de película (TFT) con uniformidad y reproducibilidad mejoradas en sustratos de vidrio de la generación 8.5 (2200 mm × 2500 mm). En comparación con un TFT basado en un IGZO con estructura grabada en el canal posterior (BCE), una nanocapa ES recién formada (~ 100 nm) y un grabado simultáneo de una nanocapa de un IGZO (30 nm) y un drenaje de fuente La capa de electrodo se introduce en primer lugar en un dispositivo TFT basado en IGZO con estructura CL-ES para mejorar la uniformidad y estabilidad del dispositivo para una visualización de gran área. La movilidad de los electrones de saturación de 8,05 cm 2 / V sy el V th La uniformidad de 0,72 V se realiza en el dispositivo TFT basado en a-IGZO con estructura CL-ES. En las pruebas de confiabilidad de tensión de iluminación de temperatura de polarización negativa y tensión térmica de polarización positiva bajo una polarización de ± 30 V durante 3600 s, el V medido th El desplazamiento del dispositivo con estructura CL-ES disminuyó significativamente a - 0,51 y + 1,94 V, que son mucho más bajos que el del dispositivo con estructura BCE (- 3,88 V, + 5,58 V). El rendimiento eléctrico del dispositivo TFT basado en a-IGZO con estructura CL-ES implica que la transferencia económica de un proceso TFT basado en silicio al proceso basado en semiconductores de óxido metálico para la fabricación de LCD es altamente factible.

Antecedentes

La placa posterior de transistor de película fina (TFT) con mayor resolución y tamaño de panel más grande es muy deseada en la industria de las pantallas planas. El material semiconductor con una alta movilidad de electrones es crucial para mejorar el rendimiento del backplane TFT. En particular, un backplane TFT basado en semiconductores de óxido metálico se considera un candidato prometedor para superar la limitación del backplane TFT basado en silicio en términos de flexibilidad mecánica y movilidad de electrones [1, 2, 3, 4]. Aunque un backplane TFT basado en semiconductores de óxido metálico muestra propiedades prometedoras, todavía se necesita el método de proceso con un proceso de bajo costo para la deposición a gran escala para aplicaciones industriales [5].

El óxido de indio-galio-zinc amorfo (a-IGZO) es un excelente semiconductor de óxido metálico con una alta movilidad de electrones de saturación (~ 5-10 cm 2 / V s) y una baja corriente de escape (<10 pA) [6,7,8,9,10]. El método de producción industrial común para el backplane de TFT basado en a-Si:H es el proceso de grabado de canal posterior de cinco máscaras (BCE). Sin embargo, la nanopelícula a-IGZO tiene una resistencia química muy baja a los agentes de grabado típicos que se utilizan actualmente en el proceso BCE. Especialmente, las nanopelículas a-IGZO se grabarían completamente en pocos segundos cuando se exponen a un grabador de Al, compuesto de ácido fosfórico, ácido nítrico y ácido acético [11,12,13]. Este grabado incontrolablemente rápido dificulta la adopción del proceso BCE para un backplane TFT basado en IGZO. Para utilizar a-IGZO en el backplane estructurado con BCE, se ha desarrollado la tecnología de cableado de Cu, como el grabador utilizado en el proceso de cableado de Cu, que se basa en H 2 O 2 , es mucho más suave para la nanopelícula a-IGZO que las que se utilizan en el cableado de Al [11, 13]. Desafortunadamente, la nanopelícula a-IGZO todavía se daña durante el proceso de cableado de Cu incluso cuando se usa un grabador más suave. Los grabadores aún más suaves causan daños en la superficie de la nanopelícula a-IGZO que forma el canal trasero de los dispositivos TFT. Estos daños provocan el colapso de la relación de composición molecular estequiométrica cerca de la superficie de una nanopelícula a-IGZO, lo que aumenta la uniformidad en la pantalla de gran área y la confiabilidad del dispositivo TFT. Hasta la fecha, se ha desarrollado un proceso convencional de seis máscaras-tapón-grabado (CV-ES) para fabricar un plano posterior TFT basado en IGZO con estructura de capa-tapón-grabado (ESL) [14, 15]. Sin embargo, este proceso de EE de seis máscaras puede conducir a una viabilidad económica negativa. Además, este mayor número de capas de película delgada aumentaría el área de superposición entre capas y daría como resultado un aumento de la capacitancia parásita y una disminución de la relación de apertura [16,17,18]. Aunque recientemente se ha informado sobre el proceso ES de cinco máscaras que produce un plano posterior TFT utilizando medio tono y tecnología de despegue, este proceso no es accesible para la producción de un plano posterior TFT basado en IGZO, ya que la superficie de su capa activa todavía está expuesta a Procesar productos químicos como el decapante y el fotorresistente en el último paso, que pueden causar una contaminación considerable a a-IGZO, reduciendo así la calidad del dispositivo y el rendimiento de producción [19,20,21]. Por lo tanto, el método de producción industrial para un backplane TFT basado en IGZO con alta uniformidad y estabilidad sigue siendo un desafío.

En este artículo, proponemos un proceso ES limpio de cinco máscaras (CL-ES) mediante la introducción de ESL para la fabricación de un backplane TFT basado en IGZO. Este proceso CL-ES recientemente desarrollado es altamente compatible con el proceso existente para el dispositivo BCE. Este proceso CL-ES está diseñado para tener las mismas máscaras que el proceso BCE, lo que garantiza una pérdida insignificante de productividad del FAB de placa posterior TFT AM-LCD existente. El backplane basado en a-IGZO producido usando el proceso CL-ES deposita el aislante de la puerta, la nanocapa IGZO y la nanocapa ES secuencialmente, luego forma una nueva máscara ESL mediante el método de grabado en seco. Esto podría evitar la contaminación de la nanocapa a-IGZO y su interfaz con el grabador, el decapante y el solvente. Esta nanomáscara recién formada ayuda a mejorar la uniformidad y estabilidad del dispositivo TFT. En comparación con el dispositivo convencional con estructura BCE, el dispositivo basado en a-IGZO con estructura CL-ES muestra un rendimiento eléctrico mejorado, es decir, una mayor movilidad de electrones de saturación, una alta relación de apertura y un bajo consumo de energía.

Métodos / Experimental

Fabricación de una placa posterior TFT basada en IGZO

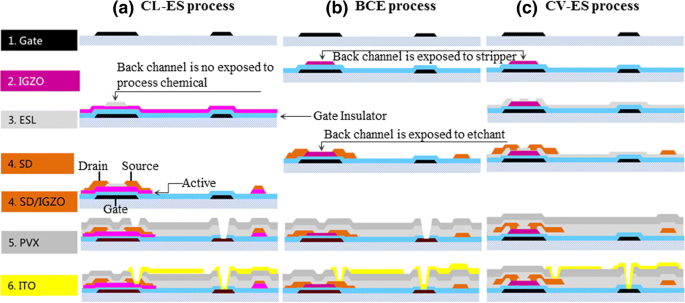

La placa posterior TFT basada en a-IGZO con estructura ES fabricada mediante el proceso CL-ES era la siguiente (Fig. 1).

(Color en línea) Esquemas de a CL-ES, b BCE y c Procesos CV-ES

En primer lugar, se utilizó una doble capa (Mo / Cu:30 nm / 250 nm) para el electrodo de puerta, ya que tiene una resistividad razonablemente baja. Luego, se depositó el aislante de la puerta, nitruro de silicio (SiNx) / óxido de silicio (SiOx) (300 nm / 100 nm), mediante el método de deposición química en fase vapor mejorada con plasma (PECVD). Esta película de SiNx está diseñada para prevenir la oxidación de la metalización de Cu y la difusión de iones de Cu en el aislador de la puerta. Posteriormente, se depositó una fina película de SiOx. Las condiciones de deposición de la película PECVD SiOx fueron potencia de RF de 17 KW, presión de 1000 mTorr, 1:55 SiH 4 / N 2 Relación de gas O y temperatura de 350 ° C. A continuación, se depositó una nanopelícula de a-IGZO a 30 nm utilizando un pulverizador catódico con magnetrón rotatorio de cc. El objetivo tenía un diámetro de 171 mm mientras que la composición era In 2 O 3 :Ga 2 O 3 :ZnO =1:1:1% en moles. Los parámetros de pulverización catódica para la nanopelícula a-IGZO fueron la presión base del sistema de 5 ~ 9 × 10 −7 Torr, potencia de pulverización rf de 10 KW, presión de pulverización catódica de 5 mTorr Ar / O 2 mezcla de gases (85% Ar-15% O 2 ). La temperatura de deposición está en condiciones ambientales. La película a-IGZO producida se templa a 330 ° C durante 1 h en un ambiente de aire limpio y seco.

En segundo lugar, se depositó la nanocapa (SiOx) de tapón de grabado (ES) utilizando el método PECVD. La nanocapa ES se deposita simultáneamente para evitar la contaminación en la capa a-IGZO. Al igual que en el proceso BCE, no hay una capa protectora para la nanopelícula a-IGZO antes del proceso de modelado de electrodos S / D, la contaminación de la superficie y el daño en la nanopelícula a-IGZO por el grabador S / D cuando la formación del canal TFT es inevitable. La nanocapa ES en el proceso CL-ES puede proteger eficazmente el canal TFT de la contaminación y los daños externos. La nanocapa ES se depositó hasta un espesor de 100 nm. Las condiciones de deposición de la película delgada de SiOx fueron potencia de RF de 17 KW, presión de 1000 mTorr, 1:66 SiH 4 / N 2 Relación de gas O y temperatura de 240 ° C. La nano-máscara ES producida se grabó mediante grabado en seco y modelado. Durante el proceso de grabado, CF 4 y O 2 se suministraron gas a una velocidad de 2000 sccm / 800 sccm.

En tercer lugar, también se utilizó Mo / Cu / Mo para el electrodo S / D. Para seleccionar el electrodo S / D de a-IGZO TFT, se consideró que la diferencia de función de trabajo entre el metal y el a-IGZO formaba un contacto óhmico y los materiales de baja resistividad. Como se describe en el proceso de grabado-tapón, durante el modelado de la nano-máscara ES, las nano-películas a-IGZO, que no están protegidas por la capa de tapón, ya se llevan a cabo bombardeando con CF 4 plasma. Por lo tanto, el contacto óhmico se forma naturalmente con Mo / Cu / Mo [22]. Las capas S / D se depositaron en un espesor de 30 nm / 300 nm / 30 nm con las mismas condiciones de pulverización catódica que el electrodo de puerta. Además, se grabaron por lotes capas de película multi-fina de Mo / Cu / Mo y a-IGZO usando “H 2 O 2 grabador de Cu que contiene un aditivo de fluoruro ”para completar el electrodo S / D. Los 30 nm de Mo añadidos encima del Cu se formaron para evitar la oxidación de la superficie de Cu mediante la película de pasivación (SiOx) en el siguiente proceso y para evitar el daño del plasma en la superficie de Cu, durante el grabado en seco para la formación de orificios de pasivación.

En cuarto lugar, la película de pasivación, dividida en dos tipos de película delgada, se depositó utilizando el método PECVD. La primera pasivación se realizó con película delgada de SiOx. La película delgada tenía un espesor de 250 nm. La segunda pasivación estuvo constituida por una película fina de SiNx. El espesor de la película delgada era de 200 nm.

En quinto lugar, como electrodo de píxel, se utilizó la película de óxido de indio y estaño (ITO), que se utiliza con mayor frecuencia en la industria de las pantallas. La película de ITO tenía un grosor de 40 nm y se utilizó pulverización catódica de cc para la deposición. Luego, el recocido final se llevó a cabo en un ambiente de aire limpio y seco a 230 ° C durante 1 h usando un horno de aire caliente. Las características eléctricas de los TFT a-IGZO fabricados se midieron utilizando el sistema de prueba paramétrica Keysight 4082A. Este proceso obtendrá el mismo número de máscaras (estándar de producto TN:cinco máscaras) que el proceso BCE, que es ampliamente utilizado en la fabricación en masa.

A modo de comparación, se fabricó un backplane TFT basado en IGZO con estructura BCE mediante el proceso BCE.

Caracterización

La medición de I-V de TFT se realizó a temperatura ambiente utilizando un analizador de características de semiconductores. La condición de análisis para evaluar la estabilidad del TFT bajo tensión de iluminación de temperatura de polarización de puerta negativa (NBTIS) fue la siguiente. V gs y V ds se fijaron respectivamente a -30 y 15 V, y la temperatura del sustrato se mantuvo a 60 ° C. La luminancia para NBITS se estableció en 5000 cd / m 2 . La duración de la tensión para la evaluación continuó durante 3600 s [23]. Se probó el estrés térmico de polarización de puerta positiva (PBTS) a V gs de 30 V y una V ds de 15 V, y la temperatura del sustrato se fijó en 60 ° C. La duración del estrés para la evaluación continuó durante 3600 s [24].

Resultados y discusión

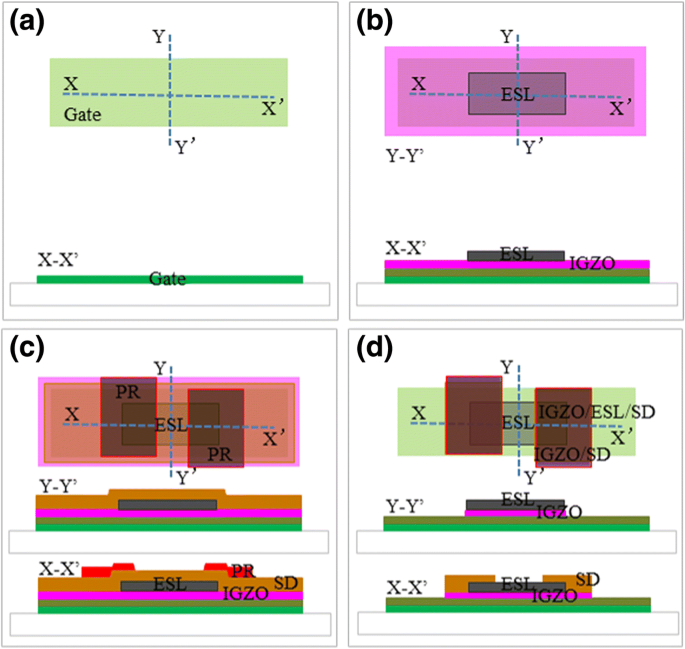

El TFT basado en a-IGZO fabricado mediante el proceso CL-ES muestra el mismo número de máscara que el del proceso BCE (Fig. 1). En comparación con el TFT basado en a-IGZO con estructura BCE, el TFT basado en a-IGZO con estructura CL-ES muestra dos ventajas:(1) plano posterior basado en a-IGZO producido con el aislante de compuerta de depósitos de proceso CL-ES, a-IGZO nano -capa y nano-capa ES secuencialmente, luego forma una nano-máscara ESL a través del método de grabado en seco. Esta nano-máscara de ESL recién formada con 100 nm puede prevenir la exposición de una nano-película de IGZO al grabador, decapante o fotorresistente. Por lo tanto, se previene eficazmente la contaminación en las interfaces entre capas [25]. (2) Al mismo tiempo, la nanopelícula a-IGZO no está protegida por la capa ES sino bombardeada por CF 4 plasma durante la formación de la nano-máscara ESL, por lo tanto se convierte en un conductor. Esto naturalmente forma el contacto óhmico entre el electrodo S / D del siguiente proceso y el semiconductor a-IGZO. Por otra parte, un grabado simultáneo de nanocapa S / D y a-IGZO puede ser un margen de superposición de la capa ESL- (a-IGZO + S / D metalización), lo que podría disminuir los dos errores del proceso de superposición del a- Capa de metalización IGZO-ESL y ES-S / D en el proceso ESL convencional (Fig. 2). El número de superposición de la capa a-IGZO, ES y S / D se reduce, lo que resultó en una disminución en el tamaño del dispositivo TFT que redujo la capacitancia parásita. La estructura planar de resultados es similar a la estructura BCE (Fig. 3a, b).

(Color online) Esquemas del método de formación simultánea para canal TFT y electrodo S / D en proceso CL-ES. un El primer paso que forma el electrodo de puerta. b El segundo paso que forma la capa de tapón de grabado. c El tercer paso que forma el patrón fotográfico S / D. d El cuarto paso que forma el electrodo S / D y el patrón activo

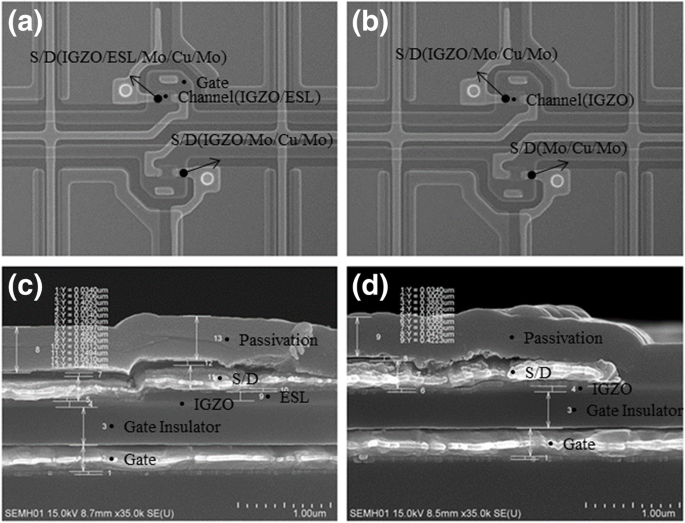

(Color en línea) Imágenes SEM de a-IGZO TFT ( a , b vista superior; c , d vista lateral) con estructura CL-ES ( a , c ) y estructura BCE ( b , d )

La Figura 3 muestra las imágenes SEM de TFT basados en a-IGZO con estructura CL-ES (Fig. 3a, c) y estructura BCE (Fig. 3b, d). Desde la vista superior, es difícil identificar las diferencias entre la estructura CL-ES y la estructura BCE (Fig. 3a, b). Desde la vista lateral, se puede encontrar una nanocapa ES entre la nanocapa a-IGZO y la capa de electrodo S / D en la estructura CL-ES (Fig. 3c). Mientras tanto, se puede encontrar una capa de pasivación en la parte superior de una nanocapa a-IGZO en la estructura BCE (Fig. 3d). En el proceso CL-ES presentado, se deposita una nanocapa a-IGZO con un espesor de 30 nm. Además, el daño durante el grabado en húmedo es insignificante. Para el proceso BCE, se deposita una nanocapa de a-IGZO de 70 nm, ya que la capa de a-IGZO necesita compensación por la pérdida de grabado. La diferencia entre los espesores de las nanocapas de a-IGZO en las estructuras CL-ES y BCE se puede observar en las imágenes SEM (Fig. 3c, d).

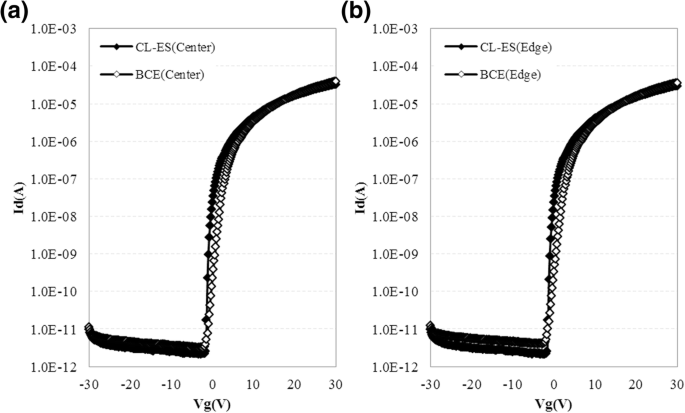

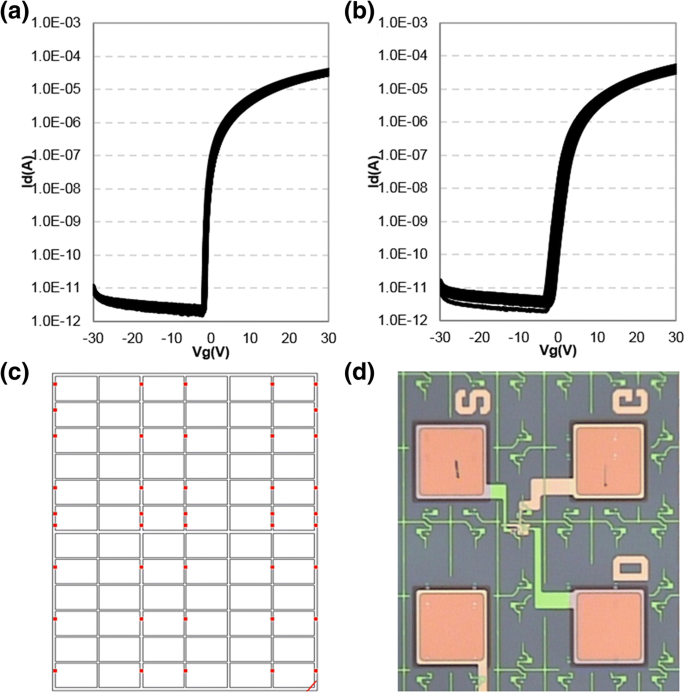

Se comparan las características I-V de TFT basado en a-IGZO con estructura CL-ES y estructura BCE (Fig. 4). La movilidad del electrón de saturación, el voltaje umbral, el valor de oscilación del voltaje subumbral (SS) y más valores característicos se resumen en la Tabla 1. Tenga en cuenta que los valores resumidos en la Tabla 1 son el número promedio derivado del centro y borde de un sustrato de vidrio de generación 8.5. . El TFT basado en a-IGZO con estructura CL-ES realiza V th de - 0,8 V, valor SS de 0,18 V / dec y movilidad de electrones de saturación de 8,05 cm 2 / V s. En el TFT basado en a-IGZO con estructura BCE, los resultados correspondientes son V th de + 0,5 V, valor SS de 0,77 V / dec y movilidad de electrones de saturación de 6,03 cm 2 / V s. En comparación con la estructura BCE, la estructura CL-ES muestra un rendimiento mejorado del dispositivo. Sin embargo, la característica en corriente del dispositivo TFT basado en a-IGZO con estructura CL-ES es menor que la del dispositivo estructurado BCE. Esto se debe al hecho de que las estructuras de canal TFT son diferentes en las estructuras CL-ES y BCE. Generalmente, la longitud del canal TFT estructurado con BCE es la distancia entre los electrodos metálicos S / D, y la longitud del canal medida en este estudio es de 5 um [21]. En la estructura CL-ES, los electrodos están en contacto con la nano-película a-IGZO que se estira al costado de la nano-máscara ESL. Por lo tanto, la longitud del canal se decide por la distancia entre los a-IGZO definidos en los lados del tapón de grabado, pero no determinada por la distancia entre los electrodos. La longitud del canal del presente dispositivo de estructura CL-ES se mide en 10 um.

(Color en línea) Comparación de la característica I-V de los TFT a-IGZO con la estructura CL-ES y BCE en el centro ( a ) y borde ( b ) de sustrato de vidrio de generación 8.5

Como se muestra en la Tabla 1, los valores medidos de I en / Yo desactivado proporción (~ 10 6 , consulte la Tabla 1) son aproximadamente 10 veces más pequeñas que el valor típico (> 10 7 ) de TFT basados en a-IGZO. Esto se debe a que el equipo de medición utilizado aquí es para la producción en masa de la generación 8.5. Para estas medidas son necesarios cables largos, ya que el tamaño del equipo industrial es grande. Los cables largos produjeron un aumento del ruido de medición. En las siguientes pruebas de confiabilidad, se utilizan equipos de medición a menor escala y los dispositivos TFT individuales se usan como muestra para la medición. De esta manera, el I medido en / Yo desactivado todas las proporciones son 10 superiores 7 (ver más abajo).

El proceso CL-ES está cuidadosamente diseñado para evitar que la capa del canal a-IGZO se exponga al grabador, fotorresistente o decapante. Durante el proceso que produce el proceso CL-ES, el aislante de la compuerta, la nanocapa a-IGZO y la nanocapa ES, cada interfaz entre capas está en contacto solo con agua DI para fines de limpieza. Por tanto, la contaminación química es insignificante en la capa aislante y en la nanocapa a-IGZO [25, 26]. Sin embargo, el proceso BCE no solo expone la capa del canal a los productos químicos, sino que también implica la contaminación por difusión de iones Cu, ya que el canal a-IGZO está directamente expuesto al metal Cu. Esto también se evita en dispositivos con estructura CL-ES. La región del canal de la nano-película a-IGZO está bien protegida por la nano-máscara ESL. La baja contaminación química en el proceso CL-ES puede conducir a una baja densidad de trampa de portadores en la interfaz entre la nanocapa a-IGZO y la capa aislante, lo que da como resultado un excelente valor de SS. Esta baja contaminación química del dispositivo TFT basado en a-IGZO a través del proceso CL-ES también ayuda a mejorar la uniformidad y reproducibilidad de a-IGZO TFT, que son muy importantes en la producción industrial [27, 28].

La Figura 5 muestra la característica I-V medida de los TFT con estructura CL-ES y estructura BCE derivada de 42 puntos de medición en un sustrato de generación 8.5. TFT basado en a-IGZO con estructura CL-ES tiene una V th rango de 0,72 V, mientras que el del dispositivo estructurado BCE es 2,14 V (Tabla 1). En otras palabras, la uniformidad del rendimiento del dispositivo se mejora significativamente con la estructura CL-ES.

(Color en línea) a Estructura CL-ES. b Característica de transferencia I-V de TFT de la estructura BCE. c 42 puntos de medición. d la foto de TFT. Todo medido en un sustrato de generación 8.5

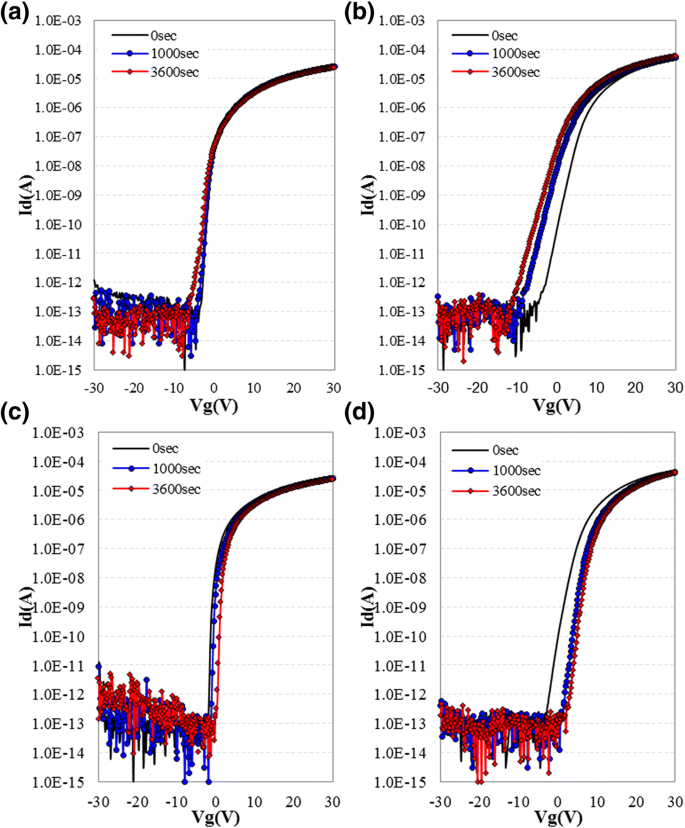

Las Figuras 6a, b muestran el cambio característico I-V del dispositivo estructurado CL-ES y el dispositivo estructurado BCE obtenido en las pruebas NBTIS, respectivamente. Los resultados de la prueba NBTIS se resumen en la Tabla 2. Bajo la condición de estrés descrita en la Tabla 2, el V th El desplazamiento del dispositivo con estructura CL-ES y el dispositivo con estructura BCE son - 0,51 y - 3,88 V, respectivamente. Además, el cambio en corriente, el cambio fuera de corriente y la variación del valor SS del dispositivo con estructura CL-ES son todos más bajos que los del dispositivo con estructura BCE (Tabla 2); esto se debe a que un dispositivo basado en un-IGZO con estructura CL-ES puede prevenir eficazmente la contaminación de un a-IGZO y una menor densidad de trampa de portadores del canal a-IGZO TFT. Especialmente, cuando se mira el resultado de los primeros 1000 s de estrés, no se observa ningún cambio en el valor de SS en el dispositivo con estructura CL-ES. Este fenómeno es comparable al aumento de 0,16 V / dec en el valor SS del dispositivo con estructura BCE, ya que muestra que los sitios defectuosos, que pueden formar trampas de portadores en la superficie de una nanopelícula a-IGZO que constituye el canal trasero CL-ES TFT, no se crean adicionalmente por estrés eléctrico o de iluminación. Estos resultados demuestran completamente que el dispositivo con estructura CL-ES es mucho más estable que el dispositivo con estructura BCE. Las figuras 6c, d muestran el desplazamiento de la curva I-V de los TFT con estructura CL-ES y BCE obtenidos de las pruebas PBTS. Los resultados detallados de las pruebas de PBTS se resumen en la Tabla 3. Tanto el TFT con estructura CL-ES como el TFT con estructura BCE han disminuido en la corriente iónica durante la evaluación de PBTS. Esto es causado por el cambio en V th a la dirección positiva. Durante la evaluación de PBTS, la relación de corriente de iones residuales [(último ion / ion inicial) × 100] del TFT con estructura CL-ES con V relativamente más pequeño th El desplazamiento positivo (+ 1,94 V) está en el nivel del 88,2%. En comparación con la relación de corriente de iones residuales del TFT estructurado con BCE del 41,3%, el TFT estructurado con CL-ES es significativamente superior. Esto muestra la importante diferencia de capacidad durante el diseño de la unidad de puerta en el circuito de matriz (GOA). A diferencia del NBTIS, el valor SS del TFT con estructura CL-ES no tiene una variación significativa ((∆SS 0.06 V / dec), o más bien disminuye (∆SS - 0.86) como en el TFT con estructura BCE. Esto quizás se deba a la portadores, se acumulan en el espacio interior y la interfaz entre el aislante de la puerta y la nanopelícula a-IGZO por polarización de la puerta positiva, llenando el sitio de la trampa del portador en la etapa inicial, lo que provoca una disminución en el fenómeno de la trampa del portador. Además, el fenómeno de cambio de voltaje del umbral se produce por carga portadora atrapada cerca de la interfaz entre el aislador de la puerta y la nanopelícula a-IGZO. Un pequeño cambio de voltaje de umbral de TFT con estructura CL-ES representa que la interfaz y el espacio interior de a-IGZO están notablemente limpios. En conclusión, las pruebas PBTS también sugiere que la estructura y el proceso de CL-ES conducen a una mejor confiabilidad del dispositivo.

(Color en línea) Deriva característica de transferencia I-V de CL-ES ( a , c ) y BCE ( b , d ) TFT obtenido de NBITS ( a , b ) y pruebas PBTS ( c , d )

Conclusiones

En conclusión, se ha desarrollado con éxito un proceso CL-ES recientemente desarrollado para fabricar un backplane TFT basado en IGZO con cinco máscaras para visualización avanzada. El proceso CL-ES tiene las ventajas de una estructura de capa de tapón de grabado al mismo tiempo que mantiene el mismo número de máscaras y áreas de dispositivo similares a un proceso BCE, lo que supera el problema del aumento del número de máscaras y el área ocupada en los dispositivos TFT convencionales de tapón de grabado. . Una nano-máscara ESL recién formada y un grabado simultáneo de una nanocapa a-IGZO y una nanocapa de electrodo S / D permiten una alta uniformidad y estabilidad del dispositivo para una visualización de gran área. Con respecto al rendimiento eléctrico, la reproducibilidad y fiabilidad del rendimiento del dispositivo de un TFT basado en a-IGZO con estructura CL-ES son mucho mejores que las del dispositivo con estructura BCE. El dispositivo TFT basado en a-IGZO tiene una V th distribución sobre 42 puntos de medición TFT en el sustrato de vidrio de generación 8.5 de 0.72 V, movilidad de electrones de saturación de 8.05 cm 2 / V s, y valor SS de 0,18 V / dec. De acuerdo con los resultados de la evaluación de confiabilidad obtenidos de NBTIS y PBTS, V th las variaciones antes y después de la tensión de los TFT basados en CL-ES a-IGZO son - 0,51 y 1,94 V después de 3600 s de tensión, respectivamente. Las variaciones del valor SS son 0,33 y 0,06 V / dec. Por lo tanto, al superar los obstáculos tecnológicos y económicos, la técnica CL-ES presentada allanará el camino para los productos de pantalla grande y de alta resolución de próxima generación.

Abreviaturas

- a-IGZO:

-

Óxido de indio-galio-zinc amorfo

- AM-LCD:

-

Pantalla de cristal líquido de matriz activa

- BCE:

-

Grabado del canal trasero

- ESL:

-

Capa de tapón de grabado

- GOA:

-

Unidad de puerta en matriz

- NBTIS:

-

Esfuerzo de iluminación de temperatura de polarización negativa

- PBTS:

-

Estrés de temperatura de sesgo positivo

- SiNx:

-

Nitruro de silicio

- SiOx:

-

Óxido de silicio

- SS:

-

Oscilación del subumbral

- TFT:

-

Transistor de película fina

- LCD TN:

-

Pantalla de cristal líquido nemático retorcido

Nanomateriales

- Uso de tecnologías sin agua en el proceso de teñido

- Interruptor de selección de arranque de hardware con Pico

- Uso de la eficacia general del equipo

- Estrategias para gestionar el rendimiento de los activos

- Uso de la gestión del rendimiento de los activos para maximizar el valor de los activos

- Ingeniería del proceso de recubrimiento por inmersión y optimización del rendimiento para dispositivos electrocrómicos de tres estados

- Compuesto híbrido Nanoestructurado de sílice / oro-celulosa-Amino-POSS mediante el proceso Sol-Gel y sus propiedades

- Fabricación de estructuras periódicas 3D basadas en nanocapas mediante el proceso de creación de plantillas utilizando ZnO derivado de la solución

- Mejora significativa de fotodetectores de metal-semiconductor-metal de MgZnO mediante el acoplamiento con plasma de superficie de nanopartículas de Pt

- Uso de una impresora 3D para mejorar su proceso de fabricación - Video

- Ventajas de usar VIA en pads