Estudio comparativo de transistores de efecto de campo de capacitancia negativa con diferentes capacitancias MOS

Resumen

Demostramos el efecto de capacitancia negativa (NC) de HfZrO x transistores de efecto de campo (FET) basados en los experimentos. I mejorado DS , SS y G m de NCFET en comparación con el semiconductor de óxido metálico de control (MOS) FET. En este experimento, los transistores MIS inferiores con diferentes tiempos de pasivación son equivalentes a los dispositivos NC con diferentes capacitancias MOS. Mientras tanto, las propiedades eléctricas de NCFET con pasivación de 40 min son superiores a las de NCFET con pasivación de 60 min debido a la buena correspondencia entre C FE y C MOS . Aunque no se logra SS de menos de 60 mV / década, se obtienen las características de transferencia no histeréticas beneficiosas para las aplicaciones lógicas.

Introducción

Con la reducción del transistor, el nivel de integración del circuito integrado (IC) está creciendo continuamente. Es urgente resolver un problema de disipación de energía que lo acompaña. Para evitar este problema, debe reducirse la tensión de funcionamiento del transistor [1]. La oscilación del subumbral (SS) del MOSFET no puede estar por debajo de 60 mV / década a temperatura ambiente, lo que restringe la reducción del voltaje umbral V TH y tensión de alimentación V DD [2]. Se han dedicado muchos esfuerzos a la investigación y el desarrollo de dispositivos con mecanismos novedosos de transporte y conmutación para superar el límite de Boltzmann, incluido el transistor de efecto de campo de capacitancia negativa (NCEFT) [3, 4], puerta resistiva FET [5], nano- FET electromecánico (NEMFET) [6, 7], semiconductor de óxido metálico de ionización por impacto (I-MOS) [8, 9] y FET tunelizado [10, 11]. Entre ellos, NCFET ha despertado mucha atención porque puede lograr un SS pronunciado sin perder la corriente de excitación [12,13,14,15]. Dopado HfO 2 (por ejemplo, HfZrO x (HZO) y HfSiO x ) se ha utilizado ampliamente en NCFET [4, 16, 17]; es compatible con el proceso CMOS [18]. Un estudio teórico ha demostrado que la histéresis no deseada se produce debido a una capacitancia ferroeléctrica incomparable C FE a la capacitancia subyacente del MOS C MOS en NCFET [19]. Sin embargo, el efecto de la coincidencia entre C FE y C MOS sobre las características eléctricas de los NCFET sigue siendo una preocupación en los experimentos.

En este trabajo se estudian las características eléctricas de los FET NC Ge con diferentes capacitancias MOS en función de las diferentes coincidencias entre C FE y C MOS . Aunque no aparece SS menor a 60 mV / década, se obtienen las características de transferencia sin histéresis y mejores propiedades eléctricas. Picos aparentes de C FE versus V FE Las curvas demuestran el efecto NC de los NCFET basados en HZO. La mejor coincidencia de C FE y C MOS contribuye a una SS más pronunciada y a una mayor corriente, lo que es beneficioso para las aplicaciones lógicas.

Métodos

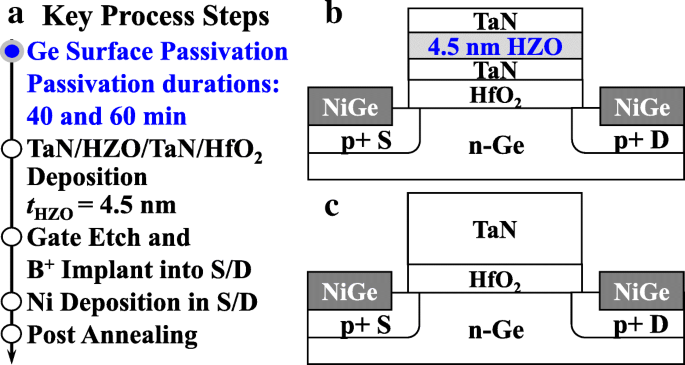

El proceso de fabricación de claves de Ge NCFET se muestra en la Fig. 1a. Se utilizaron obleas n-Ge (001) de cuatro pulgadas con una resistividad de 0.088-0.14 Ω · cm como sustratos de partida. Después de la limpieza previa a la compuerta, las obleas de Ge se cargaron en una cámara de vacío ultra alto para la pasivación de la superficie usando Si 2 H 6 . Se utilizaron dos duraciones de pasivación de 40 y 60 min. Luego, TaN / HZO / TaN / HfO 2 se depositó la pila. Los espesores del HfO 2 La capa dieléctrica y la capa HZO FE son 4,35 y 4,5 nm, respectivamente. Después del modelado y grabado de la puerta, se implantaron regiones de fuente / drenaje (S / D) utilizando iones de boro (B + ) a una energía de 30 keV y una dosis de 1 × 10 15 cm −2 . El níquel metálico S / D se formó mediante un proceso de despegue. Finalmente, se llevó a cabo un recocido térmico rápido a 450 ° C durante 30 s. Controle MOSFET con TaN / HfO 2 También se fabricó una pila. Las Figuras 1b yc muestran los esquemas del NCFET fabricado y el MOSFET de control, respectivamente. La compuerta de metal interna en el NCFET fabricado contrarresta el potencial en la superficie del canal, que se denomina estructura MFMIS.

un Pasos clave del proceso de dispositivos NC fabricados. Los esquemas de la b fabricada NCFET y c controlar MOSFET

Resultados y discusión

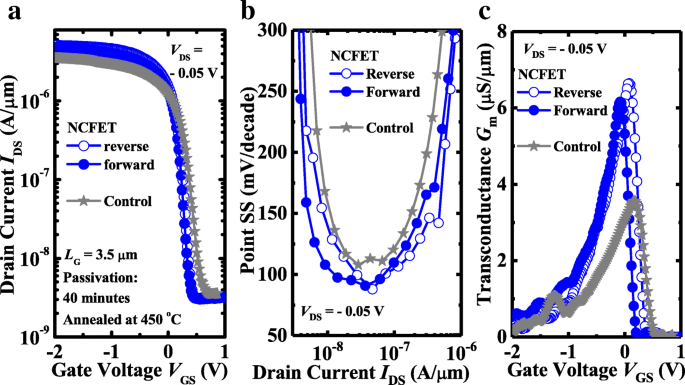

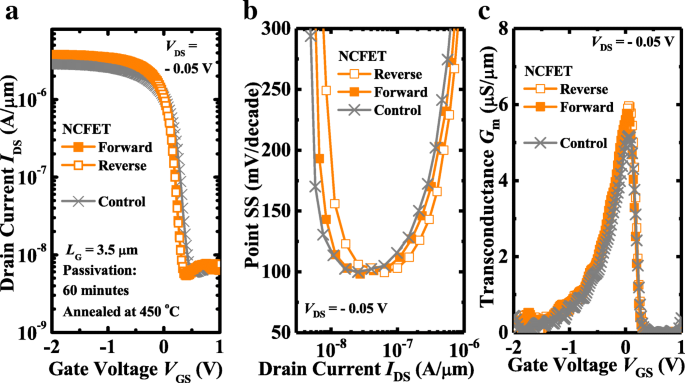

La Figura 2a traza el I medido DS - V GS curvas de un par de NCFET y control MOSFET con 40 min de pasivación de superficie. Ambos dispositivos tienen una longitud de puerta L G de 3,5 μm. El dispositivo NC con pasivación de 40 min tiene una I significativamente mejorada DS que el control MOSFET. Las curvas de transferencia de NCFET exhiben una característica no histerética. Punto SS versus I DS Las curvas de la Fig. 2b muestran que el transistor NC ha mejorado SS sobre el dispositivo de control, aunque no aparece SS de menos de 60 mV / década. La Figura 2c muestra que el transistor NC obtiene una transconductancia lineal mejorada significativamente G m sobre el dispositivo de control en V DS de - 0.05 V. La Figura 3 compara los rendimientos eléctricos de NCFET y control MOSFET con pasivación de superficie durante 60 min. Del mismo modo, el I DS , punto SS y G m de NCFET son superiores a los de control MOSFET.

un El I medido DS - V GS curvas del NCFET y control MOSFET con pasivación de 40 min. Comparación de b punto SS versus I DS y c G m características entre NC FET y control MOSFET

un El I medido DS - V GS curvas del NCFET y control MOSFET con pasivación de 60 min. Comparación de b punto SS versus I DS y c G m características entre NCFET y control MOSFET

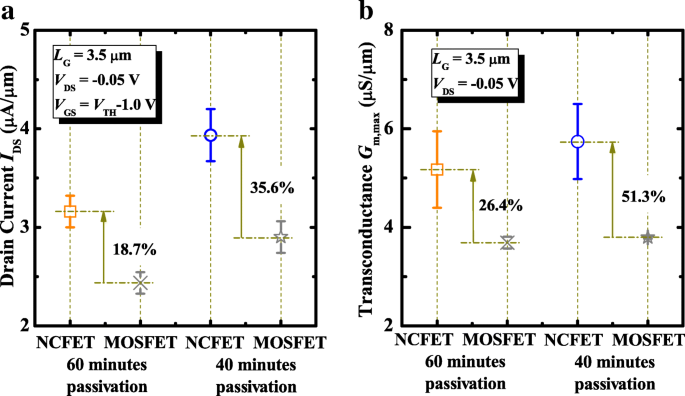

La Figura 4a muestra los resultados estadísticos de la corriente de excitación de los NCFET y los MOSFET de control en V DS de - 0,05 V y V GS - V TH =- 1.0 V. Los NCFET demuestran una mejora del 18,7% y del 35,6% en I DS para la pasivación superficial de 60 min y 40 min, respectivamente, en comparación con los dispositivos de control. Se especula que los NCFET pasivados durante 40 minutos tienen una mejor coincidencia entre C MOS y C FE sobre los dispositivos NC con 60 min. La figura 4b muestra que los NCFET obtienen una mejora del 26,4% y del 51,3% en la transconductancia máxima G m, máximo durante 60 min y 40 min de pasivación superficial, respectivamente, en comparación con los dispositivos de control. Se ve que los MOSFET de control con pasivación de superficie durante 40 min tienen un I superior DS y G m, máximo que los dispositivos pasivados durante 60 minutos, lo que se debe a que la C MOS inducida por el menor espesor de óxido equivalente ( E OT ). La puerta metálica interna proporciona un plano equipotencial; el dispositivo se puede modelar de manera equivalente como un divisor de voltaje capacitivo. La capacitancia total C G es una serie de C FE y C MOS . El voltaje de la puerta interna se amplifica debido al efecto NC. El coeficiente de amplificación de voltaje interno β =∣ C FE ∣ / ∣ C FE ∣ - C MOS obtiene el máximo cuando | C MOS | =| C FE | [20, 21]. Lograr la coincidencia optimizada de C FE y C MOS es el requisito previo para la mejora de la corriente.

La a estadística yo DS y b G m resultados de NCFET y MOSFET de control con duraciones de pasivación de 40 y 60 minutos

El V extraído int versus voltaje de puerta V GS las curvas se muestran en la Fig. 5a. V int del transistor NC se puede extraer teniendo en cuenta la hipótesis de que I DS - V int La curva del transistor NC es exactamente idéntica a I DS - V GS curva del dispositivo de control. El coeficiente de amplificación de voltaje interno dV int / dV GS se muestra en la Fig. 5b. d V int / d V GS > 1 se logra en el amplio rango de barrido de V GS para el NCFET con pasivación de superficie de 40 min, lo que contribuye a una SS más pronunciada que el dispositivo de control durante el proceso de medición, que se debe a la conmutación de polarización local [22]. Es consistente con los resultados antes mencionados en la Fig. 2b. Para el NCFET con pasivación de 60 min, el coeficiente de amplificación de voltaje interno d V int / d V GS > 1 se logra durante el rango de V GS <0 V para el doble barrido de V GS , que está de acuerdo con el SS elevado en la Fig. 3b.

un V extraído int en función de V GS curvas. b El coeficiente de amplificación de voltaje interno versus V GS curvas

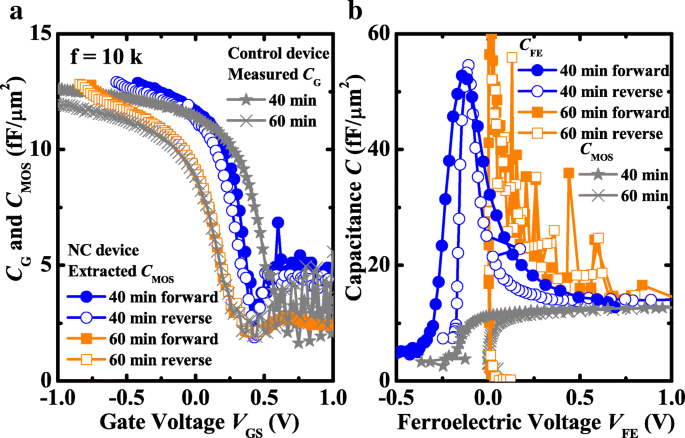

La figura 6a muestra la C extraída MOS versus V GS curvas para el transistor NC, que se basa en el V int - V GS en la Fig. 5a y la C G - V GS curvas de control MOSFET. La C extraída MOS está de acuerdo con la C medida G. Por tanto, se demuestra la validez del método de cálculo. La C FE y C MOS versus V FE las curvas se muestran en la Fig. 6b. Desde el inicio del efecto NC, el valor absoluto de C negativo FE del transistor excede C MOS para doble barrido de V GS todo el tiempo en la Fig. 6b. | C FE |> C MOS y C FE <0 puede causar características sin histéresis y la coincidencia de C MOS y C FE es beneficioso para las aplicaciones lógicas [23, 24]. Características libres de histéresis en las Figs. 2a y 3a se atribuyen a todas las coincidencias de dominios y captura de carga inhibida [25]. La conmutación de polarización estable es responsable de las características no histeréticas [26]. Además, la gran ganancia de puerta interna d V int / d V G > 1 se atribuye a la ligera discrepancia entre | C FE | y C MOS en la región de subumbral, lo que resulta en la SS pronunciada del dispositivo NC. Mientras tanto, hay una mejor coincidencia entre C FE y C MOS para el NCFET con pasivación de 40 min que el NCFET con pasivación de 60 min. Por lo tanto, esto proporciona evidencia directa para indicar que el NCFET con pasivación de 40 min posee un mejor rendimiento eléctrico que el NCFET con pasivación de 60 min. La polarización FE cambia el V FE ; por tanto, la carga de FE varía. La carga total se multiplica, lo que se atribuye a la polarización FE además del incremento de V GS . En otras palabras, para el V dado GS , la carga en el canal aumenta, por lo que I DS mejora. Como consecuencia, la característica de transferencia SS pronunciada aparece en los experimentos.

un Medido C G y extrajo C MOS en función de V GS . b C FE y C MOS versus V FE curvas

Conclusiones

Las características de transferencia sin histéresis se obtienen para los NCFET con pasivación de 40 y 60 min. Los pFET de NC Ge con pasivación de 40 min tienen mejores características eléctricas que el dispositivo NC con pasivación de 60 min en los experimentos. También demostramos el efecto NC de los NCFET basados en HZO. Para NCFET, la SS empinada y d V int / d V GS > 1 se obtienen. El NCFET con pasivación de 40 min ha logrado una buena correspondencia entre C FE y C MOS , que contribuye a las características no histeréticas. Se considera que los diferentes comportamientos de NC están relacionados con el cambio de la pared del dominio microscópico en las películas delgadas de FE.

Disponibilidad de datos y materiales

Los conjuntos de datos que respaldan las conclusiones de este artículo se incluyen en el artículo.

Abreviaturas

- B + :

-

Iones de boro

- E OT :

-

Espesor de óxido equivalente

- FET:

-

Transistores de efecto de campo

- HZO:

-

HfZrO x

- IC:

-

Circuito integrado

- I-MOS:

-

Semiconductor de óxido de metal de ionización por impacto

- MOS:

-

Semiconductor de óxido de metal

- NC:

-

Capacitancia negativa

- NCFET:

-

Transistor de efecto de campo de capacitancia negativa

- NEMFET:

-

FET nanoelectromecánico

- S / D:

-

Fuente / drenaje

- SS:

-

Oscilación del subumbral

Nanomateriales

- Transistores, efecto de campo de unión (JFET)

- Transistores, efecto de campo de puerta aislada (IGFET o MOSFET)

- Transistores de efecto de campo de unión

- Transistores de efecto de campo de puerta aislada (MOSFET)

- Introducción a los transistores de efecto de campo de unión (JFET)

- Introducción a los transistores de efecto de campo de puerta aislada

- MoS2 con espesor controlado para evolución electrocatalítica de hidrógeno

- Transistores de efecto de campo de nanoflake SnSe multicapa con contactos au óhmicos de baja resistencia

- Estudio del efecto de la dirección de impacto en el proceso de corte nanométrico abrasivo con dinámica molecular

- Fabricación, caracterización y actividad biológica de sistemas de nanoportación de avermectina con diferentes tamaños de partículas

- Un estudio de nanofibras de carbono y carbón activo como supercondensador simétrico en un electrolito acuoso:un estudio comparativo