Una SRAM 4T integrada de RRAM con carga de conmutación resistiva autoinhibida mediante un proceso lógico CMOS puro

Resumen

Este documento informa sobre una nueva memoria de acceso aleatorio estático no volátil 4T2R compatible con lógica completa (nv-SRAM) que presenta su mecanismo de almacenamiento de datos de autoinhibición para aplicaciones SRAM de baja potencia / alta velocidad. Con un área de celda compacta y compatibilidad lógica total, esta nueva nv-SRAM incorpora dos STI-ReRAM integradas dentro de la 4T SRAM. Los datos se pueden leer / escribir a través de una estructura volátil de pares cruzados para mantener una velocidad de acceso rápida. Los datos se pueden almacenar de forma no volátil en una nueva celda SRAM a través de una operación de autoinhibición única en la carga de la memoria resistiva de acceso aleatorio (RRAM), logrando una potencia estática cero durante la retención de datos.

Antecedentes

En los últimos años, se han desarrollado varias memorias de acceso aleatorio estáticas de baja potencia para satisfacer las necesidades de los sistemas informáticos en dispositivos portátiles y aplicaciones IOT [1, 2, 3, 4, 5, 6]. A medida que la tecnología CMOS se reduce al régimen de nanómetros, la corriente de fuga fuera de estado aumenta drásticamente, lo que conduce a un empeoramiento del consumo de energía estática para los módulos de memoria volátiles [7, 8]. El consumo de energía estática generado por la corriente de fuga en los transistores a nanoescala se ha convertido en uno de los desafíos clave para el avance de las SRAM de baja potencia. [9,10,11]. A lo largo de los años, se han propuesto diferentes estructuras celulares o técnicas de operación [12, 13, 14, 15, 16] para minimizar el consumo de energía en las SRAM. Algunas de las celdas recientemente propuestas incorporan elementos de almacenamiento no volátiles, como la memoria resistiva de acceso aleatorio (RRAM) y la memoria magnetorresistiva de acceso aleatorio (MRAM) [17,18,19,20], para lograr una potencia de retención cero mientras se mantiene un funcionamiento bajo potencia y velocidad de acceso rápido en el procesamiento de datos volátiles. Sin embargo, agregar elementos de almacenamiento no volátiles en matrices SRAM basadas en lógica generalmente requiere capas y / o procesos adicionales a las plataformas lógicas estándar [21, 22, 23]. Esto inevitablemente aumentará la complejidad del proceso para su desarrollo. Además, estas RRAM y MRAM basadas en back-end requieren una gran estructura de conexión, compuesta de varias pilas de vías y metales a las celdas SRAM. Estas estructuras puente aumentan la capacidad parásita del nodo de almacenamiento de datos SRAM, lo que afecta la velocidad de acceso de estas celdas SRAM no volátiles [24, 25]. En nuestro trabajo anterior [26], se propuso en primer lugar una nueva SRAM nv 4T de potencia cero estática con RRAM de pared lateral STI ubicada junto a los nodos de almacenamiento flotante de la SRAM 4T. En esta carta, esta 4T2R nv-SRAM con almacenamiento de datos no volátiles, capacidad de retención cero y velocidad de acceso rápida se analizará y optimizará en mayor profundidad para aplicaciones NVM integradas.

Métodos

Estructura de la celda STI-ReRAM

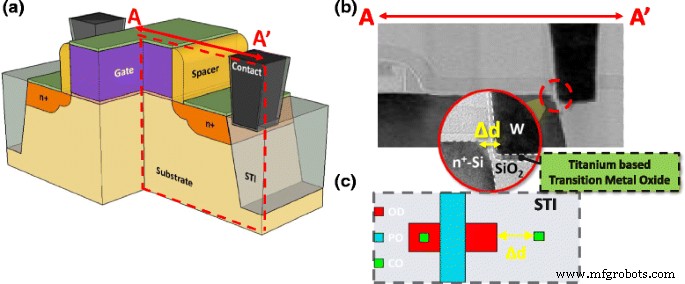

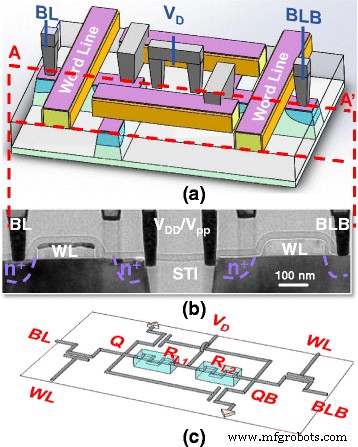

En la estructura 3D STI-RRAM de la figura 1a, el nodo de almacenamiento resistivo está compuesto por un óxido de metal de transición (TMO) entre dos electrodos, la región N + y un tapón de tungsteno en el lado izquierdo y derecho, respectivamente. Como se muestra en la imagen TEM en la Fig. 1b y el diseño en la Fig. 1c, colocando el contacto en la región STI con la distancia adecuada a la región N +, el SiO 2 restante y la capa de barrera debajo del tapón de tungsteno se convierte en película TMO y se presenta con la calidad de conmutación resistiva.

un Ilustración 3D de una celda 1T1R con STI-ReRAM justo al lado de la unión n +. b La imagen TEM correspondiente del nodo de almacenamiento resistivo compuesto de óxidos de metales de transición, formado entre un contacto especialmente colocado y la región n + del transistor seleccionado. c Diseño

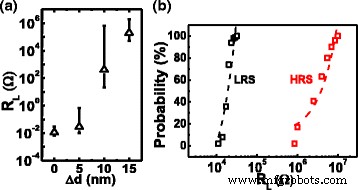

El espesor de TMO se puede controlar eligiendo un espaciado adecuado Δd entre un contacto y la región de difusión N +. Sobre la base de la medición de la figura 2a, existe una correlación positiva entre el nivel de resistencia inicial y la distancia dibujada, Δd, determinada por las máscaras que definen STI y regiones de contacto, respectivamente. Para el siguiente estudio, se elige RRAM con Δd igual a 10 nm por su voltaje de formación más bajo y R L preferible distribución tanto en el estado de baja resistencia (LRS) como en el estado de alta resistencia (HRS) como se resume en la Fig. 2b. Con un control de voltaje de línea de palabras (WL) adecuado durante las operaciones de configuración / formación, el transistor seleccionado puede fijar localmente la corriente configurada, lo que permite mejores rendimientos de resistencia.

un La resistencia inicial medida de muestras STI-RRAM con diferentes △ d. b Probabilidad acumulada de la resistencia de carga después de reiniciar / configurar el STI-RRAM en los estados de alta y baja resistencia

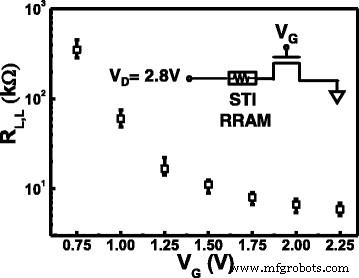

Los datos de la Fig.3 revelan además que el nivel de corriente de lectura en LRS puede controlarse bien mediante el voltaje de la puerta, V G . Durante la formación en V D =2.8 V, el transistor de selección limita la corriente máxima que pasa a través del STI-RRAM después de que el dispositivo se configura en LRS. El nivel de resistencia del estado LRS subsiguiente es inversamente proporcional a la corriente fijada localmente, que se ha encontrado en varios dispositivos RRAM basados en TaO [27, 28].

Correlación entre los niveles de resistencia de carga, R L, L , y el voltaje de puerta aplicado durante el ajuste. Los datos sugieren que diferentes R L, L se puede obtener configurando un nivel diferente de voltaje de puerta seleccionado

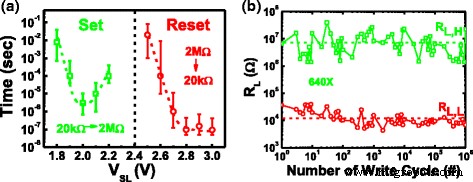

Para asegurar las características de conmutación resistiva de STI-RRAM, se prueban el tiempo de ajuste y el tiempo de reinicio, como se muestra en la Fig. 4a. Las operaciones de configuración y reinicio se pueden optimizar cuando V SL =2 y 2,8 V, respectivamente. La prueba de resistencia RRAM se resume en la Fig. 4b. Mediante el uso de un algoritmo de programación de pulsos de pasos incrementales, su ventana de lectura puede permanecer estable después de 1 millón de ciclos.

un Tiempo resumido de configuración y tiempo de reinicio frente a V PP . b Resultado de la prueba de resistencia de un millón de ciclos del STI-RRAM utilizando el algoritmo de programación de impulsos incrementales

Concepto de SRAM no volátil

La ilustración 3D en la Fig. 5 muestra la estructura celular 4T2R nv-SRAM recientemente propuesta y su correspondiente imagen TEM de sección transversal a lo largo de la línea de corte AA '. Dos STI-RRAM sirven como nodos de almacenamiento no volátiles y como resistencias de carga, que están intercaladas entre las regiones de difusión Q y QB N + y un contacto aterrizado cerca de los bordes STI con un diseño de espaciado adecuado. La imagen TEM muestra una STI-RRAM bien formada tanto en el lado izquierdo como en el derecho de la región de aislamiento y da como resultado una celda bastante compacta con estos nodos de almacenamiento no volátiles colocados de cerca al mismo nivel de los transistores.

un Ilustración 3D de la estructura celular propuesta 4T2R nv-SRAM y el b correspondiente imagen TEM de sección transversal. c El esquema del circuito de una celda SRAM se muestra con dos resistencias RRAM como dispositivos de carga

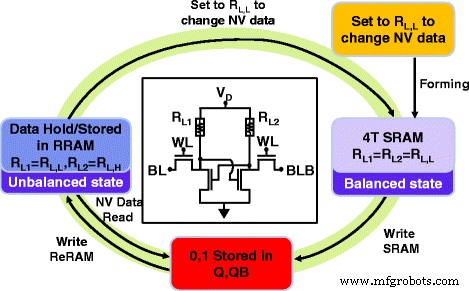

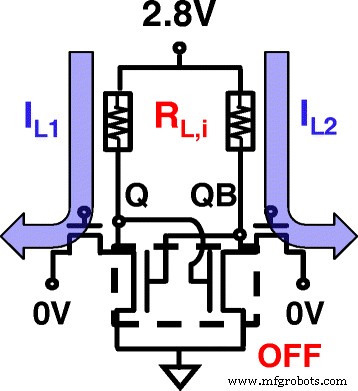

El 4T nv-SRAM propuesto puede funcionar en modos volátiles y no volátiles. Sus cuatro estados diferentes y su esquema de funcionamiento se ilustran en la Fig. 6.

Esquema del circuito de la celda nv-SRAM y su diagrama de flujo correspondiente para cambiar entre operaciones SRAM volátiles y no volátiles

En sus estados iniciales, STI-RRAM normalmente tiene un nivel de resistencia de 10 8 Ω, mientras que la película TMO está intacta. A través de una operación de formación de manta, las celdas nv-SRAM se pueden inicializar simultáneamente en un bloque por bloque en V D =2.8 V. Ambos R L1 y R L2 (resistencia de carga a la izquierda y a la derecha, respectivamente) se inicializan en R L, L . La R L, L final El nivel de 20 ~ 370 kΩ se puede controlar dando diferentes voltajes WL durante la operación de formación. Luego, la celda alcanza un estado de equilibrio, lo que significa que las dos resistencias de carga están en el mismo estado. En este estado, esta celda ahora puede funcionar como la SRAM 4T2R típica, procesando datos volátiles de una manera convencional, almacenando datos en el pestillo de acoplamiento cruzado.

Para almacenar los datos de forma no volátil, los datos bloqueados complementarios se pueden almacenar en las RRAM mediante un mecanismo de autoinhibición heredado en esta celda. Cuando los datos se almacenan con éxito en el par RRAM, se puede apagar la fuente de alimentación para la retención de datos permanente. Para acceder al estado almacenado, simplemente vuelva a aplicar V DD a la matriz. Los datos no volátiles se restaurarán en los nodos Q y QB automáticamente y se puede acceder a ellos a través del modo de lectura SRAM convencional. Finalmente, para actualizar los datos no volátiles, se aplica una operación de conjunto general a las matrices SRAM para que la matriz vuelva a su estado de equilibrio.

Resultados y discusión

Análisis eléctrico

Las condiciones de operación para las transiciones entre diferentes etapas se resumen en la Tabla 1.

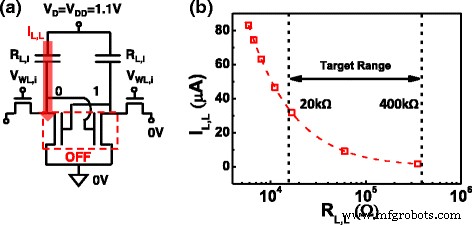

Diferente R L, L El nivel se puede obtener configurando diferentes voltajes WL durante la inicialización de un bloque o matriz. Teniendo en cuenta la estabilidad y el voltaje de funcionamiento, el R L, L El nivel que varía entre 20 y 400 kΩ es el primer objetivo de investigación en este estudio. Correspondiente al voltaje WL de 0,75 a 1,25 V, la resistencia de carga resultante se reduce de forma bastante lineal, como se muestra en la Fig. 3. Como era de esperar, menor R L, L El nivel conducirá a una corriente de espera más alta, vea la Fig. 7. Sin embargo, R L, L debe permanecer lo suficientemente bajo para asegurar una gran ventana de datos ampliada entre los dos estados de resistencia. Es necesario considerar la ventana de datos tanto estáticos, dinámicos como no volátiles para una mayor optimización del R L, L objetivo , que se establece mediante la condición de inicialización.

un Celda 4T2R SRAM en condición de espera. b Como se esperaba, nivel de resistencia de carga, I L, L durante la retención se puede reducir de manera efectiva eligiendo un R L, L más alto

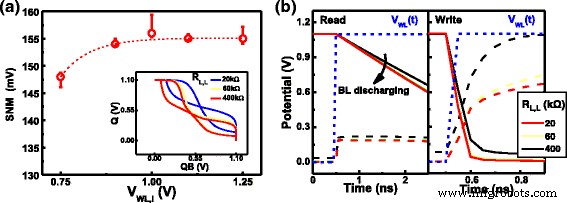

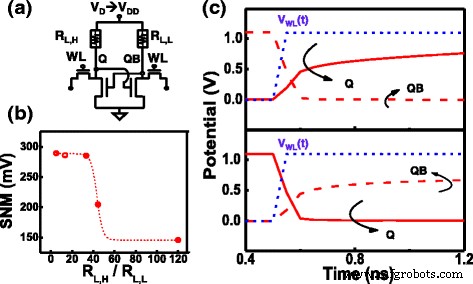

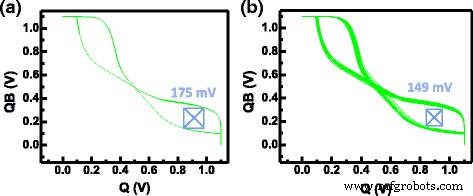

Primero se investiga la caracterización estática y dinámica de la nv-SRAM en el estado de equilibrio, considerando las células inicializadas por diferentes condiciones. En la Fig. 8, el margen de ruido estático (SNM) obtenido por las múltiples curvas de mariposa de celdas inicializadas por diferentes voltajes WL. Los datos revelan que R L, L El nivel tiene un efecto mínimo en el margen de lectura de las celdas balanceadas, cuando las resistencias de carga están dentro del rango objetivo. La distribución SNM de múltiples celdas en los estados de equilibrio bajo diferentes condiciones de inicialización se resume en la Fig. 8a. En general, los SNM permanecen bastante estables de una celda a otra, mientras que se puede establecer un margen de lectura razonable con un voltaje de WL menor que V DD , que puede ser beneficioso para aplicaciones de bajo consumo. Para investigar las características dinámicas de lectura y escritura de esta celda en el estado balanceado, la respuesta transitoria de escribir "1" y "0" se resumen en la Fig. 8b. Se encuentra que mayor R L, L reduce la velocidad de subida a los nodos Q, QB, lo que puede aumentar ligeramente el tiempo transitorio durante las operaciones de lectura y escritura. Sin embargo, la velocidad de respuesta todavía está dentro del rango esperado. Los datos anteriores sugieren que en el estado de equilibrio, este 4T2R nv-SRAM puede procesar datos volátiles como SRAM convencionales.

un El margen de ruido estático de lectura (SNM) de las celdas SRAM propuestas con diferente voltaje WL durante la inicialización. Se puede mantener un SNM razonable dentro de un rango bastante grande de R L, L de 20 ~ 400 kΩ. b Las características dinámicas de lectura y escritura de una celda en condiciones de carga equilibrada revelan un buen tiempo de respuesta en nanosegundos. Mayor R L, L reduce ligeramente la velocidad de pull-up durante la operación de escritura

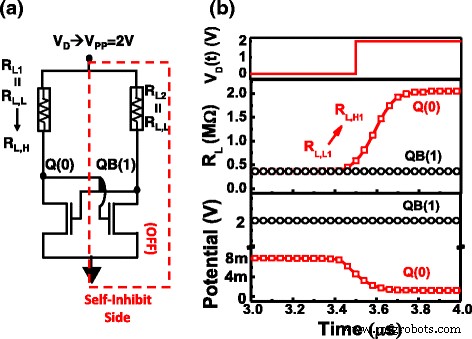

Para almacenar datos en el par STI-RRAM, esta celda permite un reinicio auto-selectivo de solo uno de los RRAM en el par de resistencias de carga, lo que permite que los datos se escriban de forma no volátil aplicando un V pp voltaje al nodo de suministro al bloque de celdas de manera uniforme. Una vez que los datos de enclavamiento se almacenan en el nodo Q y QB, la escritura no volátil se logra mediante el mecanismo de autoinhibición en la estructura de acoplamiento cruzado con RRAM, como se muestra en la Fig. 9a. Solo un lado de RRAM con bajo voltaje en el nodo Q se restablecerá a R L, H . La corriente en la otra rama es casi cero ya que el transistor desplegable se apaga por el bajo V Q .

un Ilustración del mecanismo de autoinhibición durante la escritura de datos no volátiles restableciendo un lado de dos RRAM. b Cambio dinámico de R L y Q, QB potencial verificar la escritura autoinhibida de datos de pestillo en RRAM

Los datos se almacenan en el par RRAM como V PP se aplica pulso al nodo de suministro. Al escribir datos no volátiles, el cambio dinámico de R L y la respuesta transitoria del potencial Q, QB se resumen en la Fig. 9b. Los datos de medición sugirieron que para restablecer con éxito el STI-RRAM selectivamente en un lado, un pulso de 300 ns en V pp =2 V es suficiente. Para garantizar que la operación volátil aún no se vea afectada cuando las celdas están en el estado desequilibrado como la Fig. 10a, la distribución SNM de las celdas con diferentes R L, H / R L, L relación se resumen en la Fig. 10b. Se encuentra que la relación de baja resistencia entre los estados no degrada el SNM de retención. Para garantizar que una celda con una carga desequilibrada, se caracterice la escritura dinámica de datos en dicha celda. Los datos revelan que ambos estados se pueden escribir con éxito, superando la relación de resistencia al desequilibrio inicial de 2 M / 400 k, como se muestra en la Fig. 10c.

un Estructura de pares cruzados durante la carga de desequilibrio. b Margen de ruido estático con diferentes voltajes WL durante la inicialización. c Escritura dinámica para dos estados de datos diferentes. Desequilibrio R L, L =400 kΩ también se pueden escribir

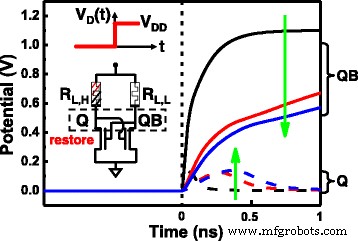

Para volver a cargar los datos volátiles almacenados previamente en RRAM, simplemente se puede aplicar V DD al nodo de la fuente de alimentación, la carga de desequilibrio en las RRAM se restaurará automáticamente a los nodos de enclavamiento de Q y QB, como se ilustra en la Fig. 11.

Restauración de los datos no volátiles almacenados en Q y QB desde un estado de carga de RRAM desequilibrado. El potencial de los nodos Q y QB se puede restaurar después del retorno de la energía en nanosegundos

Efecto parasitario y comparación

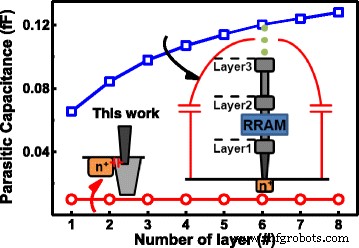

Al incorporar la STI-RRAM totalmente compatible con la lógica en esta nueva celda SRAM, esta celda se puede implementar fácilmente mediante la mayoría de los procesos lógicos estándar sin agregar capas de enmascaramiento ni pasos de proceso. Esta característica puede mejorar enormemente sus aplicaciones y flexibilidad en varios módulos IP de memoria no volátil necesarios en muchos sistemas de CI. Además, el 4T2R nv-SRAM propuesto presenta una capacitancia parásita mucho menor en comparación con otros nv-SRAMs reportados previamente [29,30,31] que requieren componentes no volátiles de back-end-of-line (BEOL). Para conectar el nodo Q y QB desde la superficie de Si a estos BEOL RRAM o MRAM, se necesitan múltiples pilas de metal y capas de vía. Estas grandes estructuras de puente conducen a un efecto RC parasitario significativo. La gran capacitancia parásita introducida en los nodos internos dentro de las celdas SRAM puede afectar críticamente el tiempo de respuesta de los dispositivos.

Para comparar el efecto parásito sobre estos, se investigan nv-SRAM en función de la estimación de la simulación posterior al diseño. Suponiendo que todas las celdas se implementan con la misma tecnología CMOS estándar, la capacitancia parásita en los nodos de pestillo aumenta a medida que aumenta el número de capas de metal para las celdas que necesitan grandes estructuras de puente. Para el nuevo nv-SRAM que usa STI-RRAM, hay muy poco aumento en la capacitancia general en los nodos bloqueados. Además, es independiente del número de capas metálicas adaptadas en un circuito particular. Para investigar más a fondo el efecto de la capacitancia parásita de la velocidad SRAM, la respuesta dinámica simulada de las celdas SRAM propuestas en [29,30,31] y este trabajo se comparan en la Fig. 12.

Capacitancia parásita en los nodos de retención de las celdas nv-SRAM de la ref [30] y que a partir de este trabajo basado en tecnología CMOS de 40 nm, se encuentra un aumento significativo en la capacitancia parásita a medida que aumenta el número de capas metálicas

Una capacitancia parásita mucho menor de este nv-SRAM integrado puede conducir a un tiempo de respuesta más rápido durante la operación de lectura dinámica en la celda SRAM. Esto evita que la gran capacitancia interna del puente de conexión afecte el tiempo de respuesta de la matriz SRAM basada en lógica.

La Tabla 2 compara las características clave de las SRAM no volátiles informadas anteriormente incorporadas con las RRAM o MRAM de back-end y este trabajo. A pesar del voltaje de conmutación de estado más alto, el nv-SRAM basado en STI-RRAM se presenta con una capacitancia parásita mucho más pequeña en los nodos retenidos internos dentro de las celdas SRAM y compatibilidad lógica total.

Degradación del margen de ruido estático inducida por variación

Para garantizar el SNM estable con celdas sujetas a variaciones de proceso, fluctuaciones en los niveles de resistencia RRAM y en el voltaje umbral del transistor, V T , se consideran en las siguientes investigaciones:desajustes en V T se sabe que provoca un cambio de SNM en SRAM mediante tecnologías escaladas [32, 33]. Además, también puede causar una corriente de cumplimiento de conjunto diferente, lo que a su vez puede resultar en una mayor variación en el nivel de resistencia de los dos R L, L . Como se ilustra en la Fig.13, diferentes V T conducir a una corriente de cumplimiento de inicialización diferente en la celda STI-RRAM, lo que lleva a un mayor desajuste en R L, L . Analizar el impacto de V T variación en SNM, asumimos V T para ser una variable aleatoria gaussiana con media y variación basada en informes anteriores [34]. Por simulación de Monte-Carlo, la distribución de curvas de mariposa sujetas a variaciones en R L, L se resumen en la Fig. 14a. Cuando ambas variaciones en R L, L y VT, se observa un estrechamiento significativo de la ventana SNM, como se muestra en la Fig. 14b. La mayor variabilidad en el nv-SRAM debe abordarse en los estudios futuros.

V T la variación conduce a un cumplimiento de inicialización diferente I L, 1 y yo L, 2

Curvas de mariposa mediante simulaciones de Montecarlo que comparan las degradaciones de SNM causadas por a variación en R L, L después de la inicialización y b variaciones en R L, L y V T

Conclusiones

Se ha demostrado con éxito una nueva SRAM no volátil basada en STI-RRAM 4T2R totalmente compatible con el proceso lógico CMOS en un proceso lógico CMOS puro en un nodo de tecnología de 40 nm sin máscaras ni pasos adicionales. Esta celda nv-SRAM presenta un mecanismo de autoinhibición y auto-restauración para datos no volátiles, pequeña capacitancia parásita en los nodos de cierre y cero energía estática durante la retención de datos. Estas características superiores hacen que nv-SRAM basada en STI-RRAM sea una solución prometedora para aplicaciones de memoria no volátil lógica de baja potencia / alta velocidad en el futuro.

Nanomateriales

- Introducción a los circuitos integrados digitales

- Circuitos integrados

- Lógica digital con comentarios

- Circuitos de conmutación de diodos

- Energía en circuitos de CA resistivos y reactivos

- Corrección práctica del factor de potencia

- Modelo de retención de TaO / HfO x y TaO / AlO x RRAM con características de interruptor autorrectificante

- Características de conmutación resistiva bipolar de dispositivos RRAM con estructura de tres capas de HfO2 / TiO2 / HfO2 en sustratos recubiertos de Pt y TiN fabricados por deposición de capa atóm…

- Memoria resistiva ZrO2 / ZrO2 - x / ZrO2 sin cumplimiento con comportamiento de conmutación multiestado interfacial controlable

- Mecanismo de conducción y resistencia mejorada en RRAM basado en HfO2 con tratamiento de nitruración

- Estudio del efecto de la dirección de impacto en el proceso de corte nanométrico abrasivo con dinámica molecular