Dispositivo LVTSCR robusto e inmune a enganches con un PMOSFET integrado para protección ESD en un proceso CMOS de 28 nm

Resumen

Se espera que el rectificador controlado por silicio activado por bajo voltaje (LVTSCR) proporcione una protección contra descargas electrostáticas (ESD) para un circuito integrado de bajo voltaje. Sin embargo, normalmente es vulnerable al efecto de enganche debido a su voltaje de retención extremadamente bajo. En este artículo, se ha propuesto y verificado un nuevo LVTSCR integrado con un MOSFET de tipo p adicional llamado EP-LVTSCR en una tecnología CMOS de 28 nm. El dispositivo propuesto posee un voltaje de activación más bajo de ~ 6.2 V y un voltaje de retención significativamente más alto de ~ 5.5 V con solo un 23% de degradación de la corriente de falla bajo la prueba de pulso de la línea de transmisión. También se muestra que el EP-LVTSCR funciona con una resistencia de encendido más baja de ~ 1.8 Ω, así como una corriente de fuga confiable de ~ 1.8 nA medida a 3.63 V, lo que lo hace adecuado para protecciones ESD en CMOS de 2.5 V / 3.3 V Procesos. Además, el mecanismo de activación y las características de conducción del dispositivo propuesto se exploraron y demostraron con la simulación TCAD.

Antecedentes

Con la miniaturización continua del tamaño de las características de los dispositivos semiconductores, el daño inducido por la descarga electrostática (ESD) en los circuitos integrados (IC) se ha convertido en un problema más serio. Además, el costo de fabricación del dispositivo de protección ESD se ha incrementado considerablemente debido a la tecnología de proceso avanzada [1]. Por lo tanto, los diseños de dispositivos de protección ESD de alta eficiencia y robustez de área son de gran valor.

Se verificó que un dispositivo rectificador controlado por silicio (SCR) sostenía una alta corriente ESD con una dimensión de dispositivo pequeña debido al fuerte efecto de retroalimentación positiva en sus transistores de unión bipolar parásitos [2]. Pero el SCR generalmente tiene un voltaje de activación alto ( V t1 ) que excede el voltaje de ruptura del óxido de puerta de la etapa de entrada en la tecnología CMOS a nanoescala. Para reducir la V t1 de SCR, se informó el SCR lateral modificado (MLSCR) para la protección ESD de entrada insertando n + muy dopado o p + regiones a través del límite de n-well y p-well [3, 4]. Pero el voltaje de activación del MLSCR es aún mayor que los voltajes de ruptura de los transistores de salida en el búfer de salida CMOS. Por lo tanto, no puede proporcionar una protección ESD de salida eficiente solo.

Para proteger eficientemente el búfer de salida CMOS, se ha propuesto un SCR activado por bajo voltaje (LVTSCR) insertando un dispositivo NMOS de canal corto (PMOS) en el SCR tradicional para obtener un voltaje de disparo mucho más bajo [5,6,7] , que es equivalente al voltaje del disparador snapback del dispositivo NMOS (PMOS) insertado. Sin embargo, al igual que los dispositivos tradicionales SCR y MLSCR, el LVTSCR también sufre los peligros de enganche debido a su voltaje de retención extremadamente bajo (V h ) de aproximadamente 2 V [8]. Tal efecto de enganche resultará en un mal funcionamiento durante el funcionamiento normal y una corriente alta incesante para destruir el CI [9].

Hay varios métodos posibles para mejorar la V h del LVTSCR [10,11,12,13,14,15]. La solución más común es expandir la región base de los transistores de unión bipolar parásitos (BJT) del SCR para disminuir la eficiencia de inyección de sus uniones emisor-base [10]. Al adoptar esta solución, no solo aumentará el área de diseño del dispositivo, sino también la resistencia de encendido ( R en ) debería, también, lo que conducirá a una degradación drástica de su corriente de falla ( I t2 ). Luego, se propuso un método optimizado insertando una región flotante-n-well en LVTSCR con menos sacrificio en I t2 [11], pero también funciona con una gran R en conduciendo un voltaje de conducción exorbitante que excede el voltaje de ruptura del óxido de la puerta contra una pequeña corriente, reduciendo así su corriente de protección ESD efectiva. El método de agregar las capas N-LDD / P-HALO adicionales en LVTSCR también puede elevar el V h [12], mientras que estos dispositivos solo son compatibles para el proceso específico y no pueden usarse ampliamente en los procesos CMOS ordinarios. Además, en [13] se informó un LVTSCR activado por NMOS de puerta a tierra (GGSCR), lo que aumenta el V h conduciendo el drenaje del NMOS incorporado al ánodo, pero podría causar que el NMOS incorporado se dañe antes de la conducción SCR en una corriente baja. Recientemente, las estructuras de LVTSCR compuestas con bajo rendimiento de V t1 así como alto V h se demostraron en [14, 15]. Estas estructuras compuestas están diseñadas con requisitos de área y alta complejidad, lo que limita su aplicación en tecnología CMOS avanzada considerando los costos de diseño. Por lo tanto, un dispositivo de protección ESD robusto, eficiente en el área e inmune a enganches es altamente deseable en la protección ESD de procesos avanzados.

En este artículo, se propone una estructura LVTSCR novedosa con un transistor PMOS integrado (EP-LVTSCR) para aplicaciones de voltaje de suministro de 2,5 V / 3,3 V. El dispositivo propuesto se fabricó en un proceso CMOS de 28 nm y su característica eléctrica se verifica mediante la medición del pulso de la línea de transmisión (TLP). Los mecanismos físicos del dispositivo propuesto se exploran mediante simulaciones de tecnología de diseño asistido por computadora (TCAD). Como resultado, la estructura propuesta posee un voltaje de retención más alto, un voltaje de disparo más bajo con un R más bajo. en y solo una ligera disminución en I t2 sin ningún paso de proceso adicional.

Métodos

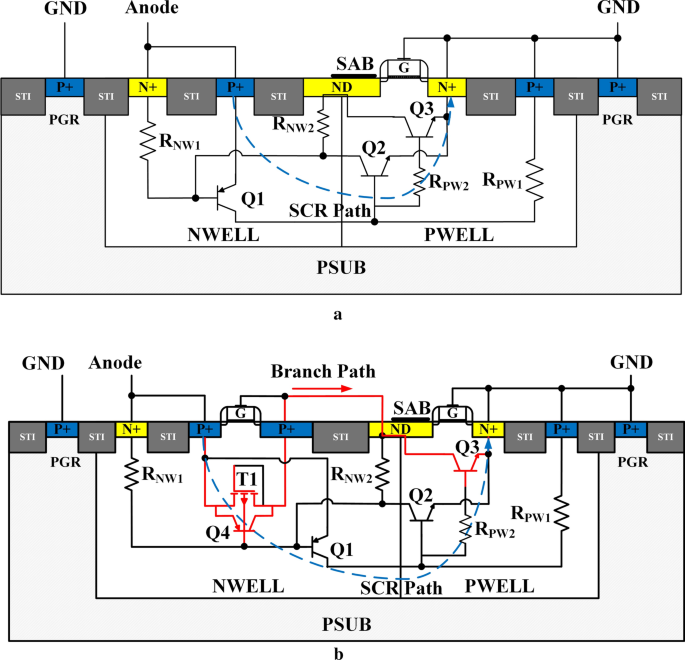

En este artículo se han estudiado el LVTSCR convencional y el EP-LVTSCR propuesto. Las vistas esquemáticas en sección transversal del LVTSCR y EP-LVTSCR convencionales se muestran en la Fig. 1a, b, respectivamente, mientras que sus circuitos equivalentes se muestran dentro de las estructuras con los transistores parásitos y las resistencias de pozo. En ambos dispositivos, las capas de bloques de siliciuro (SAB) se colocan en la parte superior de la región ND parcial que inducirá resistencias de lastre evitando la formación de capas de siliciuro [16, 17]. En LVTSCR convencional, un transistor NMOS se inserta en PWELL con su configuración de drenaje (ND) a través de NWELL y PWELL, mientras que su fuente y compuerta están conectadas a tierra (GND) juntas, lo que se puede ver en la Fig. 1a. Durante el estrés ESD, el BJT lateral parasitario p-n-p (Q1) y el BJT lateral parasitario n-p-n (Q2 y Q3) se encenderán gradualmente. En tal condición, los transistores Q1 y Q2 están acoplados para constituir la ruta de conducción SCR que predominará en la descarga de corriente, donde la ruta de conducción SCR está indicada por la línea discontinua.

Vista transversal de a el LVTSCR convencional y b el EP-LVTSCR propuesto

Comparado con el LVTSCR convencional, EP-LVTSCR tiene un transistor PMOS adicional (T1) incrustado en el NWELL ya que su puerta y drenaje están conectados a ND con un metal, que se muestra en la Fig. 1b. Cuando se aplica un pulso ESD al ánodo del EP-LVTSCR, el diodo N + / NWELL / N + / PWELL / P + con polarización inversa conducirá primero si el voltaje de zapping es mayor que el voltaje de ruptura N + / PWELL. Luego, los huecos / electrones generados por el efecto multiplicador de avalancha fluirán hacia el cátodo / ánodo, lo que aumentará la densidad de corriente en NWELL / PWELL y elevará aún más el potencial de caída a través de NWELL / PWELL. Una vez que la caída de voltaje total en R NW1 y R NW2 , que es equivalente a la caída de voltaje entre la fuente y la puerta (- V gs ) de T1, supera su voltaje umbral ( V th ) de aproximadamente 0,9 V, el T1 se encenderá. Posteriormente, los transistores laterales parásitos n – p – n Q2 y Q3 se activarán dependiendo de la conducción de sus uniones emisor-base. Se nota que la conducción de T1 bajará el R en a través de NWELL y, por lo tanto, Q2 y Q3 pueden activarse en voltajes más bajos. A medida que la corriente continúa aumentando, la caída de voltaje en R NW1 se eleva a aproximadamente 0,7 V y enciende el Q1 y el transistor lateral parasitario p – n – p del PMOS (Q4). Finalmente, la ruta SCR se enciende contra la ruta de derivación que conduce.

Varios informes demostraron que el voltaje de mantenimiento de SCR está determinado principalmente por la diferencia de potencial en la región de agotamiento de NWELL / PWELL V dep [18,19,20], que es inversamente proporcional a los portadores minoritarios (electrones / huecos) inyectados en la región de agotamiento. Mientras que la ruta de ramificación de EP-LVTSCR puede extraer huecos / electrones inyectados en la región de agotamiento de la ruta de SCR, elevando así el V h de EP-LVTSCR.

Con el fin de demostrar aún más el mecanismo físico de EP-LVTSCR, se ha realizado la simulación TCAD, donde se integraron los modelos físicos como movilidad, recombinación, termodinámica y densidad intrínseca efectiva y los métodos matemáticos como extrapolar, RelErrcontrol y corriente continua. se utilizaron cálculos. El modelado de corriente ESD por pulsos de 1,2 A con un tiempo de aumento de 10 ns se aplicó a los ánodos de EP-LVTSCR y LVTSCR convencional, respectivamente, donde el sustrato de los dispositivos se consideró como el único disipador de calor y la temperatura ambiente se estableció en 300 K.

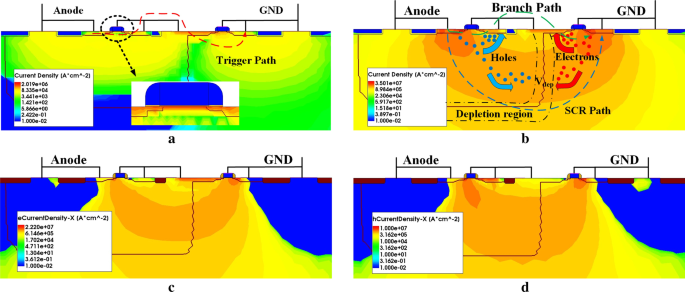

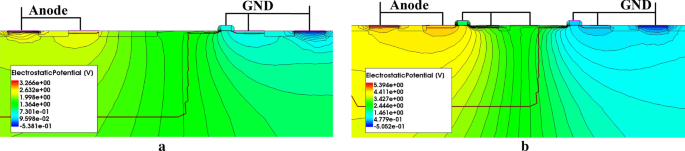

Los resultados simulados de las distribuciones de densidad de corriente total de EP-LVTSCR a 500 ps y 5 ns se muestran en la Fig. 2a, b, respectivamente. A 500 ps, la distribución de la densidad de corriente se concentra en los transistores T1 y Q2, lo que indica que las series T1 / Q2 se han encendido como una ruta de activación que se muestra en la Fig. 2a. Cuando el tiempo aumenta a 5 ns, tanto la ruta SCR como la ruta de bifurcación han conducido como se puede observar en la Fig. 2b. En este momento, parte de los huecos / electrones generados por P + / N + se extraen de NWELL / PWELL para fluir a través de la ruta de ramificación, que se ilustra mediante los huecos horizontales y la densidad de corriente de electrones de la estructura propuesta que se muestra en la Fig. 2c, d . Además, las distribuciones de potencial electrostático del LVTSCR y EP-LVTSCR convencionales a 5 ns se comparan en la Fig. 3a, b. Obviamente, el pico potencial dentro del EP-LVTSCR es mayor. Estos resultados de simulación proporcionan evidencia directa de la suposición anterior de que el voltaje de retención más alto de EP-LVTSCR resultó de la ruta de bifurcación indicada en la Fig. 1b.

a simulado por TCAD distribución de la densidad de corriente total en t =500 ps, b distribución de la densidad de corriente total a 5 ns, c Distribución horizontal de la densidad de corriente de electrones a 5 ns y d Distribución de densidad de corriente de agujeros horizontales a 5 ns del EP-LVTSCR propuesto bajo una tensión 1.2A-TLP

Distribuciones de potencial electrostático simuladas por TCAD de a la propuesta EP-LVTSCR y b el LVTSCR convencional en t =5 ns bajo un estrés 1.2A-TLP

Resultados y discusión

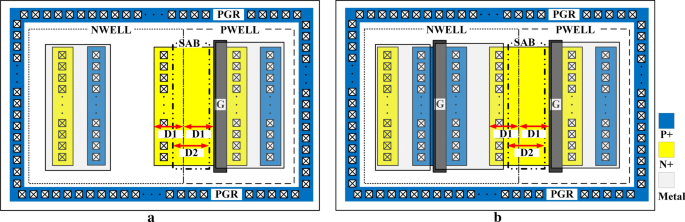

El LVTSCR y el EP-LVTSCR convencionales se implementan en un proceso CMOS lógico de 28 nm de 2,5 V / 3,3 V con el mismo ancho de 40 um, y sus topologías de diseño se muestran en las Fig. 4a, b, respectivamente. Para evitar los efectos parásitos asociados con el sustrato, se emplean anillos de protección tipo P (PGR) en ambas estructuras, y cada PGR está conectado a GND [21]. El eje central de ND está alineado con la unión NWELL / PWELL, y el parámetro D1 se usa para describir la mitad de la longitud ND, mientras que D2 es la longitud de la región SAB.

Topologías de diseño de a el LVTSCR convencional y b el EP-LVTSCR propuesto

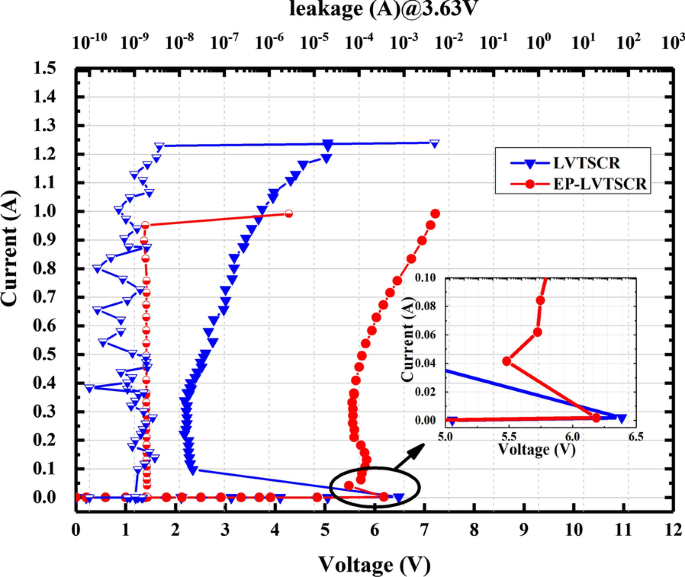

Las características ESD del LVTSCR y EP-LVTSCR convencionales se midieron usando el probador Hanwa TED-T5000 TLP con un tiempo de subida de 10 ns y un ancho de pulso de 100 ns, y las corrientes de fuga se midieron por debajo de 3.63 V (1.1 * VDD) de voltaje de CC después de cada polarización. Estrés TLP. El TLP I – V medido y las características de fuga del EP-LVTSCR y LVTSCR se muestran en la Fig. 5. Aparentemente, el EP-LVTSCR posee un V más alto h de 5,49 V en comparación con el LVTSCR convencional de 2,18 V. Aunque el EP-LVTSCR tiene una mejora significativa en el voltaje de mantenimiento, su I t2 simplemente disminuyó en aproximadamente 0.29 A, lo que se beneficia del asistente de la ruta de la corriente de la rama. Además, EP-LVTSCR también realiza una V t1 disminuyendo de 6,49 a 6,18 V. Para el pin IO de 2,5 V o 3,3 V en procesos CMOS de 28 nm, la ventana de diseño de ESD osciló entre 3,63 y 9,4 V con un margen de seguridad del 10%. Por lo tanto, el EP-LVTSCR propuesto se puede utilizar como una solución de protección ESD válida para puertos IO de 2,5 V / 3,3 V superando el problema de enclavamiento en una estructura de tipo LVTSCR tradicional.

TLP I – V medido y corrientes de fuga de EP-LVTSCR y LVTSCR convencional con la misma área de matriz

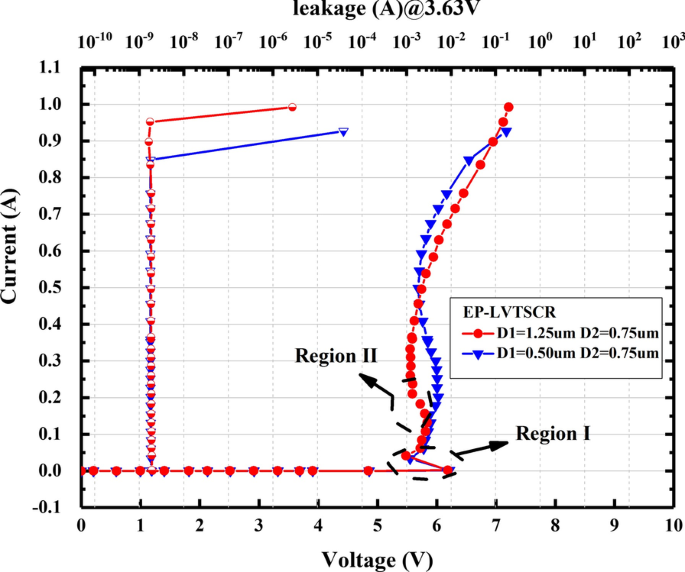

En este artículo se optimizaron las características eléctricas de la protección ESD propuesta modificando las variables de diseño D1 y D2. La Figura 6 ilustra los resultados de la medición de TLP de EP-LVTSCR con dos D1 diferentes. Se observa que las curvas I – V de los EP-LVTSCR muestran dos regiones de retroceso debido a los efectos de activación múltiple durante el encendido de los dispositivos. La primera región I de retroceso sugiere la conducción de la trayectoria del disparador que se indica en la Fig. 2a, mientras que la segunda región II de retroceso es inducida por la activación de la trayectoria de SCR. Cuando D1 disminuye de 1,25 a 0,5 um, el I t2 disminuye en aproximadamente 0,1 A y la corriente de retención en el segundo snapback aumenta en aproximadamente 0,17 A. Esto se debe a que las resistencias del pozo R NW2 y R PW2 (Fig. 1) disminuyen con la disminución de D1, por lo que se requiere más corriente para activar y mantener la conducción de SCR.

TLP I – V medido y corrientes de fuga de EP-LVTSCR con dos D1 diferentes

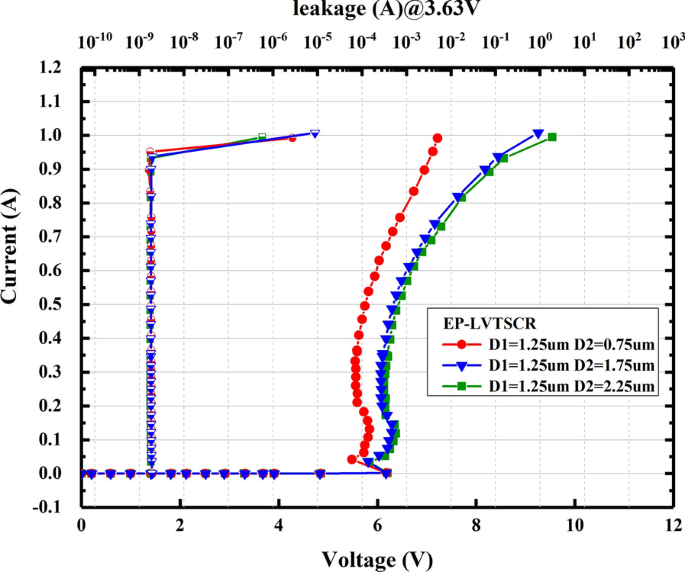

La Figura 7 muestra los resultados de TLP I – V de EP-LVTSCR con tres D2 diferentes. Cuando D2 aumenta de 0,75 a 2,25 µm, la resistencia de lastre de ND aumentó gradualmente, lo que resultó en un aumento de la resistencia de la vía de bifurcación y una mayor ampliación en R en , que se puede observar por las variaciones de pendiente de las curvas características IV en la Fig. 7. Como resultado, la V h se eleva de 5,5 a 5,8 V con el aumento de D2 y sin cambios significativos en I t2 .

TLP I – V medido y corrientes de fuga de EP-LVTSCR con tres D2 diferentes

Conclusiones

Se ha diseñado y fabricado un dispositivo ESD mejorado llamado EP-LVTSCR en una tecnología CMOS de 28 nm. Los mecanismos de los dispositivos propuestos también se demostraron con simulaciones TCAD. Comparado con el LVTSCR convencional, el EP-LVTSCR propuesto posee un voltaje de disparo más bajo de 6.2 V y un voltaje de retención significativamente mayor de 5.5 V debido a su mecanismo de disparo mejorado y efecto de conducción de rama. Con un aumento tan alto en V h , la corriente de falla del EP-LVTSCR solo disminuyó en aproximadamente un 20%. Además, la estructura propuesta opera con una resistencia de encendido más baja, así como una corriente de fuga confiable de aproximadamente 2 nA a un voltaje de 3.63 V, por lo que es altamente aplicable para proteger los pines de E / S de 2.5 V / 3.3 V. Además, también se espera que los EP-LVTSCR proporcionen protección ESD en circuitos de alimentación de 5 V con el beneficio de sus características de voltaje de retención ajustable.

Disponibilidad de datos y materiales

Todos los datos generados o analizados durante este estudio se incluyen en este artículo publicado.

Abreviaturas

- ESD:

-

Descarga electrostática

- SCR:

-

Rectificador controlado por silicio

- MLSCR:

-

SCR lateral modificado

- LVTSCR:

-

SCR activado por bajo voltaje

- CMOS:

-

Semiconductor de óxido de metal complementario

- IC:

-

Circuitos integrados

- V t1 :

-

Voltaje de disparo

- V h :

-

Tensión de retención

- BJT:

-

Transistores de unión bipolar

- R en :

-

Resistencia de encendido

- I t2 :

-

Fallo actual

- TLP:

-

Pulso de línea de transmisión

- TCAD:

-

Tecnología de diseño asistido por computadora

- SAB:

-

Bloque de siliciuro

- V th :

-

Voltaje umbral

- DC:

-

Corriente continua

Nanomateriales

- Un resumen sobre la tecnología IC para microcontroladores y sistemas integrados

- Maxim:transceptor IO-Link dual con regulador DC-DC y protección contra sobretensiones

- Diseño embebido con FPGAs:Proceso de desarrollo

- TRS-STAR:sistemas integrados robustos y sin ventilador de un valor

- Ingeniería del proceso de recubrimiento por inmersión y optimización del rendimiento para dispositivos electrocrómicos de tres estados

- Una SRAM 4T integrada de RRAM con carga de conmutación resistiva autoinhibida mediante un proceso lógico CMOS puro

- Una nueva microestructura de racimo de nanoconas con propiedades antirreflectantes y superhidrofóbicas para dispositivos fotovoltaicos

- Dispositivo multifuncional con funciones conmutables de absorción y conversión de polarización en el rango de terahercios

- RRAM basado en HfAlOx depositado en capa atómica con bajo voltaje de funcionamiento para aplicaciones informáticas en memoria

- Automatización y ciberseguridad:protección completa para los clientes

- Materiales y diseño de PCB para alta tensión