Conmutación analógica y comportamiento sináptico artificial de Ag / SiOx:Ag / TiOx / p ++ - Dispositivo de memristor Si

Resumen

En este estudio, insertando una capa intermedia de TiO x entre el SiO x :Capa de Ag y el electrodo inferior, hemos desarrollado un dispositivo de memristor con una estructura simple de Ag / SiO x :Ag / TiO x / p ++ -Si mediante un proceso físico de deposición de vapor, en el que el crecimiento y la ruptura del filamento se pueden controlar de manera eficiente durante la conmutación analógica. Las características sinápticas del dispositivo de memristor con un amplio rango de cambio de resistencia para la modulación de peso mediante la implementación de trenes de pulsos positivos o negativos se han investigado ampliamente. Se han logrado varias funciones de aprendizaje y memoria simultáneamente, incluida la potenciación / depresión, la facilitación de pulsos emparejados (PPF), la plasticidad a corto plazo (STP) y la transición de STP a LTP (plasticidad a largo plazo) controlada por pulsos repetidos más que una operación de ensayo, y también la plasticidad dependiente del tiempo de picos (STDP). Sobre la base del análisis de las características logarítmicas I-V, se ha descubierto que la evolución / disolución controlada de los filamentos de Ag conductores a través de las capas dieléctricas puede mejorar el rendimiento del dispositivo de memristor de prueba.

Introducción

En 2008, el concepto teórico de memristor [1] del Prof. Chua se convirtió en una realidad cuando Strukov et al. publicaron sus estudios sobre la relación entre el flujo magnético y la carga en un TiO 2 -basado en dos dispositivos terminales compactos por primera vez [2], lo que ha despertado el interés de investigadores de todo el mundo. Además de varias aplicaciones potenciales que van desde operaciones lógicas y sistemas de radiofrecuencia reconfigurables hasta aplicaciones de memoria no volátil [2, 3, 4], los memristores también se han investigado para emular las funciones biosinápticas debido a su estructura y dinámica de trabajo similares. Hoy en día, está ampliamente aceptado que la emulación directa de funciones sinápticas en un dispositivo electrónico es crucial para el desarrollo de sistemas informáticos neuromórficos inspirados en el cerebro [5,6,7]. Sin embargo, las sinapsis electrónicas de diseño tradicional se basan en tecnologías complementarias de semiconductores de óxido de metal (CMOS), que están sufriendo el efecto de cuello de botella de von Neumann en cuanto al complicado proceso de ejecución de la computación, los límites de la densidad de integración y la disipación de energía. Por lo tanto, el uso de un dispositivo ajustable de dos terminales ha infundido muchas oportunidades prometedoras para desarrollar nuevas estructuras para sinapsis electrónicas, que son el resultado de las propiedades únicas de los memristores con característica no volátil, tamaño de nanoescala, bajo consumo de energía, respuesta más rápida, etc. . [8, 9].

Recientemente, varios materiales (p. Ej., Óxidos metálicos como ZnO 2 , WO x , SnO x [10, 11], calcogenuros como Cu 2 S, Ag 2 S [12, 13] y materiales ferroeléctricos como La 2 O 3 , Pb 0.8 Ba 0.2 ZrO 3 [14, 15]) han sido investigados para el diseño y fabricación de dispositivos memristor. Para muchos dispositivos, el cambio en la resistencia se atribuye a la migración inducida por el campo de las vacantes de oxígeno o iones metálicos (p. Ej., Ag + , Cu 2+ y Al 3+ ) y la formación de un camino altamente conductor. La ruta conductora en los memristores generalmente se denomina "filamento conductor (CF)", que posteriormente podría romperse durante una operación de conmutación. En general, se han observado dos tipos de comportamientos de conmutación en memristores, es decir, abruptos (conmutación digital) y graduales (conmutación analógica). El cambio brusco de resistencia es consistente con la señal digital (0 o 1), lo que es beneficioso para el almacenamiento de información [16, 17].

En contraste con la conmutación digital, la sintonización de la conductancia continua en los memristores guarda algunas similitudes con una sinapsis biológica, que es la unidad celular básica para las funciones de aprendizaje y memoria en el cerebro humano [18]. En varios dispositivos de memristor, se han realizado los cambios de conductancia analógica utilizados para emular la modulación de peso de las sinapsis biológicas [19, 20]. Ag difusivo en a-Si y memristores a base de óxido con Pt / a-Si:Ag / Pt y Pt / SiO x N y :Las estructuras Ag / Pt han imitado con éxito el Ca 2+ o Na + dinámica en bio-sinapsis [21, 22]. De manera similar, también se han propuesto iones de oxígeno / filamentos vacantes en memristores a base de óxido metálico para realizar funciones sinápticas, incluida la potenciación a corto plazo (STP) y la facilitación de pulsos emparejados (PPF) [23, 24]. Sin embargo, las reglas de aprendizaje biológico son diversas y, hasta ahora, no todas las funciones sinápticas han estado involucradas en los modelos de memristor [16].

Además de la selección de materiales, el control del crecimiento y ruptura del filamento mediante la inserción de una capa dieléctrica adicional en la estructura “metal / capa memristiva / metal” ofrece ciertas ventajas para emular funciones sinápticas, incluidas STP y LTP, así como un bajo consumo de energía. Recientemente, para controlar la tasa de formación / ruptura de filamentos conductores, Wang et al. [25] han demostrado el comportamiento de conmutación analógica insertando un SiO 2 capa en un TaO x memristor basado en. Wan y col. [26] también se dieron cuenta de la conmutación analógica y emularon las funciones STP y STDP insertando una capa de óxido de grafeno reducida en la estructura de Ag / SrTiO 3 / Memristor FTO para controlar el crecimiento excesivo del filamento Ag. Además, se ha informado [27, 28] que, basándose en el conocimiento de TiO x material con una constante dieléctrica alta (~ 40) y un intervalo de banda bajo (~ 3 eV), el rendimiento del dispositivo de memristor en términos de resistencia y uniformidad del ciclo se ha mejorado notablemente mediante la inserción de un TiO 2 capa fina con HfO 2 capa memristiva. Aparte de esto, se ha informado [24] que debido a la baja movilidad iónica y la baja velocidad de reacción redox, el TiO x La película delgada también puede actuar como una capa amortiguadora para evitar el crecimiento excesivo del filamento conductor, lo que permite un mejor comportamiento sináptico y mantiene un buen contacto del filamento conductor durante los procesos de conmutación resistiva.

En este artículo, informamos una nueva estructura de Ag / SiO x :Ag / TiO x / p ++ -Dispositivos de memristor Si y sus comportamientos de conmutación analógica. En comparación con un dispositivo de una sola capa que se informó anteriormente [22, 29], se ha encontrado que la inserción de un TiO x La capa como se muestra en la estructura anterior afecta el comportamiento de conmutación del dispositivo de memristor en términos de ampliar la ventana de conductancia y mantener un estado estable durante los procesos de conmutación. Además, la conductancia del dispositivo de memristor se puede sintonizar fácilmente en trenes de pulsos positivos y negativos, respectivamente. Nuestros resultados recientes demuestran que hemos obtenido con éxito una conmutación analógica confiable y funciones bio-sinápticas debidamente emuladas, como plasticidad a corto y largo plazo (STP y LTP), función de facilitación de pulso emparejado (PPF), plasticidad dependiente del tiempo de pico ( STDP) así como la transición de STP a LTP en Ag / SiO x :Ag / TiO x / p ++ -Dispositivo de memristor Si.

Métodos

- i.

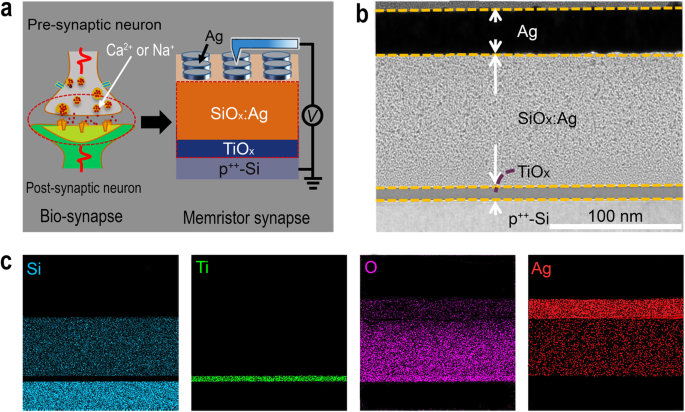

Fabricación del dispositivo:como se muestra en la Fig. 1a, nuestro memristor fue diseñado como Ag / SiO x :Ag / TiO x / p ++ -Si estructura. El p ++ -Si sustratos (15 × 15 mm 2 ) con una resistividad de aproximadamente 0,01 Ω cm se limpiaron mediante un método estándar, y luego se fabricaron los dispositivos sobre ellos. Todos los procesos siguientes se llevaron a cabo a temperatura ambiente en un sistema de alto vacío. Primero, se depositó una capa de óxido de titanio de ~ 10 nm de espesor en p ++ -Si sustratos por pulverización catódica con magnetrón RF utilizando una cerámica de alta pureza TiO 2 objetivo. Luego, un SiO x de ~ 95 nm de espesor :La capa de Ag se depositó mediante co-pulverización de RF usando un SiO 2 objetivo con pequeñas rodajas de Ag colocadas en la ruta de pulverización magnética. Durante el proceso de deposición, el caudal y la presión de Ar se mantuvieron en 50 sccm y 20 mTorr, respectivamente, mientras que la potencia de RF se mantuvo en 80 W. Finalmente, se modeló el electrodo superior (TE) de una capa de Ag de ~ 30 nm de espesor mediante una técnica de fotolitografía y despegue en la que las finas capas metálicas se depositaron mediante el uso de magnetrón de CC. El diámetro del electrodo individual es de aproximadamente 150 μm.

- ii.

Métodos de caracterización:se realizaron mediciones de microscopía electrónica de transmisión (TEM) y análisis de espectroscopía de fotoelectrones de rayos X (XPS) para analizar la microestructura de SiO x :Ag y TiO x capas y el estado químico de los átomos de Ag, respectivamente, en los que la muestra de TEM se hizo primero usando un haz de iones enfocado (FIB, FEI Nova Nano Lab 200) y luego se observó bajo un sistema FEI Phillips CM10-Supra TEM. Las caracterizaciones eléctricas se realizaron con un analizador de semiconductores (Keithley 2636B) enganchado a una estación de sonda. Durante la medición eléctrica, las polarizaciones positivas y negativas se definieron por la corriente que fluye entre el electrodo superior y el inferior. Todas las mediciones eléctricas se realizaron a temperatura ambiente en el aire.

Esquema de Ag / SiO x :Ag / TiO x / p ++ -Dispositivo de memristor Si y su análisis TEM transversal. un Ilustración esquemática del dispositivo y analogía entre la sinapsis biológica y la sinapsis electrónica. b Vista TEM transversal de una sola unidad de memristor de Ag / SiO x :Ag / TiO x / p ++ -Si estructura. El SiO x :Ag y TiO x películas delgadas intercaladas entre Ag TE y p ++ -Si BE electrodos. c El mapeo elemental de la sección transversal del dispositivo

Resultados y discusión

En la figura 1a se describe un esquema del dispositivo y la configuración de medición. El dispositivo tiene una estructura simple que consta de SiO x :Ag y TiO x capas delgadas intercaladas entre un Ag TE y un p ++ -Si BE que está confirmado por el TEM de sección transversal de la celda de memristor y el mapeo elemental que se muestra en la Fig. 1b y c. El estado químico de los átomos de Ag en la superficie de SiO x es analizado por XPS, como se muestra en el archivo adicional 1:Figura S1. El espectro Ag3d para Ag se deconvoluciona en un solo doblete con energías de unión de 368.0 eV para Ag3d 5/2 y 374.0 eV para Ag3d 3/2 , que se asignan con precisión al estado metálico Ag. La imagen HRTEM en el archivo adicional 1:la Figura S2 muestra una sección transversal del TiO amorfo x capa, mientras que los pequeños nanoclusters de Ag son visibles en SiO x :Capa de Ag, que probablemente es causada por la difusión de Ag durante el proceso de preparación de la muestra TEM para minimizar la energía interfacial total del sistema de material [22]. Además, la rápida transformada de Fourier (FFT) confirma que los nanoclusters de Ag incrustados en SiO x son de estructura policristalina, como los nanocristales de Ag (111) y Ag (002). En el Ag / SiO x :Ag / TiO x / p ++ -Dispositivo de memristor Si, el Ag / SiO x :Ag y el TiO x / p ++ -Si como la membrana presináptica y la membrana postsináptica, respectivamente, como se ilustra en la Fig. 1a. El peso sináptico cambia al liberar Ca 2+ o Na 2+ iones en un espacio entre las membranas presinápticas y postsinápticas llamado "hendidura" por la membrana presináptica cuando se reciben los pulsos neurales. De manera similar, la conductancia de Ag / SiO x :Ag / TiO x / p ++ -El dispositivo de memristor Si se puede modular artificialmente como una sinapsis electrónica a través de la migración de iones Ag bajo los impulsos de voltaje.

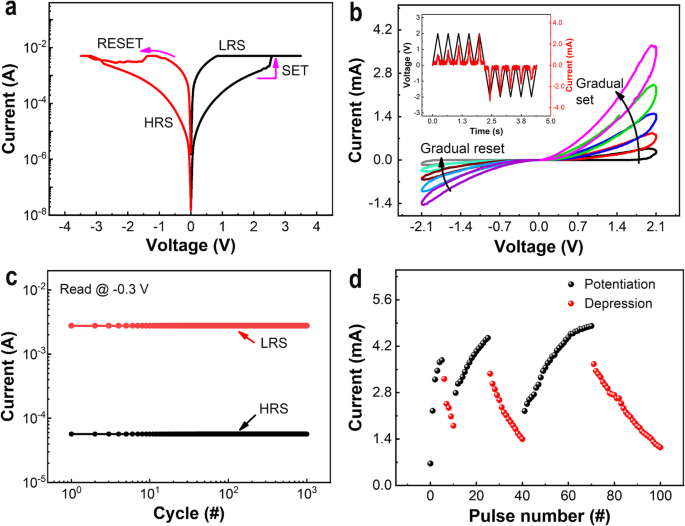

La figura 2a muestra la curva corriente-voltaje (I-V) de Ag / SiO x :Ag / TiO x / p ++ -Dispositivo de memristor Si en la escala semilogarítmica. Bajo el sesgo de barrido de 0 V → +4.0 V → −4.0 V → 0 V, la curva I-V medida muestra un bucle de histéresis pellizcado, que es una huella digital de un memristor. Cuando se aplica un sesgo positivo al Ag TE, un aumento gradual de la corriente hasta el límite de corriente de cumplimiento (I cc ) ocurre y el estado de resistencia del dispositivo cambia de un estado de alta resistencia (HRS) a un estado de baja resistencia (LRS), que se denomina proceso "SET". Mientras que, cuando se aplica un sesgo negativo al Ag TE, se produce una disminución en la corriente y el estado de resistencia se devuelve a HRS desde LRS, lo que se denomina proceso de “REINICIO”. Indica que la conductividad del dispositivo se puede modular correspondientemente con una polarización de barrido positiva o negativa, mostrando un comportamiento de conmutación resistiva bipolar. En lugar de un aumento o disminución abrupto de la corriente durante los procesos SET y RESET en un régimen de alto voltaje, es muy interesante que la corriente del dispositivo aumente o disminuya consecutivamente bajo el barrido de voltaje repetido de 0 V → +2.1 V o 0 V → −2.1 V, como se muestra en la Fig. 2b. La relación de la corriente y el voltaje frente al tiempo (I-V-t) también se representa en el recuadro de la Fig. 2b para mostrar los cambios en la conductancia con mayor claridad. Al igual que en una bio-sinapsis, se observa una respuesta obvia del dispositivo de la evolución hacia abajo o hacia arriba y hacia abajo de la corriente después de la implementación de la parte consecutiva positiva (1ª a 5ª) y negativa (6ª a 10ª) de las curvas I-V, respectivamente. El aumento (o disminución) continuo de la corriente durante los barridos de voltaje positivo (o negativo) indica que la resistencia del dispositivo se puede modular mediante el modo de barrido de CC. También se observa que durante cada barrido positivo o negativo subsiguiente, la curva I – V toma el lugar donde se quedó el último, mostrando una característica de conmutación analógica típica para un dispositivo de memristor. El rendimiento de resistencia del dispositivo de memristor se puede evaluar implementando un voltaje de barrido bipolar más amplio a un voltaje de lectura de +0,3 V, como en la Fig.2c, lo que muestra que el dispositivo se puede operar de manera estable y uniforme entre LRS y HRS durante el ajuste / reinicio. operación sobre 10 3 ciclos.

Características I – V del Ag / SiO x :Ag / TiO x / p ++ -Dispositivo de memristor Si. un Comportamiento de conmutación bipolar b Potenciación o depresión mediante la repetición de barridos de voltaje. El recuadro muestra la relación voltaje y corriente versus tiempo (V-I-t), demostrando el estado de conductancia durante la potenciación o depresión. c Prueba de rendimiento de ciclismo de resistencia con un voltaje de lectura de -0,3 V durante 10 3 ciclos de un rango más amplio de barridos bipolares de 0 a +4.0 V para set y de 0 a −4.0 V para reset. d Propiedades repetidas de la modulación de la conductancia

El dispositivo de memristor también se puede operar con señales de pulso en lugar de voltaje de barrido de polarización de CC. La Figura 2d muestra la respuesta del dispositivo en forma de potenciación o depresión después de la implementación de impulsos repetitivos de potenciación (sesgo positivo) y depresivo (sesgo negativo). Las amplitudes de los pulsos de potenciación y depresión son +1,2 V y −1,2 V, respectivamente, y todos los anchos e intervalos de pulsos se fijan en 5 ms. Aquí, la modulación de la conductancia en el dispositivo se observa independientemente del sesgo de pulso positivo o negativo, que es similar a la respuesta sináptica en forma de potenciación o depresión bajo el estímulo potenciador y deprimente, respectivamente. Obviamente, se encuentra que la respuesta del dispositivo se puede ajustar de un ciclo a otro dependiendo del número de pulsos de estimulación, lo que indica que se puede usar una potenciación y depresión estable y uniforme más allá de la polaridad del sesgo aplicado para emular el ajuste de peso y la memoria. mejora en una sinapsis electrónica [30].

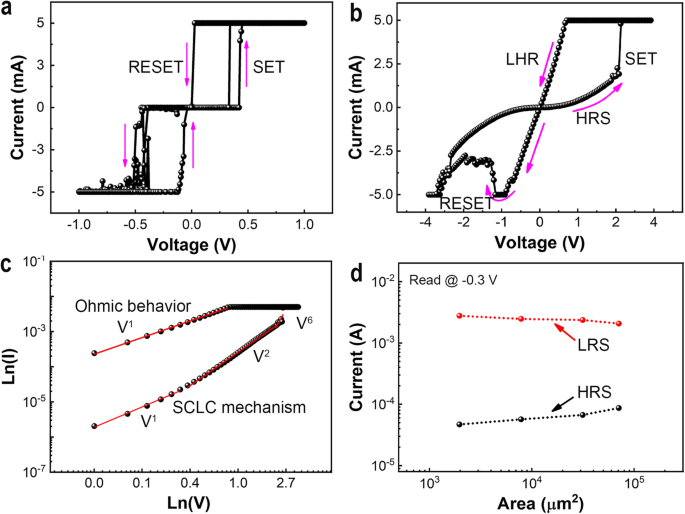

Para comprender el comportamiento de conmutación, los mecanismos de conducción se analizan ajustando las características I-V. Para este propósito, un SiO x independiente :Memristor basado en película fina de Ag con la estructura de Ag / SiO x :Ag / p ++ -Si también se fabrica. Como se muestra en la Fig. 3a, la respuesta del dispositivo a los barridos de voltaje cuasi-CC indica un comportamiento de conmutación de umbral típico, como se informó anteriormente [29, 31]. Las direcciones de las flechas muestran que el dispositivo puede alternar entre los dos estados como memoria volátil. Sin embargo, la curva I-V de Ag / SiO x :Ag / TiO x / p ++ -El dispositivo de memristor Si muestra que la situación es bastante diferente a la del SiO independiente x :Dispositivo memristor basado en Ag. La Figura 3b muestra que el dispositivo exhibe comportamientos de conmutación bipolar en el aspecto del LRS y el HRS bajo la parte positiva y negativa de la curva I-V, mientras que los voltajes operativos son relativamente más altos. La Figura 3c demuestra la curva I-V de Ag / SiO x :Ag / TiO x / p ++ -Dispositivo de memristor Si, que se ajusta como Ln (I) versus Ln (V) de datos de región positiva para HRS y LRS. Estos resultados de ajuste muestran que el comportamiento de transporte de carga en HRS es consistente con un mecanismo clásico de conducción limitada de carga espacial (SCLC) controlado por trampa, que consta de tres porciones como la región óhmica (I / V), la región de la ley de Child (I / V 2 ), y la región de fuerte aumento de la corriente [32]. Considerando que, el comportamiento lineal en LRS, donde la pendiente es =1, indica un excelente comportamiento óhmico, como se muestra en la Fig. 3c. Los diferentes comportamientos de conducción en HRS y LHR se evidencian por la formación de filamento de Ag conductor en LRS [32]. La Figura 3d apoya además que la conmutación resistiva es causada por la formación / ruptura del filamento conductor. Se puede ver que mientras que el LRS del dispositivo es independiente del tamaño de la celda del dispositivo, el HRS del dispositivo es proporcional al tamaño de la celda. Esta propiedad independiente del tamaño en el LRS se ha observado generalmente en la conducción de dispositivos de memoria basados en filamentos [33]. Por lo tanto, se puede concluir que el fenómeno de conmutación resistiva en Ag / SiO x :Ag / TiO x / p ++ -El dispositivo de memristor Si se origina típicamente a partir de la formación / ruptura controlada del filamento conductor bajo el voltaje de polarización positivo / negativo. Los cambios graduales en la conductancia podrían resultar de la variación de la brecha de la sección transversal entre TE y BE bajo el campo eléctrico similar a otros informes [34]. Entonces, la resistencia total del dispositivo se puede describir como R =Rij =V / I de acuerdo con el circuito equivalente, donde Rij se define como la resistencia relacionada con el tamaño del espacio lateral de CF entre TE y BE. Por lo tanto, si esta brecha se puede ajustar mediante la modulación del tamaño de Ag CF entre TE y BE usando una polarización programada adecuadamente, entonces la conducción o la resistencia del dispositivo memristivo se pueden sintonizar gradualmente.

Análisis del mecanismo de conducción de Ag / SiO x :Ag / p ++ -Si y Ag / SiO x :Ag / TiO x / p ++ -Si dispositivos. un La curva I – V lineal de Ag / SiO x :Ag / p ++ -Si y b Ag / SiO x :Ag / TiO x / p ++ -Si dispositivo. c Los mecanismos de conducción corresponden a SCLC en HRS y óhmico en LRS para Ag / SiO x :Ag / TiO x / p ++ -Si dispositivo según los resultados de ajuste de la región positiva de la curva I – V en ( b ). d Dependencia del área celular de la conductancia en el LRS o el HRS

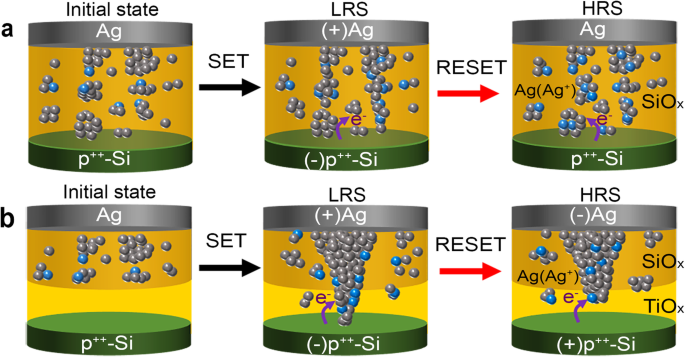

En la Fig.4 también se presenta un modelo físico correspondiente para interpretar el mecanismo de conmutación en SiO independiente x :Ag y SiO x :Ag / TiO x -Dispositivos memristor basados en. El comportamiento de las nanopartículas de Ag en SiO x Las células basadas en células pueden interpretarse basándose en reacciones electroquímicas (migración y acumulación de iones de Ag y átomos de Ag) entre los electrodos bipolares de forma similar a como se informó anteriormente [22, 35]. Cuando se aplica el voltaje de barrido, las nanopartículas de Ag crecen aún más para cerrar la brecha entre los electrodos, lo que resulta en un aumento abrupto de la corriente hasta el nivel de cumplimiento, y el memristor se enciende en LRS (como se muestra en el panel central de la Fig. 4a). Después de eliminar la polarización eléctrica, los nanoclusters de Ag alargados que formaron el puente temprano se contraen ahora rápidamente [22], y el dispositivo vuelve a HRS (como se muestra en el último panel de la Fig. 3a) [35], lo que indica un cambio de umbral bipolar comportamiento en un memristor que puede alternar entre los dos estados como en los dispositivos de memoria volátil.

Diagrama esquemático del modelo físico de comportamiento de conmutación. un Ag / SiO x :Ag / p ++ -Dispositivo de memristor Si; b Ag / SiO x :Ag / TiO x / p ++ -Dispositivo de memristor Si

La situación es bastante diferente en el caso de SiO x :Ag / TiO x dispositivo de memristor basado en SiO x La capa delgada tiene una banda prohibida alta (~ 9 eV) y una constante dieléctrica más baja (~ 3), pero el TiO x La capa tiene un intervalo de banda bajo (~ 3 eV) y una constante dieléctrica alta (~ 40), lo que hace que el campo eléctrico a través de SiO x capa superior a la del TiO x capa, disolviendo más átomos de Ag en la capa de conmutación [28]. Es la baja movilidad de los iones y la baja velocidad de reacción redox del óxido de titanio lo que controla la migración y acumulación de átomos de Ag y de iones de Ag a través de la capa interfacial [36]. Estos dos hechos, como se mencionó anteriormente, pueden causar la formación de filamentos en forma de nano-cono de TE a BE [37]. La región metálica concentrada en forma de confinamiento efectivo del crecimiento de filamentos en forma de nanoconos de TE a BE puede ofrecer el control de los estados de resistencia durante la operación cíclica [38]. Cuando el electrodo superior de Ag tiene una polarización suficientemente positiva a través de las capas dobles, el campo eléctrico a través de las capas dieléctricas es suficiente para impulsar los iones Ag del Ag TE ap ++ -Si BE a través de la capa interfacial, lo que lleva a disminuir el espacio efectivo entre electrodos (como se muestra en el panel central de la Fig. 4b). Los filamentos de Ag no se disuelven a menos que se aplique un voltaje negativo y tienden a mantener su forma original incluso se elimina el voltaje de polarización. Cuando se aplica un voltaje negativo, comienza un REINICIO normal y los Ag CF se desolan parcialmente (generalmente en la ubicación más delgada) debido al proceso electroquímico asistido por calor [39]. El dispositivo de memristor se apaga y vuelve a HRS (último panel de la Fig. 4b), y luego alterna de forma reversible entre dos estados (mostrados en la Fig. 3b) como un dispositivo de memoria no volátil. El panel izquierdo de la Fig. 4b presenta que los filamentos formados aquí deberían ser más gruesos que los del panel central de la Fig. 4a, que no pueden disolverse y romperse a menos que se aplique un voltaje negativo. La parte del filamento en el SiO x La capa es aún mucho más delgada que la de la parte del nano-cono en el TiO x capa, y la forma de todo el filamento es de alguna manera como un nano-cono. Por lo tanto, cuando se aplica una polarización negativa, el filamento se romperá rápidamente cuando se aplique voltaje negativo (Fig. 3b), mientras que la tensión aumentará aún más y la corriente aumentará nuevamente, lo que indica un riesgo de SET negativo en una polarización alta. rango debido a los átomos de Ag residuales que existen cerca de la superficie de BE.

De hecho, la resistencia total del memristor en el HRS está simplemente relacionada con el espacio entre la punta del nano-cono del filamento y el electrodo inferior, que puede aumentarse o disminuirse ajustando la polarización eléctrica [33]. Esta tendencia a alterar el HRS en los memristores se puede ver en la Fig. 2b, en la que la corriente puede aumentarse o disminuirse consecutivamente bajo el sesgo de barrido repetido de 0 V a +2,1 V y de 0 V a -2,1 V, respectivamente. Por otro lado, el barrido constante de un voltaje por debajo de +2,1 V no es suficiente para formar un filamento conductor a través del TE y BE. En cambio, el filamento conductor de Ag puede acumular gradualmente átomos de Ag, lo que lleva a una disminución en la brecha efectiva entre los electrodos, como se muestra en el archivo adicional 1:Figura S3. Por lo tanto, mediante el uso de un sesgo de programación adecuado, se puede realizar la transición del cambio de umbral típico al cambio gradual, y la resistencia total de la celda de memoria se puede sintonizar ajustando el espacio efectivo entre los electrodos, como se puede observar en una sinapsis biológica.

Similar a una biosinapsis, los estímulos de entrada con una programación de pulso adecuada pueden alterar los estados de conductancia del dispositivo de memristor para realizar varias tareas neuronales. La FPP es otro tipo de característica crucial, que puede ajustar la conductancia mediante la suma temporal de los estímulos de entrada y realizar varias tareas neuronales a corto plazo, incluido el filtrado y la adaptación sinápticos [40, 41]. La función PPF en una biosinapsis funciona de la siguiente manera:la segunda respuesta postsináptica se vuelve más alta que la primera durante dos estímulos de picos sucesivos, dejando el intervalo de tiempo de picos menor que el tiempo de recuperación [22]. La Figura 5a muestra la respuesta del dispositivo, que se monitorea después de implementar un par de pulsos de facilitación a una amplitud de +2.0 V con un ancho e intervalo fijos nombrados como una escala de 0.08 s. Se observa un aumento notable en la corriente como respuesta del segundo pulso al primero, lo que indica un cambio aparente del estado de conductancia después de la implementación de la programación de pulso adecuada. Durante el intervalo entre dos pulsos posteriores, se observa una disminución de la corriente, que puede atribuirse a la existencia de carácter volátil en el dispositivo. La disminución de la conductancia podría corresponder a la difusión de átomos de Ag después de la eliminación del pulso de potenciación [42]. La función PPF exitosa solo se puede ejecutar cuando el intervalo de tiempo entre dos pulsos consecutivos es menor que el tiempo de relajación de difusión de los átomos de Ag, lo que provoca que se introduzcan más átomos de Ag en el SiO x :Ag / TiO x capa. Además, se logra un estado de saturación cuando el dispositivo se estimula continuamente con un número de pulsos de facilitación con una amplitud de +2.0 V y un ancho e intervalo fijos nombrados como una escala de 0.08 s, como se muestra en la Fig. 5b. Los resultados muestran que cuando se aplican pulsos de alta frecuencia, qué bombea más átomos de Ag en el SiO x capa hasta que se forme un puente conductor a través del TE y BE, logrando un nivel de saturación [22]. Este fenómeno es bastante similar a la regla de aprendizaje de Hebb, donde los cambios de peso sináptico deben tener un valor saturado para evitar la excitabilidad excesiva de las neuronas con los picos no teñidos del tren de pulsos aplicados [43].

Resultados experimentales de la facilitación de pulsos emparejados (FPP) . un Implementación de PPF en Ag / SiO x :Ag / TiO x / p ++ -Si dispositivo que usa +2.0 V de altura de pulso con 0.08 s. b Demostración del movimiento del peso sináptico de saturación usando un tren de pulsos de amplitud +2.0 V con el mismo ancho e intervalo de 0.08 s

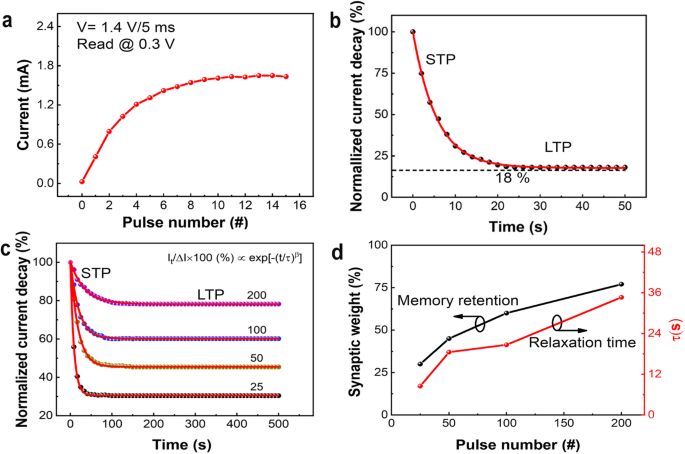

Además, al igual que en una sinapsis biológica, un memristor sufrirá una pérdida de memoria con una disminución repentina de la corriente después de la implementación de un pico de potenciación, que puede atribuirse a la existencia de STP en el memristor [44, 45]. En neurobiología, STP y LTP se atribuyen comúnmente como memoria a corto plazo (STM) y memoria a largo plazo (LTM) [46]. Se ha establecido que la transición de STP a LTP podría ocurrir mediante la repetición de estímulos (es decir, un proceso de ensayo) [46, 47]. Para verificar y comparar este comportamiento con los observados en sinapsis biológicas, se ha implementado una secuencia de pulsos de voltaje a nuestro Ag / SiO x :Ag / TiO x / p ++ -Dispositivos de memristor Si. La Figura 6a muestra el aumento de corriente desde un estado inicial de 0.05 mA a 1.8 mA después de la implementación de 15 pulsos consecutivos (amplitud +1.4 V, ancho e intervalo de 5 ms). La caída de corriente normalizada ((I t -Yo o ) / Yo o × 100%) se mide a la lectura de voltaje +0,3 V inmediatamente después de imponer pulsos de potenciación con el tiempo ( t ), como se muestra en la Fig. 6b. La relación entre la caída de corriente normalizada y el tiempo bien ajustada por la relación dada en la Ec. (1) [48]:

$$ {\ Delta I} _t / {\ Delta I} _o \ times 100 \% =\ exp \ left [- {\ left (t / \ tau \ right)} ^ {\ beta} \ right] $$ ( 1)

Decaimiento actual y retención de memoria en Ag / SiO x :Ag / TiO x / p ++ -Si memristor. un Aumento de la corriente después de la implementación de 15 consecutivos que potencian pulsos idénticos. b La caída de corriente se controla a un voltaje de lectura de +0,3 V después de estimular el dispositivo. c La caída de la corriente normalizada frente al tiempo que muestra la transición de STP a LTP después de la implementación de trenes de pulsos del número de estimulación. d El tiempo de retención y relajación de la memoria ( τ ) para pulsar números

aquí, τ se llama tiempo de relajación y β se llama índice de estiramiento (0 < β <1). Generalmente, esta relación se utiliza para describir los procesos de relajación en materiales desordenados con una distribución aleatoria de energías. La curva muestra que la caída en el peso sináptico es similar a la "curva de olvido" de la memoria humana en psicología [49], que presenta una caída rápida al principio que podría llamarse STP y luego alcanza gradualmente un nivel estable que podría llamarse LTP. en el dispositivo. Sin embargo, se observa una caída obvia de la corriente normalizada en el dispositivo en un intervalo de tiempo muy corto ( t ) y luego alcanza un nivel de saturación en un estado de baja conductancia (hasta el 16% en 50 s). En esta situación, sin ningún otro cambio en los parámetros de pulso, hemos llevado a cabo un proceso de simulación adicional con un número repetido de pulsos. The current is measured at a read voltage of +0.3 V immediately after imposing different numbers of pulses (i.e., 25, 50, 100, and 200) from the same initial state for each set of pulse trains. Figure 6c shows that the normalized current decay with time in each set of measurements is fitted by the relation given in Eq. (1). Figure 6d shows that by an increase of the stimulation number, the relaxation time (τ ) increases, indicating forgetting process fades slowly. Meanwhile, an obvious elevation of the current level is observed, implying a positive change in synaptic weight (conductance), as shown in Fig. 6d by the black line. These results presented in Fig. 6 provide clear evidence of the existence of STP and LTP in our device. A smaller number of stimulations can only induce STP in the device, with a slight rise in conductance at saturation level. Therefore, by increasing the number of repetitive stimulations, the rehearsal process not only rises a conductance level but also is achieved a long-lasting memory retention phenomenon, as shown in Fig. 6d by the red line.

The conventional digital-type memories require the non-volatility to store the information, while in bio-synapse, information processes and accordingly reconfigures the memory status. It can be seen in Fig. 6 that the transition from STP to LTP is realized, and the synaptic weight is adjusted accordingly, while the unimportant ones with small synaptic weight are temporarily stored and then diminished with time. This phenomenon is quite similar to the “multi-store model” presented by Atkinson and Shiffrin [50]. In this model, first input information is analyzed, then stored in different hierarchy levels, according to the importance of “synaptic weight” through the rehearsal process. Therefore, an increase in synaptic weight and resultant prolonged relaxation time (τ ) in our device as a function of stimulation numbers has best verified the rehearsal scheme.

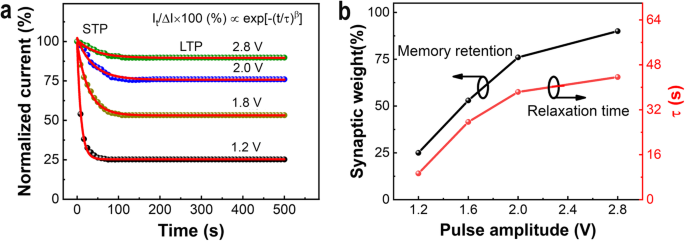

Besides the pulse repetition process, the transition of the STP to the LTP phenomenon is further examined as a function of pulse strength. The device response is monitored after implementation of different pulse amplitudes, i.e., +1.2 V, +1.6 V, +2.0 V, and +2.8 V with similar width and interval scale of 3 ms, as shown in Fig. 7a. The current is monitored with a readout voltage of +0.3 V after imposing each pulse train consisting of 50 pulses. The fitted results with the stretched exponential relaxation model in Fig. 7a shows that the relaxation time is increased as a function of pulse strength (as shown in Fig. 7b red line). Meanwhile, as shown in Fig. 7b, an elevation of the synaptic weight of about 90% is observed at a larger τ of 43 s and +2.8 V amplitude, which is much higher than the synaptic weight of about 25% at a smaller τ of 10 s and +1.2 V amplitude (as shown in Fig. 7b black line), indicating the formation of LTP. Based on these results, it is easy to find that the formation and persistence of LTP in our device are highly dependent on both pulse numbers or pulse amplitude. These results coincide with the facts that the memory states, i.e., STM and LTM, and their stabilities in bio-synapses are related to the input stimulus characteristics.

Experimental results of current decay in Ag/SiOx :Ag/TiOx /p ++ -Si memristor device after the stimulation process. un The normalized current decay versus time showing the transformation from STP to LTP; b The memory retention and relaxation time (τ ) as a function of the pulse amplitude

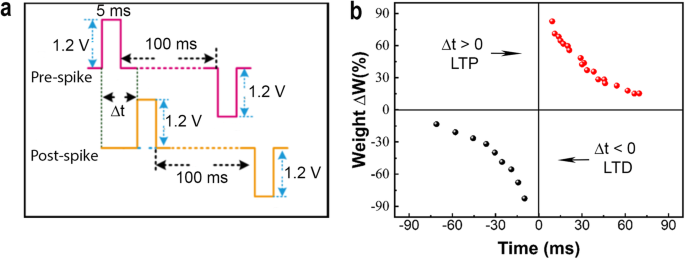

The spike-time-dependent-plasticity (STDP) is another fundamental character for learning and memory function [51] in a biological synapse. It has been reported [52] that in the electronic synapse, the weight can be modulated by a relative timing of pre- and post-synaptic pulses. The Hebbian STDP rule works as follows:if the pre-spike precedes the post-spike (Δt> 0), it could reinforce the connection strength between two neurons. In contrast, if the post-spike heads the pre-spike (Δt <0), it could weaken the connection strength between two neurons. Such kinds of reinforcement and weakening of connection strength between two neurons are also called LTP and LTD, respectively [45]. In the whole process, the order of pre- and post-spikes with respect to time determines the weight change (ΔW) polarity. In order to emulate the STDP rule in our device, a pair of pulses (+1.2 V, 5 ms, and −1.2 V, 5 ms) as pre- and post-spiking signals are implemented, as shown in Fig. 8a. It can be seen that there will emerge a more considerable conductance change (synaptic weight) with the decrease of Δt (in both cases when Δt> 0 and Δt <0). The percentage change in synaptic weight is defined as ΔW =(Gt −G0 )/G0 × 100%. Here, G0 is the conductance measured before stimulation and Gt is the conductance measured after the stimulation using pre- and post-spiking pairs, respectively. A plot is shown in Fig. 8b, that can explain the relationship between ΔW and Δt before and after the simulation process. It can be seen that when the pre-synapse (positive) appears before the post-spike (negative) (Δt> 0), the conductance is enhanced with an increase in ΔW along with the decrease in Δt. On the contrary, when the pre-synapse (positive) appears after the post-spike (negative) (Δt <0), the net conductance of the device is decreased (depressed) in ΔW along with the increase in Δt. These results have demonstrated that our Ag/SiOx :Ag/TiOx /p ++ -Si memristor device has successfully emulated the Hebbian STDP learning rule in the form of an artificial synapse.

Experimental results for implementation of STDP rule in Ag/SiOx :Ag/TiOx /p ++ -Si memristor device. un The schematic illustration of implementing electrical programming bias comprising the pair of pulses at amplitudes +1.2 V and −1.2 V fixed with the same width of 5 ms. The approaching time difference between stimulus pulses is Δt ms (t =±10n, n =1, 2, …, 10); b The synaptic weight (ΔW) as a function of spike timing (Δt), demonstrating well on the potentiation and depression behaviors in the memristor device

Conclusiones

In summary, a new kind of memristor device with the simple structure of Ag/SiOx :Ag/TiOx /p ++ -Si has been fabricated by a physical vapor deposition process. The synaptic characteristics of the memristor with a wide range of resistance change for synaptic weight modulation by implementing positive or negative pulse trains have been investigated extensively. Several crucial learning and memory functions have been demonstrated simultaneously in such a single fabricated memristor device, including short-/long-term potentiation and depression (STP/STD, LTP/LTD), PPF and the STP-to-LTP transition as well as STDP, which are adjusted and controlled by repeating pulses more than a rehearsal operation. Furthermore, the analysis of logarithmic I-V characteristics with corresponding physical model indicates that the controlled formation/dissolution of Ag-filaments across the Ag and p ++ -Si electrodes could improve the performance of the new Ag/SiOx :Ag/TiOx /p ++ -Si memristor device with a buffer layer of TiOx between the SiOx :Ag layer and the bottom electrode. This developed device, as an artificial synapse, might bring a potential research prospect in the design and hardware implementation of new-generation biomimetic neural networks and computing systems.

Disponibilidad de datos y materiales

Todos los datos están completamente disponibles sin restricciones.

Abreviaturas

- BE:

-

Electrodo inferior

- HRS:

-

High-resistance state

- I-V:

-

Corriente-voltaje

- LRS:

-

Low-resistance state

- LTM:

-

Long-term memory

- LTP:

-

Long-term plasticity

- PPF:

-

Paired-pulse-facilitation

- SCLC:

-

Space-charge limited conduction

- STDP:

-

Spike-time-dependent-plasticity

- STM:

-

Short-term memory

- STP:

-

Short-term plasticity

- TE:

-

Electrodo superior

- TEM:

-

Microscopía electrónica de transmisión

- XPS:

-

Espectroscopia de fotoelectrones de rayos X

Nanomateriales

- Señales analógicas y digitales

- Tipos de sensores analógicos y digitales con aplicaciones

- Funciones duales del dispositivo V / SiOx / AlOy / p ++ Si como selector y memoria

- Efectos de las variaciones de grabado en la formación de canales Ge / Si y el rendimiento del dispositivo

- Efecto de las heteroestructuras bicapa CeO2 − x / ZnO y ZnO / CeO2 − x y la polaridad de electroformado en las propiedades de conmutación de la memoria no volátil

- Absorbedor de infrarrojo cercano mejorado:silicio negro estructurado fabricado en dos pasos y su aplicación en el dispositivo

- Propiedades fotocatalíticas sensibles a la luz visible mejoradas de los compuestos de nanohojas Ag / BiPbO2Cl

- Dispositivo multifuncional con funciones conmutables de absorción y conversión de polarización en el rango de terahercios

- Comportamiento del conjunto de electrocatalizador de membrana y electrocatalizador nanoestructurado en una celda de combustible de glicerol directo pasivo

- La inteligencia artificial predice el comportamiento de los sistemas cuánticos

- Ventajas y desventajas de la inteligencia artificial