Funciones duales del dispositivo V / SiOx / AlOy / p ++ Si como selector y memoria

Resumen

Esta letra presenta funciones duales que incluyen selector y cambio de memoria en un V / SiO x / AlO y / p ++ Si dispositivo de memoria resistiva simplemente controlando el límite de corriente de cumplimiento (CCL). El cambio de umbral unidireccional se observa después de una formación positiva con CCL bajo de 1 μA. Los cambios al lado del electrodo V del oxígeno forman el VO x capa, donde el cambio de umbral puede explicarse por el fenómeno de transición de aislamiento de metal. Para una CCL más alta (30 μA) aplicada al dispositivo, se obtiene una conmutación de memoria bipolar, que se atribuye a la formación y ruptura del filamento conductor en SiO y capa. AlO y de 1,5 nm de espesor La capa con alta conductividad térmica juega un papel importante en la reducción de la corriente de salida para la conmutación de memoria y umbral. A través de la dependencia de la temperatura, se confirma la barrera de alta energía (0,463 eV) en el LRS, que puede causar no linealidad en un estado de baja resistencia. Cuanto menor sea la CCL, mayor será la no linealidad, lo que proporciona un tamaño de matriz más grande en la matriz de puntos cruzados. La coexistencia de la conmutación de la memoria y el umbral de acuerdo con la CCL proporciona la flexibilidad para controlar el dispositivo para su uso previsto.

Antecedentes

La memoria resistiva de acceso aleatorio (RRAM) es uno de los candidatos prometedores para la tecnología de memoria no volátil de próxima generación debido a su rápida velocidad de conmutación [1, 2], bajo consumo de energía [3,4,5,6,7 , 8], capacidad multinivel [9,10,11,12,13,14,15], alta escalabilidad [16,17,18,19,20] y capacidad de apilamiento 3D [21,22,23,24,25 ]. Estas propiedades son especialmente adecuadas para la memoria de clase de almacenamiento (SCM) que puede llenar la brecha de rendimiento entre la memoria dinámica de acceso aleatorio (DRAM) como memoria principal y la unidad de estado sólido (SSD) como memoria de almacenamiento. A pesar de que el dispositivo RRAM ha avanzado mucho en los últimos años [1,2,3,4,5,6,7,8,9,10,11,12,13,14,15,16,17,18,19 , 20,21,22,23,24,25], queda, sin embargo, una gran desventaja:la corriente furtiva a través de las células vecinas se produce en una matriz de puntos de cruce de alta densidad [26]. El dispositivo de memoria con el componente selector debe proporcionar características de corriente-voltaje (I – V) no lineales para superar este problema [26, 27, 28, 29, 30, 31, 32, 33, 34, 35]. Hasta ahora, varios dispositivos con conceptos no lineales como conmutación resistiva complementaria (CRS) [26], barrera de túnel [27,28,29,30,31,32,33], conmutación de umbral basada en Ag [34], tipo diodo selector [35, 36], conmutación de umbral ovónico (OTS) [37, 38] y transición de aislante metálico (MIT) [39,40,41,42,43]. Voz x como uno de los materiales típicos del MIT, podría usarse ampliamente en aplicaciones potenciales como componente de conmutación óptica y eléctrica [40,41,42]. SiO 2 se utiliza ampliamente como capa de pasivación en la industria de los semiconductores. Además, SiO x rico en Si ( x <2) se puede utilizar como una capa de cambio de resistencia en RRAM [44,45,46,47,48,49,50,51,52,53,54,55]. SiO x puede ser preferido sobre muchos otros materiales en términos de compatibilidad con procesos CMOS y bajo costo. SiO x Se ha informado que los dispositivos basados en RRAM actúan como mediadores de la función de los puentes conductores simplemente mediante el uso de electrodos como Cu y Ag con alta difusividad [44,45,46,47]. En otro caso, el cambio de memoria es inducido por el efecto de cambio de valencia dentro del SiO x capa, que puede explicarse por la generación de vacantes de oxígeno o el modelo de intercambio de protones [48,49,50,51,52,53,54,55]. En la conmutación unipolar, donde una operación establecida precede a un reinicio, es sensible a la atmósfera ambiental. El rendimiento de conmutación en el aire se degrada significativamente [48,49,50,51,52,53]. Por otro lado, la conmutación filamentaria sin efectos de exploración hacia atrás muestra la conmutación unipolar y bipolar típica en varios SiO x -dispositivos RRAM basados en [52, 53, 54].

Aquí, presentamos la coexistencia de conmutación de umbral y conmutación de memoria en V / SiO x / AlO y / p ++ Dispositivo de Si en función del límite de corriente de cumplimiento (CCL). El dispositivo con electrodo de fondo de silicio (BE) tiene varias ventajas en comparación con el electrodo de metal convencional. El dispositivo RRAM con conmutación de memoria o umbral se conecta directamente a la fuente o al lado de drenaje en un transistor, que es una aplicación potencial para memoria integrada y dispositivo de pendiente pronunciada. La corriente de sobreimpulso podría reducirse debido a la resistencia en serie de Si BE. Además, la nanopunta de silicio BE a través del grabado en húmedo y el ajuste de la concentración de dopaje en la superficie del silicio pueden mejorar el rendimiento de conmutación. El AlO y La capa, que es una gran banda prohibida con una propiedad aislada, ayuda a reducir la corriente de funcionamiento durante el umbral y la conmutación de memoria. El SiO x La capa actúa como una capa de conmutación de memoria en un CCL alto, mientras que sirve para suministrar oxígeno a V TE a un CCL bajo, lo que proporciona un cambio de umbral.

Métodos

V / SiO x / AlO y / p ++ El dispositivo de Si se fabricó de la siguiente manera:en primer lugar, BF 2 Se implantaron iones con una energía de aceleración de 40 keV y una dosis de 5 × 10 15 cm −2 en un sustrato de Si a Si BE fuertemente dopado. El daño de la red se curó mediante el proceso de recocido a 1050 ° C durante 10 min. El Si BE muy dopado tenía una resistencia laminar de 30,4 Ω / □. A continuación, un AlO y de 1,5 nm de espesor La capa fue depositada por un sistema de deposición de capa atómica (ALD) usando H 2 O y Al (CH 3 ) 3 y un SiO x de 5,5 nm de espesor La capa se sometió a una deposición de vapor químico mejorada con plasma (PECVD) al reaccionar 5% de SiH 4 / N 2 (160 sccm), N 2 O (1300 sccm) y N 2 (240 sccm) a 300 ° C. Posteriormente, se depositó un electrodo superior (TE) de vanadio (V) de 50 nm de espesor con un diámetro de 100 μm mediante pulverización catódica con CC de un objetivo V con gas Ar (30 sccm). Finalmente, se depositó un Al de 50 nm de espesor como capa protectora mediante pulverización catódica con CC para evitar una mayor oxidación de V TE. Todas las propiedades eléctricas se caracterizaron mediante el barrido de voltaje CC y los modos de pulso utilizando un analizador de parámetros de semiconductores (SPA) Keithley 4200-SCS y un módulo ultrarrápido de corriente-voltaje (I – V) 4225-PMU a temperatura ambiente, respectivamente. Para el funcionamiento del dispositivo, el TiN BE se conectó a tierra y se controló la polarización de Ni TE.

Resultados y discusión

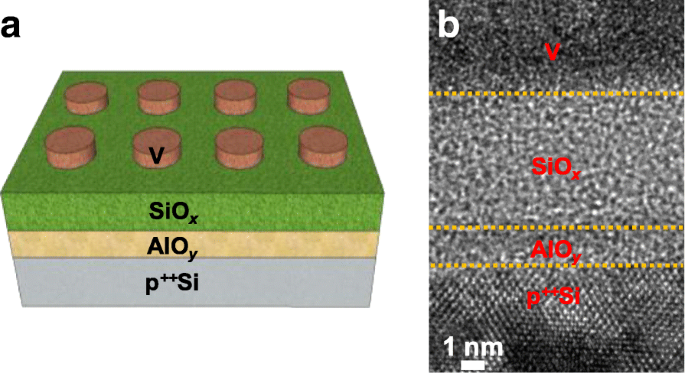

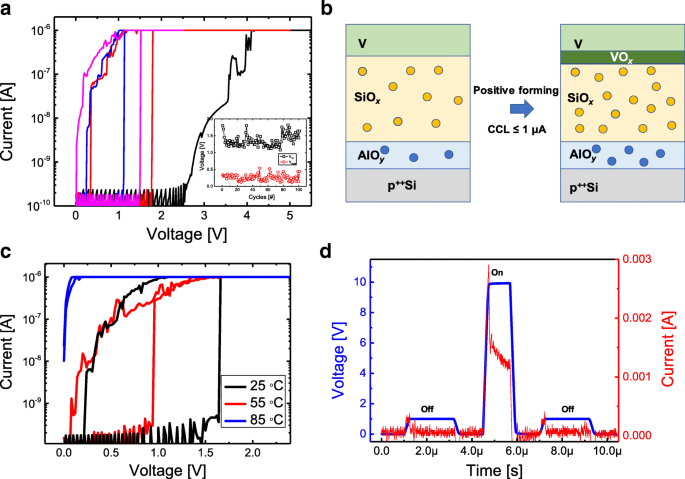

La figura 1a muestra la estructura esquemática de V / SiO x / AlO y / p ++ Dispositivo Si. Tres V amorfos, SiO x y AlO y Las capas y la capa de Si monocristalino se observan mediante una imagen de sección transversal de microscopía electrónica de transmisión (TEM) como se muestra en la Fig. 1b. Los espesores del SiO x y AlO y las capas son de 5,5 y 1,5 nm, respectivamente. Para confirmar la relación de composición de dos películas dieléctricas, se realizó un análisis XPS (archivo adicional 1). La x valor de SiO x y el y valor de AlO y son 0,88 y 1,33, respectivamente. Nuestro SiO x película con PECVD en comparación con SiO 2 depositado mediante oxidación seca se deposita a una temperatura mucho más baja y tiene muchos más defectos, lo que los hace adecuados para la conmutación resistiva a voltajes relativamente más bajos. La figura 2a muestra el cambio de umbral típico de V / SiO x / AlO y / p ++ Dispositivo Si. La conmutación inicial con un proceso de formación positivo requiere un voltaje más alto que la conmutación de umbral posterior, ya que las capas dieléctricas tienen defectos inicialmente más pequeños. Se aplica un CCL de 1 μA al dispositivo para evitar la formación de filamentos conductores excesivos en el SiO x capa. La corriente de fuga es muy baja (100 pA a 1 V) en comparación con el cambio de umbral de VO x informado anteriormente . Esta ventaja se atribuye al Al 2 O 3 con mayor permitividad y conductividad térmica en comparación con el SiO 2 . El estado desactivado tiene la propiedad de aislar porque los filamentos se rompen fácilmente y luego no quedan filamentos. Un posible mecanismo para el cambio de umbral es la oxidación del V TE del oxígeno suministrado por el SiO x capa durante el proceso de formación positiva como se muestra en la Fig. 2b. La propiedad eléctrica de VO x entre V TE y SiO x La capa puede cambiar de un estado aislante a un estado metálico, provocando un cambio repentino en la resistencia. Un CCL bajo de 1 μA no es suficiente para producir filamentos conductores eficientes dentro del SiO x película. Por lo tanto, SiO x con propiedades aislantes puede ser otra causa para reducir la corriente de salida. Para un proceso de formación negativo de V / SiO x / AlO y / p ++ Si dispositivo, no se observa un cambio de umbral (ver archivo adicional 1). Cuando se aplica el sesgo negativo al V TE, el movimiento del óxido se mueve hacia el Si BE, de modo que el V TE ya no puede participar en el cambio de umbral como VO x . El recuadro de la Fig. 2a muestra el voltaje umbral (V th ) y mantener el voltaje (V hold ) durante los 100 ciclos. La V ésima donde la corriente aumenta bruscamente con una pendiente casi infinita entre 1.08 y 1.82 V, y V hold en cuyo punto el retorno de la corriente a un estado de alta resistencia se encuentra entre 0,12 y 0,54 V. La figura 2c muestra las características I – V en la corriente a diferentes temperaturas. A 25 ° C y 55 ° C, muestran un cambio de umbral casi similar, pero la curva I – V a una temperatura más alta de 85 ° C pierde la propiedad de cambio de umbral. Es bien sabido que VO x pierde su MIT a altas temperaturas. Por lo tanto, este resultado es otra prueba de que VO x es la principal causa del cambio de umbral. La figura 2d muestra las características transitorias para la conmutación de umbral. El pulso con la amplitud de 1 V monitoreó la corriente de lectura antes y después del pulso de escritura con un ancho de 1 μs. La alta corriente fue monitoreada mientras se aplicaba el pulso con alta amplitud al dispositivo, y luego, el V / SiO x / AlO y / p ++ El dispositivo Si apagó la corriente inmediatamente después de que se eliminó el pulso de escritura. Las propiedades del selector analizadas anteriormente se pueden usar cuando se combinan con la operación de elementos de memoria por debajo de 1 μA [55, 56].

Configuración del dispositivo de V / SiO x / AlO y / p ++ Si. un Dibujo esquemático y b Imagen TEM

Conmutación de umbral unidireccional de V / SiO x / AlO y / p ++ Si cuando se aplica un conformado positivo con CCL de 1 μA. un Curvas I – V típicas. b Dibujo esquemático del proceso de conformado. c Características I – V por dependencia de la temperatura. d Características transitorias

La Figura 3a muestra la conmutación resistiva bipolar de V / SiO x / AlO y / p ++ Dispositivo de Si después de una formación positiva con CCL de 100 μA. Luego, el proceso de reinicio con un rápido aumento de la resistencia se realiza barriendo el voltaje negativo y el dispositivo se cambia a un estado de alta resistencia (HRS). El proceso de ajuste con una rápida disminución de la resistencia se produce luego a un voltaje de polarización positivo, lo que hace que el dispositivo vuelva a un estado de baja resistencia (LRS). Para comprender las propiedades del filamento conductor, observamos la conductancia normalizada y la dependencia de la temperatura. La conducción en el LRS es una pauta importante para informar indirectamente las propiedades del filamento conductor. La Figura 3b muestra la conductancia normalizada (G N ) que se define como la conductancia dinámica (G d ) dividir por conductancia estática (G 0 ) para curvas I – V de V / SiO x / AlO y / p ++ Dispositivo de Si en el LRS con diferentes temperaturas. Independientemente de la temperatura, el G N el valor converge a 1 cuando el voltaje es cero. Esto nos permite descartar el conocido mecanismo de conducción como la emisión de Schottky, el túnel de Fowler-Nordheim y la ley de Child (I ~ V 2 ) en corriente limitada de carga espacial (SCLC). La conducción óhmica metálica también se puede excluir considerando la dependencia de la temperatura como se muestra en la Fig. 3c. La disminución de la resistencia al aumentar la temperatura sugiere que el filamento conductor tiene una propiedad semiconductora. Por lo tanto, podemos excluir la penetración de V en el SiO x capa para el filamento conductor principal de V / SiO x / AlO y / p ++ Dispositivo Si en LRS. Por lo tanto, la operación de memoria bipolar del V / SiO x / AlO y / p ++ El dispositivo de Si está dominado por la conmutación intrínseca de SiO x . También se confirma que las corrientes positivas y negativas no son muy diferentes, lo que sugiere que en lugar de un tipo de interfaz como la emisión de Schottky, está dominada por la conducción en masa. Teniendo en cuenta la conductancia normalizada mencionada anteriormente, existen dos posibles mecanismos de conducción dominante en masa. El primero es la conducción por salto siguiendo la fórmula:

$$ J ={qnav} _o {e} ^ {- q {\ o} _T / kT} {e} ^ {qaV / 2 dkT} $$

Conmutación de memoria de V / SiO x / AlO y / p ++ Si cuando se aplica un conformado positivo con CCL de 30 μA. un Curvas I – V típicas. b Conductancia normalizada. c En (I) versus 1000 / T. d Dibujo esquemático del proceso de conformado

donde q , n , a , ø T , v o y d son la carga eléctrica, la concentración de la carga espacial, la media de la distancia de salto, la altura de la barrera de electrones para el salto, la frecuencia de vibración intrínseca y el espesor de la película dieléctrica, respectivamente. El ø T calculado a partir de la pendiente de un gráfico lineal de ln (I) frente a 1000 / T es 0,463 eV como se muestra en la Fig. 3c. Un valor calculado a partir de la relación entre E a y V es 5,17 nm, lo que indica el filamento conductor formado en el SiO x no es fuerte y está cerca del estado HRS. El otro mecanismo de conducción, la emisión de Poole-Frenkel (P-F), se trató en el archivo adicional 1. Según los resultados anteriores, el modelo de filamento conductor en la operación de memoria de V / SiO x / AlO y / p ++ El dispositivo de Si se muestra en la Fig. 3d. En el proceso de formación positiva, el proceso de oxidación procedió en el lado V TE, pero debido al alto CCL, se puede formar un filamento conductor dentro del SiO x y AlO y debido al movimiento de las vacantes de oxígeno. Durante el proceso de reinicio, el campo eléctrico opuesto al de formación y fraguado induce el oxígeno y la recombinación con la vacante de oxígeno, lo que resulta en la ruptura del filamento conductor. Se observa que las operaciones de selector y memoria se observan en la misma celda. La operación de memoria es posible después de que se haya producido la operación de umbral y luego el interruptor esté completamente apagado. Sin embargo, la dirección inversa no es posible porque la conmutación de reinicio de la operación de memoria no está completamente desactivada.

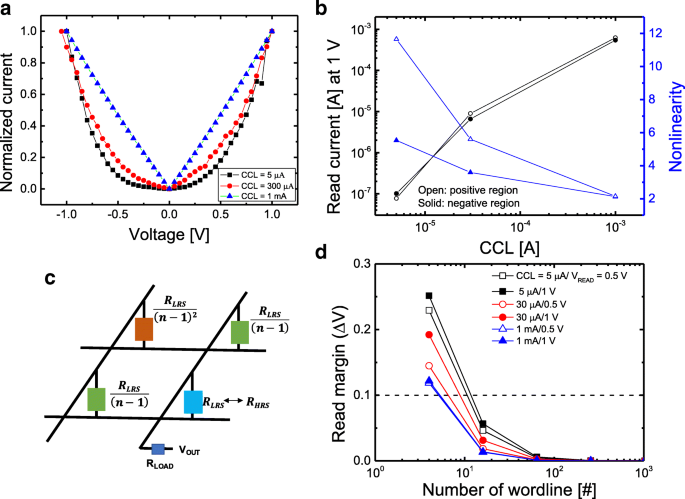

La Figura 4a muestra curvas I – V normalizadas en el LRS de V / SiO x / AlO y / p ++ Dispositivo de Si en régimen de bajo voltaje (0 ~ 1 V) para diferentes condiciones CCL (5 μA, 30 μA y 1 mA). Aquí, la curva I – V normalizada se define como la corriente en cada voltaje dividida por la corriente a 1 V. Dado que los niveles de la corriente LRS que dependen de la CCL varían, establecemos el valor de la corriente en 1 V para comparar fácilmente la no linealidad. Se puede observar que a medida que disminuye el CCL, la corriente se suprime en un régimen de voltaje más bajo. Para derivar una relación más cuantitativa, la no linealidad se define como la relación de la corriente en V READ a eso en la mitad de V READ . La Figura 4b muestra la corriente de lectura a 1 V y la no linealidad como una función de CCL para V / SiO x / AlO y / p ++ Dispositivo Si. La disminución en la corriente de lectura debido a la reducción de CCL sugiere que el filamento conductor se vuelve más fino y luego aumenta la no linealidad. La película de óxido de silicio intrínseca exhibe una alta no linealidad incluso en una sola capa. La propiedad no lineal intrínseca se debe a la naturaleza en masa del óxido de silicio más que a la interfaz del silicio. Cuanto más pequeña es la CCL, menos degradación se genera en el SiO x , por lo que se puede minimizar la reducción del nivel de energía de la trampa en el LRS en comparación con el del HRS. Por lo tanto, la barrera de energía más alta puede maximizar la no linealidad en el estado LRS cuando se aplica una CCL más baja al dispositivo. De manera similar, la conducción descrita por la emisión P-F en el TaO x / TiO y stack asegura una alta no linealidad [57]. Otra posibilidad es que debido a que la constante dieléctrica del óxido es menor, se hagan más pases a la película de óxido debido a la concentración del campo. Esto puede conducir a la disminución del nivel de energía de la trampa de la capa de óxido, que se puede esperar que sirva como una barrera de túnel para Al 2 O 3 . Obtener el margen de lectura (∆V) en n × n matriz de puntos cruzados, utilizamos el circuito equivalente simplificado como se muestra en la Fig. 4c. Considerando el peor de los casos, las celdas adyacentes se establecen en el LRS y la resistencia de carga (R L ) a la resistencia LRS. El ∆V se calculó a partir de la diferencia entre V OUT en LRS y V OUT en HRS. La Figura 4d muestra el ∆V en función del número de líneas de palabras ( n ) para V / SiO x / AlO y / p ++ Dispositivo Si. Cuanto menor sea el CCL, mayor será el ∆V porque aumenta la no linealidad. Cuando se asegura un margen de lectura del 10%, la matriz se puede expandir a aproximadamente más de 10 × 10 para CCL de 5 μA y a 5 × 5 para CCL de 1 mA. El tamaño de la matriz para soportar la corriente furtiva no es suficiente, pero ayudará a expandir el tamaño de la matriz cuando el dispositivo con función de selector esté conectado en un V / SiO x / AlO y / p ++ Dispositivo Si. En comparación con la lectura de 0,5 V en todos los CCL, tiene una mayor no linealidad con lectura a 1 V. Aunque el V READ es bajo conduce a una baja potencia estática en la operación de lectura, el valor de no linealidad se vuelve más pequeño, lo que se debe al hecho de que el campo eléctrico es menor en el SiO x / AlO y capa en V READ más pequeña .

Características no lineales de V / SiO x / AlO y / p ++ Si para cambio de memoria. un Curvas I – V con diferentes CCL. b Leer actual y no linealidad como funciones de CCL. c Circuitos equivalentes de matriz de puntos cruzados. d Lea el margen en función del número de línea de palabra para diferentes CCL y lea el voltaje

Conclusiones

En este trabajo, un V / SiO x / AlO y / p ++ Se investiga un dispositivo de Si que tiene un selector y una función de memoria simplemente controlando CCL. Cuando se aplica un CCL de 1 μA o menos, se observa una conmutación de umbral unidireccional para la aplicación del selector. La formación positiva oxida el electrodo V y el fenómeno MIT de VO x puede inducir un cambio de umbral. El AlO y capa es capaz de lograr una alta selectividad de 10 4 reduciendo la corriente de salida. Por otro lado, cuando se aplica un CCL de 5 μA o más, se observa un cambio de memoria a medida que se forman filamentos conductores efectivos en el SiO x capa. Cuanto menor sea el CCL, mayor será la no linealidad, lo que ayuda a aumentar el tamaño de la matriz de puntos cruzados.

Abreviaturas

- ALD:

-

Deposición de la capa atómica

- BE:

-

Electrodo inferior

- CCL:

-

Límite actual de cumplimiento

- CRS:

-

Conmutación resistiva complementaria

- DRAM:

-

Memoria dinámica de acceso aleatorio

- HRS:

-

Estado de alta resistencia

- I – V:

-

Corriente-voltaje

- LRS:

-

Estado de baja resistencia

- MIT:

-

Transición de metal-aislante

- OTS:

-

Cambio de umbral ovónico

- PECVD:

-

Deposición de vapor químico mejorada con plasma

- P-F:

-

Poole-Frenkel

- RRAM:

-

Memoria resistiva de acceso aleatorio

- SCLC:

-

Corriente limitada por carga espacial

- SCM:

-

Memoria de clase de almacenamiento

- SPA:

-

Analizador de parámetros de semiconductores

- SSD:

-

Unidad de estado sólido

- TE:

-

Electrodo superior

- TEM:

-

Microscopía electrónica de transmisión

- V:

-

Vanadio

Nanomateriales

- Términos y conceptos de la memoria digital

- Qué es un sistema operativo y sus componentes

- Gestión de memoria C++:nuevo y eliminar

- Memoria de partición:introducción y servicios básicos

- Los procesadores abordan la convergencia de IoT y AI

- Control de no linealidad dual de las propiedades de modo y dispersión en la guía de ondas plasmónica de grafeno-dieléctrico

- Un estudio colectivo sobre modelado y simulación de memoria resistiva de acceso aleatorio

- Monocapa de g-GaN adsorbido por metales alcalinos:funciones de trabajo ultrabajo y propiedades ópticas

- Fabricación IoT:definición, funciones y ejemplos

- Piezas de la máquina ranuradora y sus funciones.

- Tipos de diferencial y sus funciones.