Un regulador de voltaje mejorado transitoriamente con estabilidad y aumento del rechazo de la fuente de alimentación

Resumen

En este documento se propone un regulador de voltaje (VR) de alta estabilidad, que integra mejora transitoria y protección contra sobrecorriente (OCP). Teniendo en cuenta el rendimiento y las ventajas de área de los dispositivos de bajo voltaje, la mayoría de las partes de control del VR propuesto son suministradas por el voltaje de salida regulado, que forma la técnica de autoalimentación (SPT) con refuerzo de rechazo de la fuente de alimentación (PSR). Además, la estabilidad y la respuesta transitoria se mejoran mediante la técnica de carga dinámica (DLT). También se adopta un circuito de retroalimentación de sobrecorriente integrado para proteger el VR presentado de daños en situaciones de sobrecarga. El VR propuesto se implementa en una tecnología BCD estándar de 350 nm, cuyos resultados indican que el VR puede funcionar de manera constante con un voltaje de entrada de 5,5 a 30 V, un rango de carga de 0 a 30 mA y un capacitor de salida de 0,1 a 3,3 μF. Se logra una regulación de línea de 2,98 μV / V y una regulación de carga de 0,233 mV / mA con una limitación de corriente de 40 mA. El PSR es mejor que - 64 dB hasta 10 MHz con un condensador de salida de 0,1 μF.

Introducción

En los diseños modernos de sistemas en chip (SoC) a escala nanométrica, los diferentes subbloques generalmente requieren diferentes rieles de suministro para lograr algunas funciones específicas. Además, es posible que todo el sistema SoC deba operar bajo un amplio rango de voltaje de entrada y aún así proporcionar un alto rendimiento que no se vea afectado por los cambios en las condiciones de suministro [1]. Así, el regulador de voltaje (VR) de amplio rango de voltaje de entrada implementado en tecnología de escala nanométrica puede ser uno de los candidatos más adecuados para este tipo de aplicaciones. En comparación con su contraparte de conmutación, como el regulador de conmutación y la bomba de carga, la VR lineal tiene la ventaja de alta precisión, bajo ruido de salida y tamaño compacto. La mayoría de los VR lineales realizan su función de regulación de voltaje con un solo suministro de voltaje, pero solo unos pocos pueden lograr la combinación de un amplio rango de suministro de energía, bajo nivel de ruido, transitorios rápidos, alta capacidad de carga y características de protección adicionales [2, 3, 4] .

Para realizar una amplia gama de fuentes de alimentación, es necesaria la utilización de transistores que puedan soportar presiones de alto voltaje. Sin embargo, este tipo de transistores suele ocupar más área y tiene un peor rendimiento en comparación con los transistores estándar. Dos de las soluciones existentes para reducir el uso de transistores de alta tensión son el método de prerregulador [5, 6] y el método de transistores de baja tensión apilados [7, 8]. El primero utiliza un prerregulador adicional para proporcionar un voltaje de suministro interno para el regulador del núcleo. Este último implementa transistores de bajo voltaje apilados bien diseñados para mantener los voltajes terminales de los transistores dentro del límite de la tecnología [7]. Sin embargo, estos métodos limitan el margen de tensión. Este documento adopta la técnica de autoalimentación (SPT) para lograr un amplio rango de suministro de energía, lo que significa que la mayoría de los módulos centrales en el bucle de regulación son alimentados por el voltaje de salida regulado del VR propuesto [9]. Sin ningún circuito adicional, SPT puede mejorar el rendimiento de la realidad virtual y también reducir la cantidad de dispositivos de alto voltaje.

Al usar SPT, la primera etapa de ganancia del amplificador de error (EA) es suministrada por el voltaje de salida regulado del VR propuesto. Al diseñar cuidadosamente la segunda etapa de EA, el ruido de alta frecuencia del voltaje de entrada tiene poco impacto en el voltaje de salida del EA. Además, en este documento se adopta la arquitectura de transistor de potencia tipo N. Por lo tanto, el regulador propuesto tiene un alto rechazo de la fuente de alimentación (PSR) y un buen rendimiento de ruido [10,11,12,13,14,15].

La respuesta transitoria rápida también es un índice importante para medir el rendimiento de los VR [16, 17, 18, 19, 20], que generalmente se logra agregando un bucle de aceleración adicional [21]. En este artículo, la mejora transitoria se realiza mediante la técnica de carga dinámica (DLT). Durante el procedimiento de respuesta transitoria, DLT introduce una corriente adicional que cambia en consecuencia con las condiciones de carga para actuar como una carga dinámica, mediante la cual se puede suprimir el sobreimpulso y el subimpulso del voltaje de salida regulado [9].

Con la ayuda de DLT, la estabilidad del lazo dentro de un amplio rango de carga se fortalece porque la corriente de carga adicional puede reducir la variación de la posición del polo no dominante. Para hacer que el lazo sea estable, la compensación Miller con resistencia de anulación también se usa para generar un polo de baja frecuencia y un cero adicional para compensar el polo de salida. Además, una serie de resistencias con el capacitor de salida introduce otro cero para compensar el polo generado por la capacitancia de la puerta parásita del transistor de potencia [6, 9, 22, 23].

Finalmente, un bucle limitador de corriente integrado está diseñado para evitar daños por sobrecorriente y mejorar la confiabilidad del VR propuesto [9, 24,25,26,27].

Este documento está estructurado de la siguiente manera. El principio y el mecanismo del VR propuesto se ilustran en la sección "Método", incluido el circuito de protección contra sobrecorriente (OCP), el circuito de mejora de transitorios y DLT, el método de aumento de estabilidad y el análisis de PSR. Los resultados de desempeño y las comparaciones con otras publicaciones relacionadas se muestran en la sección “Resultados y discusión”. La sección "Conclusión" extrae la conclusión de la realidad virtual propuesta.

Método

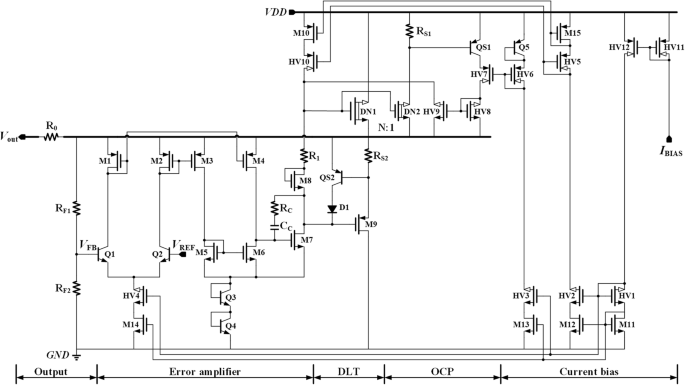

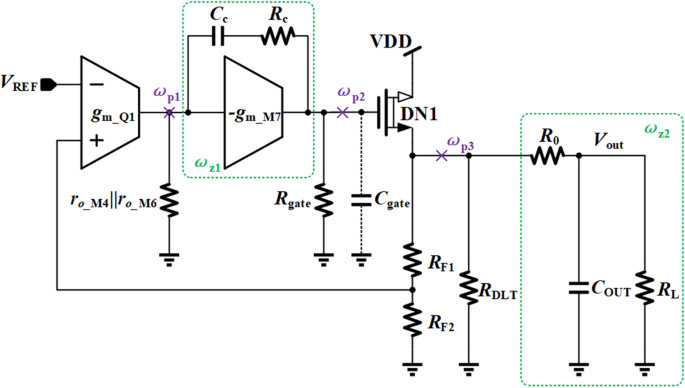

El circuito detallado del VR propuesto se muestra en la Fig.> , HV n , Q n , DN n y D n , respectivamente en la figura, donde n es el número de secuencia del dispositivo relevante.

El circuito detallado de la realidad virtual propuesta

La VR propuesta incluye principalmente cinco submódulos:polarización de corriente, OCP, DLT, EA y etapa de salida. El circuito de polarización de corriente proporciona corriente de polarización para todo el sistema regulador [12, 14]. El voltaje de referencia se puede generar de muchas formas diferentes [1], y el circuito detallado no se muestra aquí. Un bucle de limitación de corriente incorporado funciona como un circuito OCP para limitar la corriente de carga a un valor preestablecido. El circuito de mejora de transitorios, implementado por DLT, logra la supresión de sobreimpulsos y subimpulsos mediante el cambio adaptativo de la corriente de carga durante el procedimiento de transitorios. El bucle de regulación de retroalimentación negativa está formado por EA y la etapa de potencia de salida para ajustar el voltaje de salida. Suponiendo que el voltaje de salida V FUERA y por lo tanto el voltaje de retroalimentación V FB fuera menor que el valor deseado, el voltaje de puerta del transistor de potencia DN1 se elevaría con la ayuda del bucle de regulación para aumentar el voltaje de salida, y viceversa. Finalmente, el voltaje de salida puede estabilizarse en

$$ {V} _ {\ mathrm {OUT}} \ approx {V} _1 ={V} _ {\ mathrm {REF}} \ left ({R} _ {\ mathrm {f} 1} + {R} _ {\ mathrm {f} 2} \ right) / {R} _ {\ mathrm {f} 2} $$ (1)En la Fig. 1, se puede observar que el voltaje de salida del VR propuesto también alimenta la primera etapa de ganancia de EA, que se denomina SPT. Con esta técnica de multiplexación de potencia, la mayoría de los dispositivos del bucle de regulación pueden implementarse mediante dispositivos de bajo voltaje. En comparación con sus homólogos de alto voltaje, los dispositivos de bajo voltaje tienen mayor rendimiento, menor costo y menor área, lo que hace que el bucle de regulación propuesto logre una buena capacidad de regulación mucho más fácil. En cuanto a la segunda etapa de EA, Q3 y Q4 se agregan para levantar el riel de suministro de tierra, que se adopta para limitar el voltaje de la fuente de drenaje de M7, V DS_M7 . En otras palabras, Q3 y Q4 pueden evitar que M7 tenga una gran presión de voltaje.

En aras de la simplicidad, el circuito simplificado se utiliza para ilustrar las ideas de innovación en el análisis posterior.

Circuito OCP propuesto

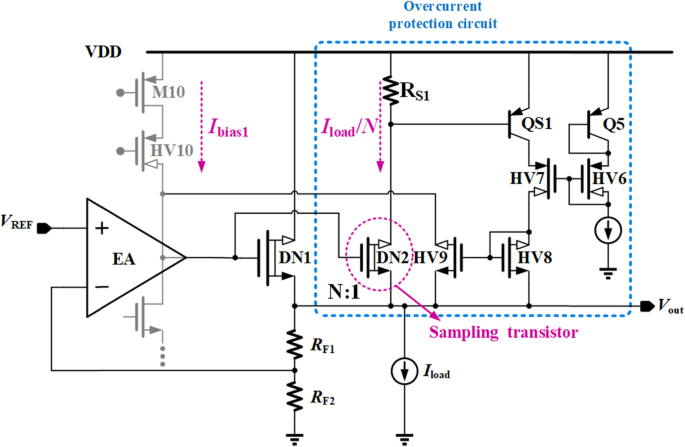

La Figura 2 muestra el circuito OCP propuesto. El bucle de limitación de corriente propuesto puede cambiar automáticamente el modo de funcionamiento de acuerdo con las diferentes condiciones de carga. La corriente máxima de la VR propuesta se puede limitar reduciendo el voltaje de la puerta del transistor de potencia cuando ocurre una sobrecarga.

Principio del OCP propuesto

El mecanismo del OCP propuesto es el siguiente. El transistor de muestreo DN2 detecta proporcionalmente la corriente que fluye a través de DN1, que es aproximadamente igual a la corriente de carga I Cargar , lo que hace que el voltaje caiga en R S1 , V RS1 , reflejan el nivel de corriente de carga. Una vez V RS1 alcanza el voltaje de encendido de QS1, HV8 y HV9 formará un espejo de corriente para desviar una corriente de la segunda etapa de EA. Luego, el voltaje de la puerta de DN1 se puede bajar para limitar la corriente de carga a un valor preestablecido, que se puede expresar como

$$ {I} _ {\ mathrm {Load}} \ le N \ times \ left ({V} _ {EB \ left (\ mathrm {QS} 1 \ right)} / {R} _ {S1} \ right ) $$ (2)donde N es la relación del factor de tamaño de DN1 a DN2. El propósito de Q5 y HV6 es proporcionar un voltaje de polarización adecuado a HV7 y, por lo tanto, proteger a QS1 de condiciones de sobretensión.

Hay un circuito de retroalimentación negativa incorporado en el OCP propuesto. La ganancia de bucle T y el polo dominante p dominante de este bucle de límite de corriente puede estar dado por,

$$ T ={g} _ {m \ _ \ mathrm {DN} 2} {R} _ {S1} {g} _ {m \ _ \ mathrm {QS} 1} {R} _ {\ mathrm {puerta } \ _ \ mathrm {OC}} $$ (3) $$ {p} _ {\ mathrm {dominante}} =1 / \ izquierda ({R} _ {\ mathrm {puerta} \ _ \ mathrm {OC} } {C} _ {\ mathrm {puerta}} \ derecha) $$ (4)donde g m_DN2 y g m_QS1 son la transconductancia de DN2 y QS1, respectivamente. R gate_OC ≈ ( g m_HV10 r o_HV10 r o_M10 ) || r o_M7 || r o_HV9 y C puerta ≈ C gs_DN1 son la resistencia y la capacitancia de salida equivalentes en el nodo de puerta del transistor de potencia DN1 cuando se produce una sobrecorriente, respectivamente. Cuando el VR propuesto normalmente opera sin sobrecorriente, HV9 está en la región de corte y, por lo tanto, la resistencia de salida equivalente en el nodo de puerta de DN1 llamado R puerta se puede expresar como [( g m_HV10 r o_HV10 r o_M10 ) || r o_M7 ].

Circuito de mejora transitoria y DLT propuesto

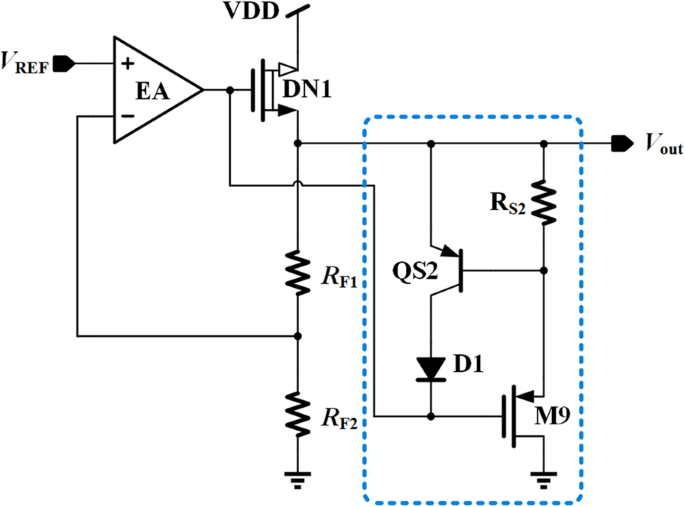

La Figura 3 muestra el circuito de mejora transitoria usando DLT. Dado que la corriente de carga es proporcional a Vgs_DN1 e inversamente proporcional a Vsg_M9, la corriente que fluye a través de M9 es mayor en condiciones de carga ligera y cercana a cero en condiciones de carga pesada. Por lo tanto, a medida que aumenta la corriente de carga, se puede introducir una corriente disminuida en la carga de salida total. Mediante este método, este circuito se puede igualar a una carga dinámica, lo que puede ser útil tanto para la mejora transitoria como para aumentar la estabilidad del bucle de regulación.

El circuito de mejora transitoria propuesto

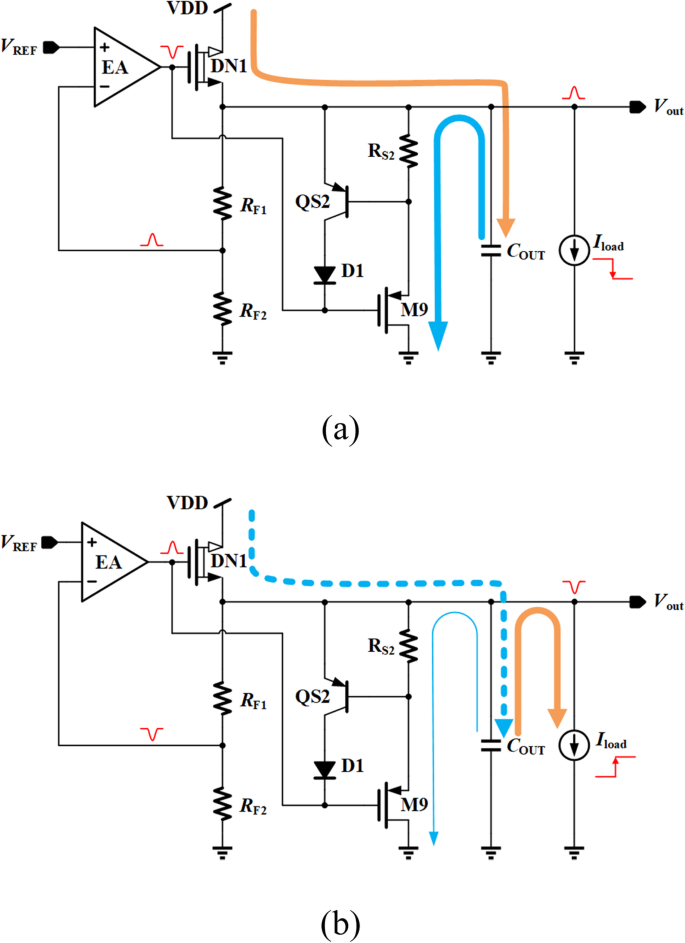

El principio operativo detallado de mejora transitoria es el siguiente. Si la corriente de carga experimenta una disminución repentina, la corriente que fluye a través del transistor de potencia DN1 no cambiará inmediatamente debido a la capacidad limitada de ajuste del bucle y la velocidad de respuesta. Esta corriente, que se muestra en la Fig. 4a como una ruta amarilla, provocará un sobreimpulso en el voltaje de salida y, por lo tanto, aumentará la caída de voltaje en R S2 y M9. Luego, una corriente adicional fluye a través de R S2 y M9, que se muestra en la Fig. 4a como una ruta azul, se genera en la salida regulada para cancelar la corriente de ruta amarilla no deseada. Por lo tanto, el pico de voltaje de salida se reduce de manera efectiva.

Respuesta transitoria de la RV propuesta. un cambio de corriente de carga pesada a ligera. b cambio de corriente de carga ligera a pesada

La Figura 4b demuestra el caso de cambio de corriente de carga ligera a pesada, donde se produce un subimpulso en la salida regulada y luego la corriente que fluye a través de R S2 y M9 disminuye. Esto puede ser equivalente a proporcionar una carga de corriente reducida, por lo que la corriente neta que fluye a través del transistor de potencia DN1 aumenta y se puede lograr la supresión de voltaje por debajo del alcance.

Para proteger M9 de sobrecorriente, se agregan QS2 y D1. Cuando el voltaje en R S2 es mayor que el voltaje de encendido de QS2, la corriente adicional fluirá hacia QS2 y D1. La corriente máxima en M9 se establece en

$$ {I} _ {\ mathrm {M} 9 \ _ \ max} \ le \ left ({V} _ {BE \ _ QS2} / {R} _ {S2} \ right) $$ (5)El propósito de D1 es evitar que QS2 caiga en la región de amplificación invertida y fluya una corriente invertida en ella, que es un estado anormal de la función de límite de corriente M9.

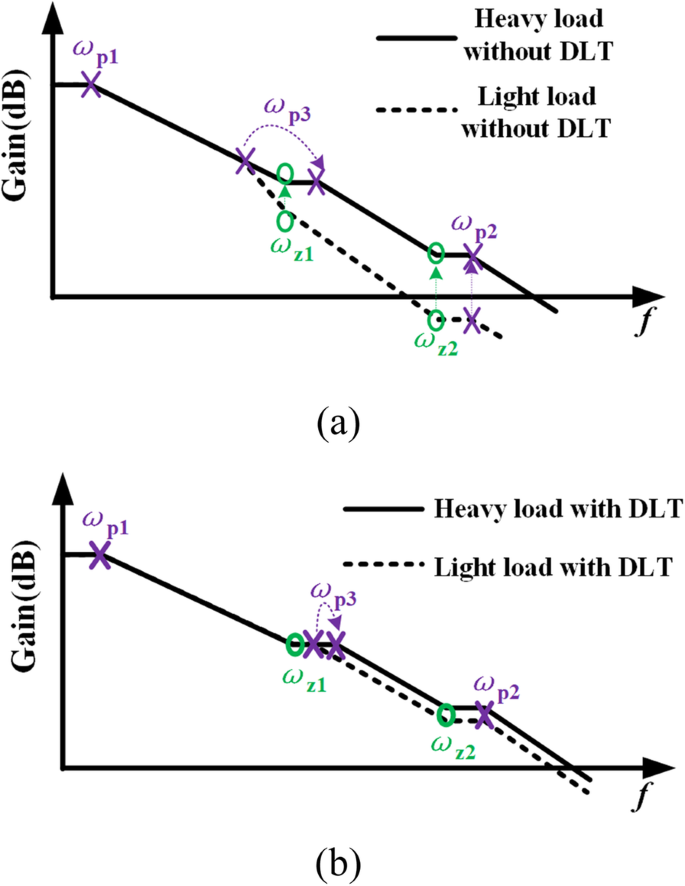

Aumento de la estabilidad de la realidad virtual propuesta

Como se muestra en la Fig.5, hay tres polos ω p1 , ω p2 y ω p3 y dos ceros ω z1 y ω z2 en el bucle de control, y la ganancia del bucle del VR propuesto es

$$ {A} _ {\ mathrm {Vloop}} ={A} _O \ beta $$ (6)

Distribución de polos y ceros de la realidad virtual propuesta

donde A O es la ganancia de lazo abierto del VR, y β es el coeficiente de retroalimentación,

$$ {A} _O ={A} _ {\ mathrm {CD} 0} {A} _ {E0} \ frac {\ left (1 + s / {\ omega} _ {Z1} \ right) \ left ( 1 + s / {\ omega} _ {Z2} \ right)} {\ left (1 + s / {\ omega} _ {P1} \ right) \ left (1 + s / {\ omega} _ {P3} \ right) \ left (1 + s / {\ omega} _ {P2} \ right)} $$ (7) $$ \ beta =\ frac {R _ {\ mathrm {F} 2}} {R _ {\ mathrm {F} 1} + {R} _ {\ mathrm {F} 2}} $$ (8)donde A CD0 ≈ 1 es la ganancia de baja frecuencia de la etapa de potencia que opera como un seguidor de voltaje y A E0 es la ganancia de baja frecuencia del EA,

$$ {A} _ {E0} ={g} _ {m \ _Q1} \ left ({r} _ {o \ _M4} \ Big \ Vert {r} _ {o \ _M6} \ right) {g} _ {m \ _M7} {R} _ {\ mathrm {puerta}} $$ (9)Considerando el efecto Miller y la capacitancia parásita en el nodo de la puerta de DN1, los polos y ceros se escriben como [13]

$$ {\ omega} _ {p1} =1 / \ left [{g} _ {m \ _M7} {R} _ {\ mathrm {gate}} {C} _c \ times \ left ({r} _ { o \ _M4} \ Big \ Vert {r} _ {o \ _M6} \ right) \ right] $$ (10) $$ {\ omega} _ {p2} ={g} _ {m \ _M7} / { C} _ {\ mathrm {puerta}} $$ (11) $$ {\ omega} _ {p3} =1 / \ left \ {\ left [{R} _L \ Big \ Vert \ left ({g} _ {m \ _ \ mathrm {DN} 1} ^ {- 1} \ Big \ Vert {R} _ {\ mathrm {DLT}} + {R} _0 \ right) \ right] {C} _ {\ mathrm { OUT}} \ right \} $$ (12) $$ {\ omega} _ {z1} =1 / \ left [{C} _c \ left ({R} _c-1 / {g} _ {m \ _M7 } \ right) \ right] $$ (13) $$ {\ omega} _ {z2} =1 / \ left [\ left ({R} _0 \ Big \ Vert {R} _L \ right) {C} _ {\ mathrm {FUERA}} \ derecha] $$ (14)donde R DLT es la resistencia equivalente del circuito de mejora transitoria; C FUERA es el condensador de salida del VR propuesto.

Dado que el condensador de compensación C C está agrandado por ( g m_M7 R puerta ) debido al efecto Miller en el nodo p1, el polo ω p1 es el polo dominante. El segundo poste debe ser ω p3 , porque C FUERA suele estar en el rango de varios microfaradios. Aunque el condensador parásito C puerta es relativamente grande, aún es más pequeño que la capacitancia equivalente en el nodo p1 y el capacitor de salida. Además, la resistencia en el nodo p2 es de solo 1 / g m_M7 . Por lo tanto, el poste ω p2 se encuentra en alta frecuencia. El cero ω z1 es cancelar el polo de frecuencia media ω p3 . La resistencia R 0 genera un cero ω z2 para compensar el polo parasitario interno ω p2 . La estabilidad del VR propuesto se puede mejorar como resistencia R 0 creciente. Sin embargo, la resistencia R 0 aumentará el error del voltaje de salida debido a la caída de voltaje causada por la corriente de carga. Por lo tanto, la resistencia R 0 debe establecerse en un valor razonable para hacer una buena compensación entre la precisión del voltaje de salida y la estabilidad del lazo.

En un regulador de voltaje convencional sin DLT, el polo en el nodo de salida estará a una frecuencia diferente debido a la variación de la transconductancia del transistor de potencia inducida que cambia la corriente de carga. A medida que aumenta la corriente de carga, la transconductancia del transistor de potencia g m _DN1 aumentará y, por lo tanto, el polo de salida se moverá hacia la alta frecuencia mientras que los otros ceros y polos se mantendrán en la misma posición, como se muestra en la Fig. 6a. Esto puede dificultar la compensación de frecuencia del sistema y ralentizar la respuesta transitoria en condiciones de carga ligera. Más en serio, el sistema puede ser inestable.

Respuesta de frecuencia del regulador de voltaje. un Regulador de voltaje sin técnica de carga dinámica. b El regulador de voltaje propuesto con técnica de carga dinámica

Con la ayuda del DLT propuesto, el VR presentado tiene una mejor estabilidad con diferentes cargas. Como se analizó anteriormente, la corriente a través del circuito de carga dinámica disminuye a medida que aumenta la corriente de carga en estado estable y viceversa. Dado que esta corriente es proporcionada por DN1, puede suprimir las variaciones de transconductancia de DN1 dentro de un rango de corriente de carga más amplio, lo que es útil para la estabilidad del sistema y la constancia del ancho de banda durante un rango de carga más amplio mediante el uso del DLT propuesto. La respuesta de frecuencia del VR propuesto se muestra en la Fig. 6b, que puede garantizar la estabilidad con una respuesta transitoria rápida.

El condensador de salida establece la posición del cero ω z2 . Al colocar el polo cero de manera razonable, el sistema tendrá una mejor estabilidad con diferentes C FUERA .

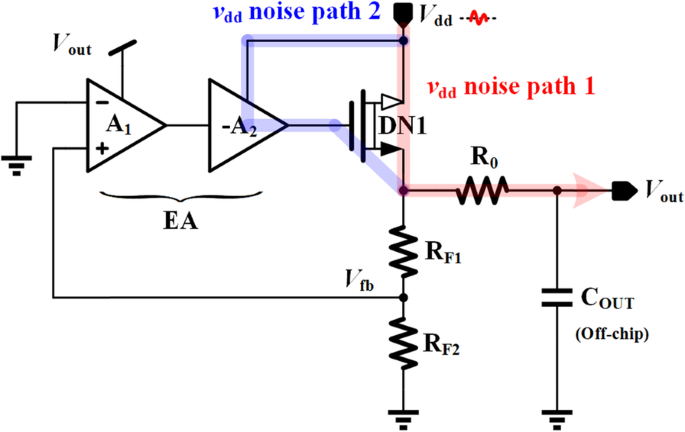

Análisis de PSR de la RV propuesta

PSR es uno de los parámetros críticos para medir el rendimiento de los reguladores de voltaje y se refiere a la capacidad de rechazo frente a las ondas de alta frecuencia y el ruido que surge del voltaje de suministro. En esta sección se adopta el método de análisis PSR propuesto por Gupta 12, cuya idea principal es simplificar todo el sistema regulador en un modelo de divisor de voltaje. Como se muestra en la Fig.7, hay dos rutas de ruido de V dd a V fuera :la ruta 1 transfiere directamente el ruido del drenaje del transistor de potencia DN1 a V fuera ; La ruta 2 va desde la segunda etapa de EA hasta la puerta del transistor de potencia DN1. El efecto de la ruta 2 se puede expresar como

$$ {A} _ {\ mathrm {ruta} 2} \ approx \ frac {r_ {o \ _M7}} {g_ {m \ _ \ mathrm {HV} 10} {r} _ {o \ _ \ mathrm { HV} 10} {r} _ {o \ _M10}} $$ (15)

Análisis PSR del VR propuesto

Como se muestra en (15), A ruta2 Es bastante pequeño con la ayuda del SPT propuesto y la estructura del espejo actual de cascode. Esto hace que la influencia de la ruta 1 sea dominante en el análisis de PSR.

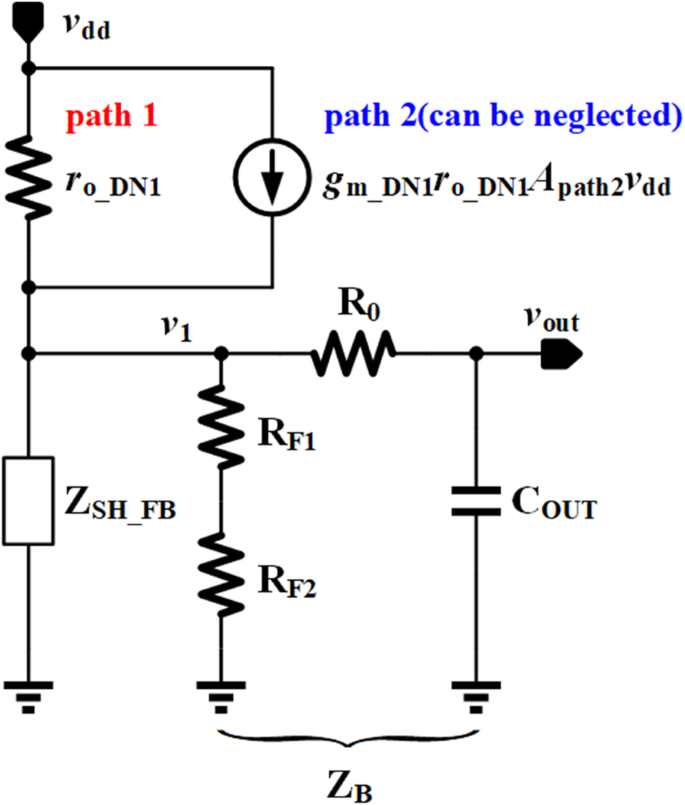

El modelo PSR simplificado del VR propuesto se muestra en la Fig.8, donde r o_DN1 es la resistencia de salida del transistor de potencia DN1 que representa la ruta de ruido 1, la fuente de corriente controlada se origina en la ruta de ruido 2, Z B consta de R F1 , R F2 , R 0 y C FUERA actuando como un filtro a alta frecuencia, y Z SH_FB es la impedancia equivalente que incluye la función de bucle de retroalimentación negativa. Z SH_FB puede ser dado por

$$ {Z} _ {SH \ _ FB} =\ frac {1} {g_ {m \ _ DN1} \ left (1+ \ beta {A} _E \ right)} $$ (16)

El modelo simplificado de PSR

donde g m_DN1 es la transconductancia del transistor de potencia DN1. Por lo tanto, la función de transferencia de PSR se puede expresar como

$$ \ mathrm {PSR} =\ frac {V _ {\ mathrm {out}}} {V _ {\ mathrm {dd}}} =\ frac {\ left (1+ {g} _ {m \ _ \ mathrm { DN} 1} {r} _ {o \ _ \ mathrm {DN} 1} {A} _ {\ mathrm {ruta} 2} \ right) \ left ({Z} _B \ Big \ Vert {Z} _ { \ mathrm {SH} \ _ \ mathrm {FB}} \ right)} {r_ {o \ _ \ mathrm {DN} 1} + {Z} _B \ Big \ Vert {Z} _ {\ mathrm {SH} \ _ \ mathrm {FB}}} $$ (17)Estableciendo deliberadamente la ganancia intrínseca de HV10 mucho mayor que la del transistor de potencia DN1, g m_DN1 r o_DN1 A ruta2 Se puede lograr <<1 y, por lo tanto, se puede despreciar la fuente de corriente controlada. La expresión de PSR se puede simplificar aún más como

$$ \ mathrm {PSR} \ approx \ frac {Z_B \ Big \ Vert {Z} _ {\ mathrm {SH} \ _ \ mathrm {FB}}} {r_ {o \ _ \ mathrm {DN} 1} + {Z} _B \ Big \ Vert {Z} _ {\ mathrm {SH} \ _ \ mathrm {FB}}} $$ (18)Desde Z B y Z SH_FB cambiará con la variación de frecuencia, es necesario analizar la característica de frecuencia del PSR.

La baja frecuencia

A baja frecuencia, la ganancia de EA es muy alta y C FUERA puede tratarse como circuito abierto. Por lo tanto, Z B >> Z SH_FB y el PSR se puede escribir como

$$ {\ mathrm {PSR}} _ {\ mathrm {LF}} \ approx \ frac {1} {g_ {m \ _ \ mathrm {DN} 1} {r} _ {o \ _ \ mathrm {DN} 1} \ left (1+ \ beta {A} _ {E0} \ right)} $$ (19)La frecuencia media

La impedancia de Z SH_FB aumentará porque la ganancia del bucle disminuye en la frecuencia media. En esta etapa, la Z SH_FB sigue siendo pequeño y el PSR se ve afectado principalmente por la ganancia de bucle. Con respecto a (7), el PSR puede expresarse como

$$ {\ mathrm {PSR}} _ {\ mathrm {MF}} \ approx \ frac {1} {g_ {m \ _ \ mathrm {DN} 1} {r} _ {o \ _ \ mathrm {DN} 1} \ left (1+ \ beta {A} _ {E0} \ right)} \ frac {1 + s / {\ omega} _p} {1 + s / \ left [{\ omega} _p \ left (1 + \ beta {A} _ {E0} \ right) \ right]} $$ (20)Como se muestra en (20), el PSR está empeorando y el ruido del voltaje de salida es más serio mientras que la frecuencia aumenta dentro de la frecuencia de ganancia unitaria.

La alta frecuencia

Debido al aumento de frecuencia, Z SH_FB se vuelve grande y finalmente se acercará a 1 / g m_DN1 . La impedancia de C FUERA se vuelve más pequeño, pero sigue siendo mucho más grande que R 0 . Entonces R 0 se puede omitir como antes. El PSR de alta frecuencia depende de la división de voltaje entre r o_DN1 y 1 / g m_DN1 en paralelo con C FUERA , que puede estar representado por

$$ {\ mathrm {PSR}} _ {\ mathrm {HF}} \ approx \ frac {1} {g_ {m \ _ \ mathrm {DN} 1} {r} _ {o \ _ \ mathrm {DN} 1}} \ frac {1} {1 + s {C} _ {\ mathrm {OUT}} / {g} _ {m \ _ \ mathrm {DN} 1}} $$ (21)A alta frecuencia, el ruido en el voltaje de salida se puede suprimir en gran medida debido al efecto de C FUERA .

Como se analizó anteriormente, la buena capacidad anti-ruido en todo el rango de frecuencia de la realidad virtual propuesta está garantizada por tres aspectos. En primer lugar, se adopta una alta ganancia de bucle; En segundo lugar, SPT hace que el ruido de la fuente de alimentación tenga poco impacto en la puerta del transistor de potencia; En tercer lugar, el condensador de salida C FUERA puede mejorar el PSR a alta frecuencia con propiedad de filtrado.

Resultados y discusión

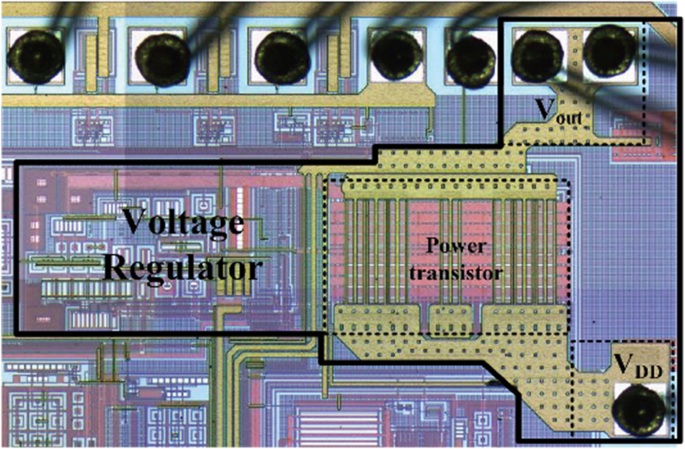

La VR propuesta se ha implementado en una tecnología BCD estándar de 0,35 μm. La foto del chip del regulador fabricado se muestra en la Fig. 9, cuya área de núcleo activo del VR es 290 μm × 900 μm.

La foto de chip de la realidad virtual propuesta

El voltaje de salida regulado del VR propuesto es de 5 V con el voltaje de la fuente de alimentación entre 5,5 y 30 V. El condensador de salida es un condensador cerámico de bajo costo. La capacitancia del condensador de salida se puede establecer entre 100 nF y 3,3 μF.

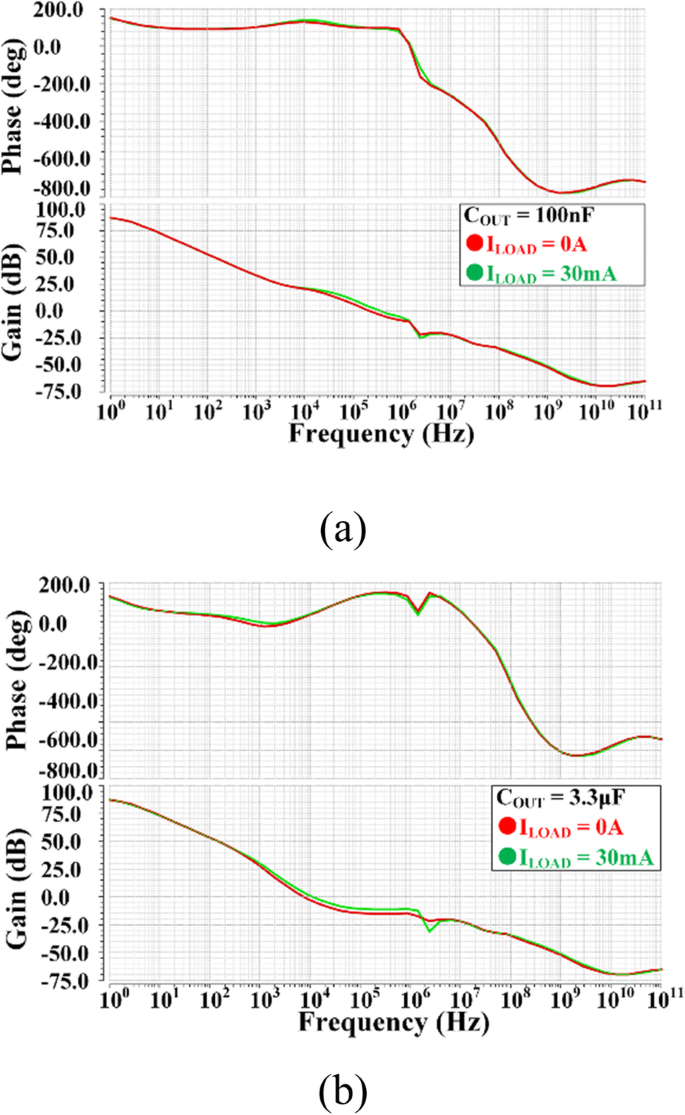

La Figura 10 demuestra la respuesta de frecuencia del VR propuesto en diferentes condiciones de carga con un capacitor de salida de 100 nF y 3.3 μF. El LDO propuesto puede mantenerse estable en una amplia gama de valores de capacitores de salida, y la forma de onda de la respuesta de frecuencia del bucle tiene una diferencia muy pequeña entre la corriente de carga de 0 y 30 mA, lo que se beneficia del DLT propuesto analizado anteriormente.

Respuestas de frecuencia de bucle de la realidad virtual propuesta con un valor diferente de I Cargar y C FUERA condiciones. un C FUERA =100 nF, b C FUERA =3.3 훍 F. La línea roja y verde representa I Cargar de 0 A y 30 mA, respectivamente

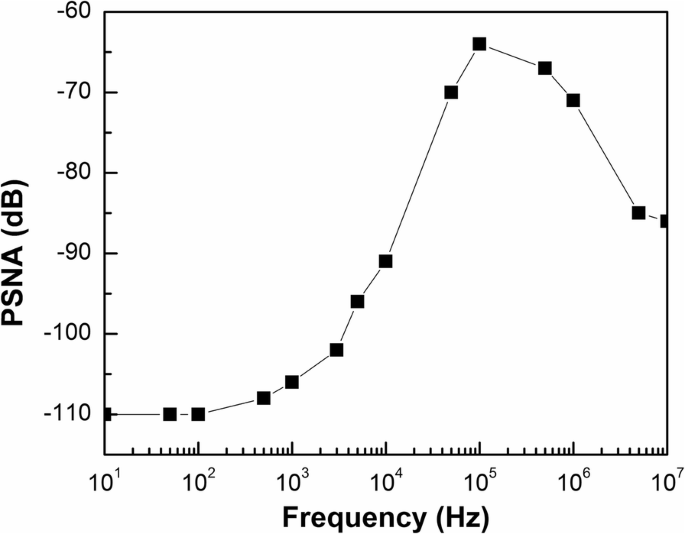

El resultado de la verificación de PSR con un condensador de salida de 0,1 μF se muestra en la Fig. 11, donde se logra un - 110 dB a baja frecuencia y mejor que - 64 dB hasta 10 MHz. A baja frecuencia, el VR propuesto tiene un buen PSR debido a la alta ganancia de bucle. El PSR se vuelve pobre dentro de la frecuencia de ganancia unitaria debido al polo dominado ω p . El condensador de salida C FUERA mejora la característica de PSR a alta frecuencia. Esos resultados muestran que es consistente con el análisis anterior, y la VR propuesta obtiene un mejor PSR en el rango de frecuencia completo.

PSR de la RV propuesta

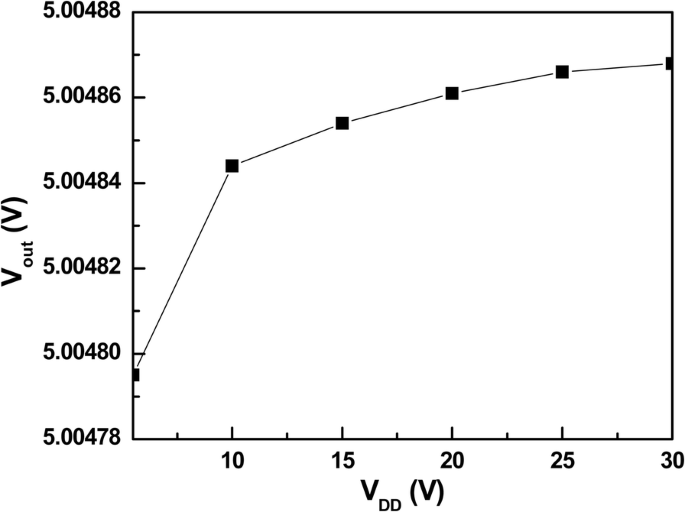

El resultado de la regulación de línea del VR propuesto se muestra en la Fig. 12. En el rango de voltaje de entrada de 5,5 a 30 V, el voltaje de salida solo varía 73,53 μV, lo que da como resultado una regulación de línea de solo 2,98 μV / V. Esto confirma la eficacia del SPT propuesto.

Regulación de línea de VR propuesta

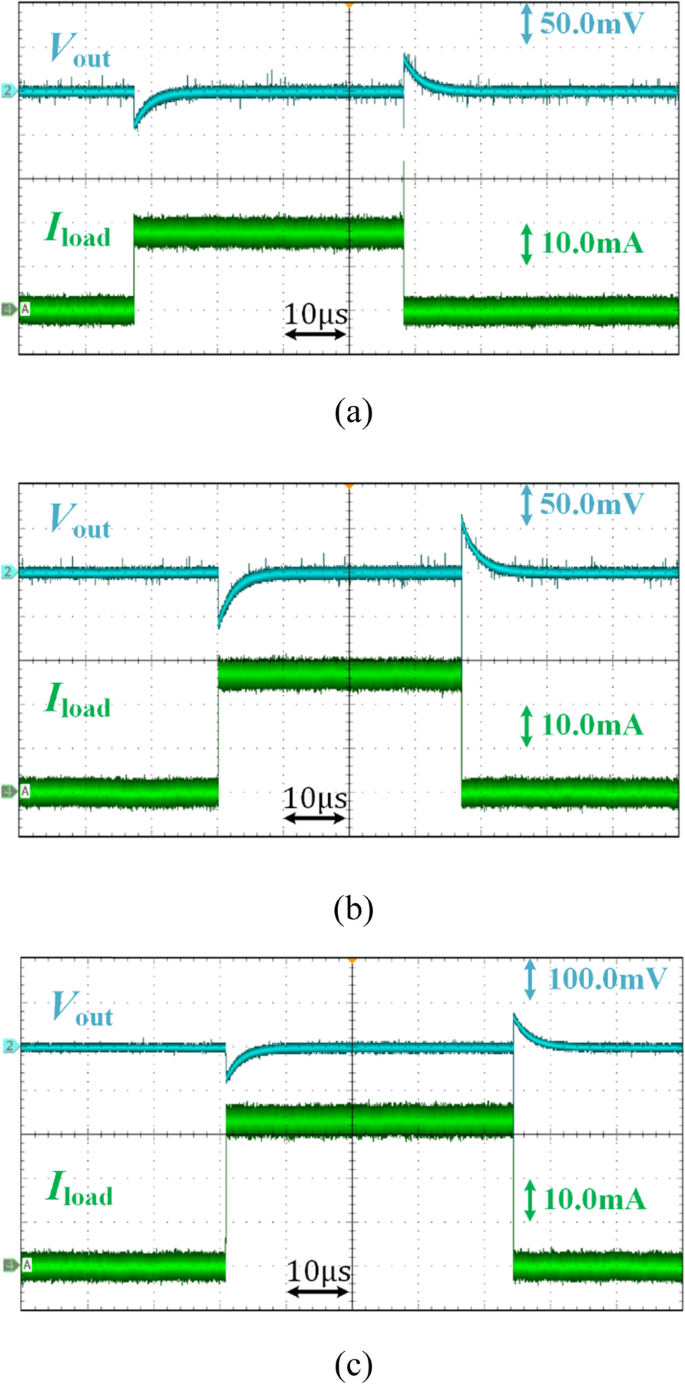

La Figura 13 muestra la respuesta transitoria del voltaje de salida debido a diferentes corrientes de carga. El pico de voltaje y la caída del voltaje de salida regulado es de aproximadamente 43 mV, 65 mV, 83 mV cuando la corriente de carga cambia de 0 a 18 mA, 28 mA y 32 mA, respectivamente. Esto da como resultado una regulación de carga de 0.233 mV / mA, que es causada principalmente por R 0 para la estabilidad con una amplia gama de capacitancia de salida.

Forma de onda de respuesta transitoria del VR propuesto debido a un paso de corriente de carga diferente. un 0 a 18 mA; b 0 a 28 mA; c 0 a 32 mA

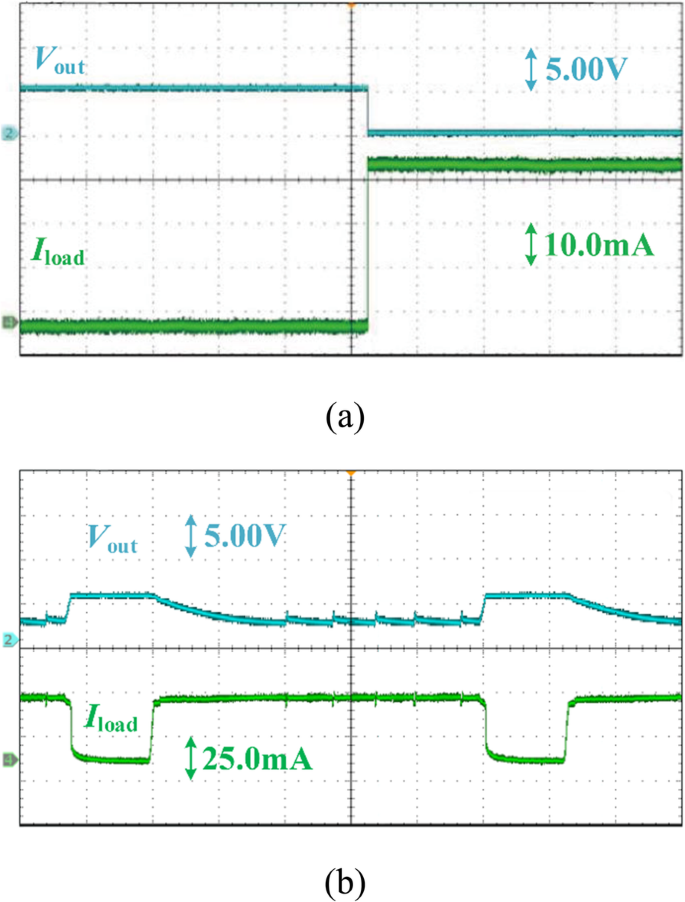

El OCP medido se muestra en la Fig. 14. Para verificar la efectividad del OCP, se adopta un cortocircuito en la Fig. 14a. Como se muestra en la Fig. 14a, cuando se produce la sobrecorriente con el voltaje de salida que se lleva a tierra, la corriente de salida del VR propuesto se mantiene en alrededor de 40 mA. La Figura 14b ilustra una respuesta transitoria entre la sobrecorriente y la carga normal, lo que indica que el VR propuesto tiene la capacidad de recuperación automática cuando la sobrecarga sale.

La medición de OCP de la VR propuesta. un cortocircuito de salida; b transitorio entre sobrecorriente y carga normal

La Tabla 1 proporciona una comparación de rendimiento del LDO propuesto y algunos otros LDO publicados anteriormente. En comparación, este LDO tiene la mejor regulación de línea y PSR, que se beneficia del SPT propuesto. El área activa se reducirá aún más si se fabrica en un proceso más avanzado.

La Tabla 2 proporciona otra comparación de rendimiento que se centra en los LDO que también tienen un amplio rango de suministro de energía. Con la ayuda de los DLT y SPT propuestos, este trabajo tiene la mejor regulación de línea y el rango de suministro de energía más amplio en comparación con otros LDO. La función OCP adicional hace que este trabajo sea más competitivo y confiable.

Conclusión

Un SPT VR de alta estabilidad con DLT y OCP se implementa en un proceso BCD estándar de 0,35 μm. Con la ayuda de SPT, la mayor parte del bucle de regulación es suministrado por un voltaje de salida regulado, que es beneficioso para la estabilidad y mejora de PSR. El DLT propuesto es útil para la respuesta y la estabilidad transitorias. Además, el circuito OCP integrado puede evitar que el VR presentado se dañe por sobrecarga o cortocircuito. La regulación lineal del VR propuesto es de 2,98 μV / V con VDD de 5,5 a 30 V mientras que la tensión de salida regulada es de 5 V, y la regulación de carga es de 0,233 mV / mA con corriente de carga de 0 A a 30 mA. El voltaje de sobreimpulso y subimpulso durante el cambio de corriente de carga también es pequeño al usar el circuito de mejora transitoria presentado. El PSR a baja frecuencia es - 110 dB, y es mejor que - 64 dB hasta 10 MHz. Se puede lograr una alta estabilidad de bucle en una amplia gama de condensadores de salida y corriente de carga y, por lo tanto, el VR propuesto es adecuado para aplicaciones que requieren alto rendimiento y confiabilidad bajo variaciones del condensador de salida y la corriente de carga.

Disponibilidad de datos y materiales

Todos los datos generados o analizados durante este estudio se incluyen en este artículo publicado.

Abreviaturas

- VR:

-

Voltage regulator

- OCP:

-

Overcurrent protection

- SPT:

-

Self-power technique

- PSR:

-

Power supply rejection

- DLT:

-

Dynamic load technique

- EA:

-

Error amplifier

Nanomateriales

- Regulador de voltaje

- Leyes y ecuaciones del circuito de CC

- Circuitos de verano y promedios

- Voltaje y corriente

- Condensadores y cálculo

- Cálculos complejos de voltaje y corriente

- Algunos ejemplos con circuitos de CA

- Maxim:transceptor IO-Link dual con regulador DC-DC y protección contra sobretensiones

- ST:regulador de conmutación con amplios rangos de voltaje

- Liderando con persistencia y perseverancia

- 5 pasos para reinventar la arquitectura operativa y mejorar los resultados con IoT