FET ferroeléctricos con aisladores incrustados de nanocristales (NEI) para dispositivos de capacitancia negativa y aplicaciones de memoria no volátil

Resumen

Presentamos un nuevo transistor de efecto de campo ferroeléctrico (FeFET) con aislante incrustado de nanocristales (NEI) con una capa aislante unificada-ferroeléctrica / dieléctrica (FE / DE) muy delgada, que es prometedora para la lógica de bajo voltaje y la memoria no volátil ( NVM) aplicaciones. La naturaleza ferroeléctrica de las capas de NEI que comprenden ZrO 2 ortorrómbico nanocristales incrustados en Al 2 amorfo O 3 se prueba mediante mediciones de voltaje de polarización, microscopía de fuerza de respuesta piezoeléctrica y mediciones eléctricas. Se investigan el rendimiento dependiente de la temperatura y el comportamiento de resistencia de un FET de capacitancia negativa NEI (NCFET). Un FeFET con FE / DE de 3,6 nm de grosor logra una ventana de memoria superior a 1 V, allanando un camino para el escalado definitivo del grosor de FE para permitir FeFET tridimensionales con un paso de aleta muy pequeño.

Antecedentes

Los transistores de efecto de campo con una capa aislante de puerta ferroeléctrica (FeFET) han atraído un interés considerable para una variedad de aplicaciones de circuitos integrados. Debido a sus propiedades inherentes de capacitancia negativa (NC), un FeFET puede lograr un comportamiento de conmutación más pronunciado que un MOSFET convencional, lo que permite una operación de voltaje más bajo [1]. Varias estructuras de canal [2, 3, 4] y materiales [5, 6, 7] han obtenido una oscilación subumbral (SS) por debajo de 60 mV / década. Además, histéresis en la corriente-voltaje ( I - V ) característica debida a la polarización remanente ( P r ) se puede utilizar para la aplicación de memoria no volátil (NVM) [8]. El desarrollo de materiales para FeFET se ha centrado recientemente en HfO 2 dopado policristalino debido a su mejor escalabilidad de espesores [9] y compatibilidad con procesos CMOS [2]. Sin embargo, todavía existe un límite fundamental para HfO 2 escala de espesor para evitar corrientes de fuga de puerta no deseadas; esto a su vez limita el FinFET [2]. Inspirado en el concepto de dispositivo de memoria y MOS de nanocristales [10, 11], en este trabajo se presenta una capa dieléctrica (DE) aislante con nanocristales ferroeléctricos (FE) incrustados. El nuevo diseño de dispositivo resultante ilustrado en la Fig. 1 se denomina FeFET “Aislador incrustado de nanocristales” (NEI). La principal ventaja de este diseño es una capa de FE / DE unificada más delgada que cumple con el requisito de fuga de puerta baja.

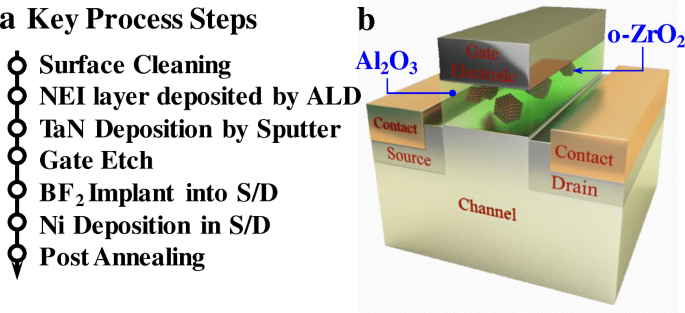

un Pasos clave del proceso para la fabricación de transistores de efecto de campo ferroeléctricos NEI. b Esquema 3D del NEI FeFET

En este trabajo, se informan los NEI FeFET. Se caracterizan las propiedades físicas y ferroelectricidad de las capas de NEI con diferentes espesores físicos. El rendimiento eléctrico de los NEI FeFET se investiga para aplicaciones de NVM y lógica de bajo voltaje.

Métodos

Los pasos clave del proceso para la fabricación de NEI FeFET se muestran en la Fig. 1a. Se utilizaron obleas de Ge (001) tipo n de cuatro pulgadas con una resistividad de 0.088-0.14 Ω cm como sustratos de partida. Después de la limpieza previa a la compuerta con HF diluido, se cargaron obleas de Ge (001) en una cámara de deposición de capa atómica (ALD) para la deposición de la capa de NEI que comprende ZrO 2 nanocristales incrustados en Al 2 amorfo O 3 matriz. En este trabajo se utilizaron capas de NEI con los distintos espesores. La puerta de metal TaN se depositó sobre los NEI FeFET utilizando la pulverización catódica reactiva. Después del modelado y grabado de la puerta, BF 2 + Los iones se implantaron en las regiones de origen / drenaje a una energía de 20 keV y una dosis de 1 × 15 cm −2 . Se depositó níquel (Ni) de treinta nanómetros en las regiones de fuente / drenaje utilizando el proceso de despegue. Finalmente, la fabricación del dispositivo se completó con un recocido térmico rápido (RTA). Controle los transistores de efecto de campo semiconductores de óxido metálico (MOSFET) con un Al 2 puramente dieléctrico O 3 También se fabricó la capa aislante de la puerta.

La Figura 1b muestra el esquema en 3D del NEI FeFET fabricado, que comprende nanocristales FE incrustados en una capa aislante de puerta DE amorfa. Aunque el volumen de material FE es pequeño, es suficiente para aplicaciones NCFET y NVM. El material aislante DE es clave para lograr una fuga de puerta baja y un voltaje de funcionamiento bajo; debe tener una gran energía de banda prohibida y una alta permitividad dieléctrica ( κ ). También debe prever un campo altamente coercitivo ( E c ) de los nanocristales de FE incrustados.

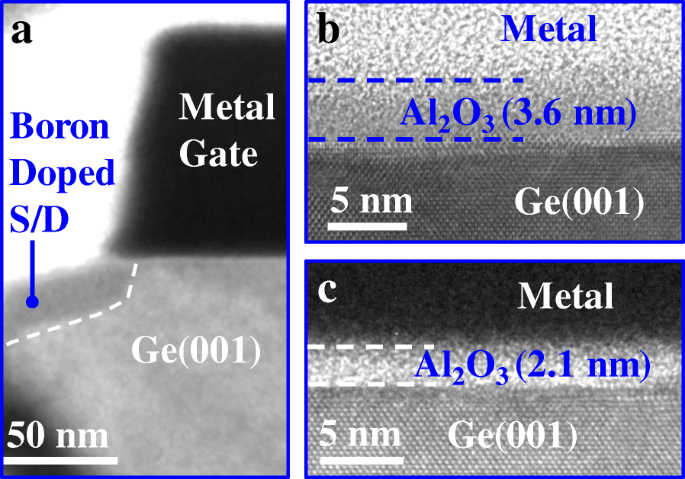

La imagen del microscopio electrónico de transmisión de sección transversal (XTEM) de la Fig. 2a muestra las regiones de fuente / drenaje, canal y borde de puerta de un FeFET fabricado. Las Figuras 2b yc indican que los espesores de las capas NEI estudiadas en este trabajo son de 3,6 y 2,1 nm, respectivamente. Tenga en cuenta que una capa interfacial de GeO x existe entre la capa NEI y Ge, aunque no se puede ver.

un Imagen XTEM que muestra las regiones de puerta, canal y fuente / drenaje de NEI-FeFET. b y c Imágenes XTEM de pila de puertas de FeFET con capas NEI de 3,6 y 2,1 nm de grosor, respectivamente

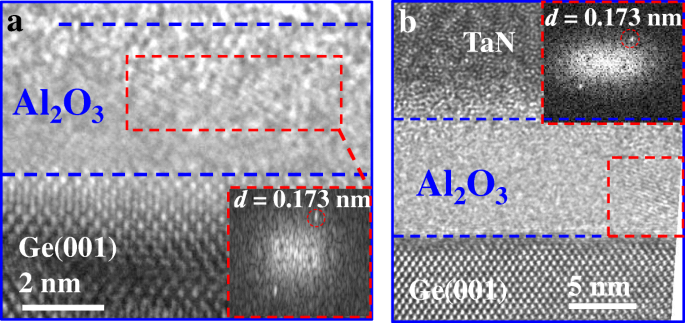

Las imágenes TEM de alta resolución (HRTEM) en la Fig.3 demuestran el ZrO 2 nanocristales incrustados en Al 2 amorfo O 3 sobre Ge (001) en las muestras NEI con espesores de 3,6 y 6 nm. En nuestro trabajo anterior, hemos demostrado que el porcentaje atómico de Zr en la capa NEI es inferior al 0,5% [12]. Según los patrones de difracción, el espaciado interplanar d dentro de los nanocristales se calcula que es de 0,173 nm, que corresponde a ZrO 2 ortorrómbico orientado (111) fase [13].

Imágenes HRTEM que muestran nanocristales incrustados en Al 2 amorfo O 3 para las muestras con espesores de a 3.6 nm y b 6 nm. Los recuadros muestran que el espaciado interplanar d en el nanocristal es de 0,173 nm, correspondiente a o-ZrO 2 (111) fase

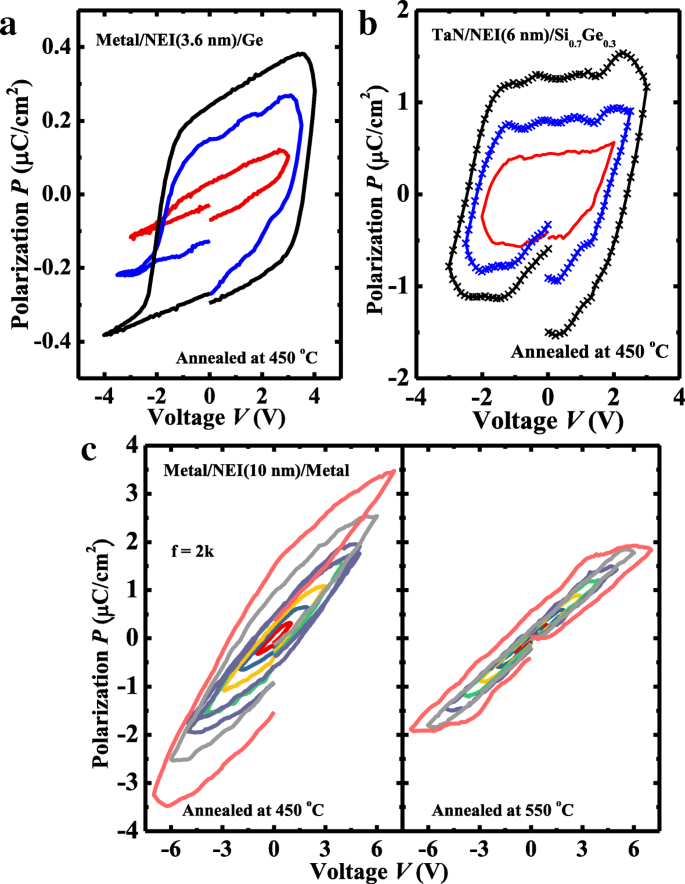

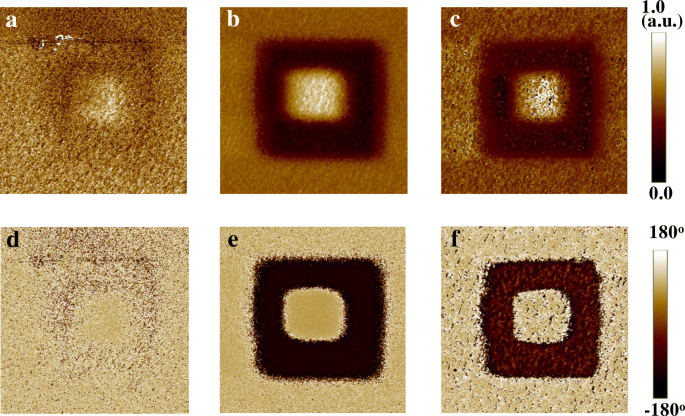

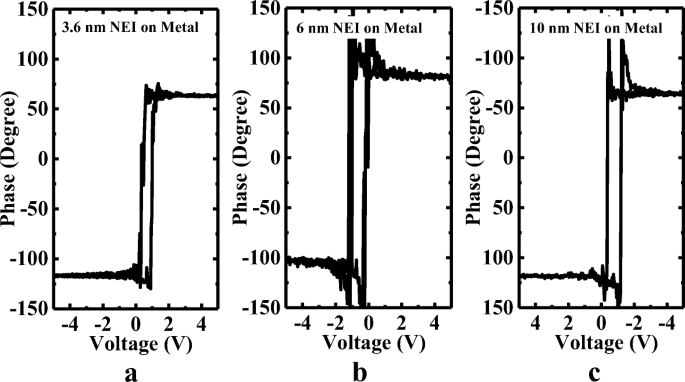

Polarización frente a voltaje ( P - V ) y microscopía de fuerza de respuesta piezoeléctrica (PFM) se llevaron a cabo en las muestras de NEI con los diferentes espesores. Para caracterizar la ferroelectricidad de la capa NEI, P - V curvas de TaN / NEI (3,6 nm) / Ge, TaN / NEI (6 nm) / Si 0,7 Ge 0.3 , y los condensadores TaN / NEI (10 nm) / TaN se muestran en la Fig. 4a, byc, respectivamente. La capa NEI exhibe una P más baja que los valores informados de HfZrO 2 (HZO) [14], que se debe al hecho de que la relación de volumen de ZrO 2 nanocristal en Al 2 O 3 la matriz es bastante baja. Se ve que la polarización remanente P r de la película NEI aumenta con el aumento del espesor de la película. P-V Las curvas de la Fig. 4c indican que la ferroelectricidad de la capa de NEI se degenera mientras que la temperatura de recocido aumenta de 450 a 550 ° C. Cabe señalar que el motivo de la P-V no cerrada bucles se debe a que efectivamente existe una fuga. Se informó que la compensación resultante en el campo eléctrico cero disminuye a medida que se reduce el rango de barrido de voltaje [3, 15, 16]. Se midieron las imágenes de amplitud (superior) y fase (inferior) de NEI de 3,6 nm, 6 nm y 10 nm, como se muestra en la Fig. 5a, byc, respectivamente. Como se muestra en la Fig. 6, los patrones que indican la polaridad opuesta escritos en la superficie de NEI en TaN exhiben un contraste más claro con el aumento del espesor de la película.

un - c P medido - V curvas de TaN / NEI (3,6 nm) / Ge, TaN / NEI (6 nm) / Si 0,7 Ge 0.3 y TaN / NEI (10 nm) / TaN, respectivamente

un - c Imágenes de amplitud (superior) y fase (inferior) de la medición de PFM para NEI de 3,6, 6 y 10 nm en TaN, respectivamente

un - c Características de cambio de fase de NEI de 3,6, 6 y 10 nm en TaN, respectivamente. Se observa que se puede escribir polaridad opuesta en la superficie de la capa NEI

Resultados y discusión

NEI NCFET

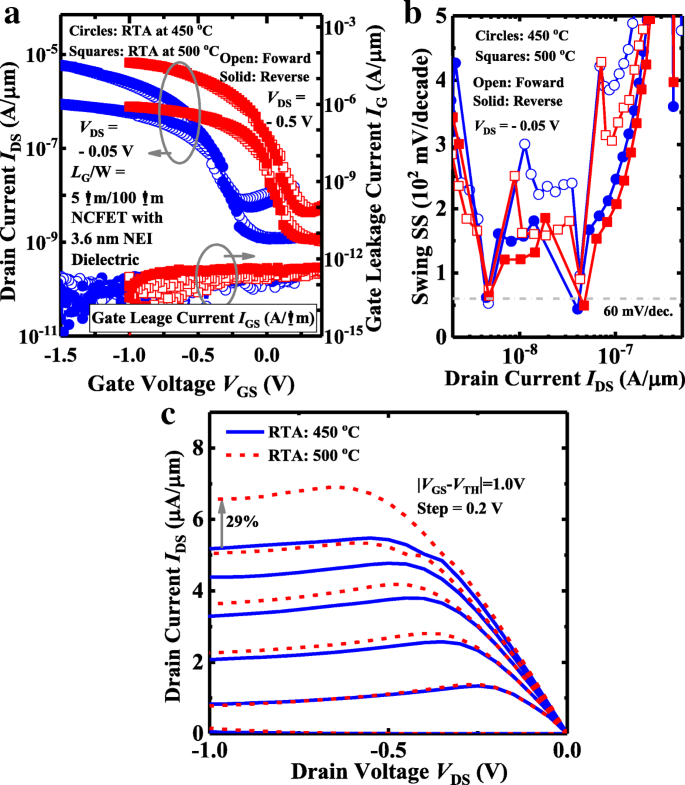

La figura 7a muestra I medido DS - V GS curvas de los NEI NCFET con un espesor NEI de 3,6 nm recocido a 450 ° C y 500 ° C. Los NCFET exhiben poca histéresis que indica la buena correspondencia entre la capacitancia ferroeléctrica y la capacitancia MOS en los transistores. Los NCFET muestran el efecto NC inducido en el sentido de las agujas del reloj I-V bucles, lo que contrasta con los de sentido contrario a las agujas del reloj mediante la captura / eliminación de trampas de carga [17]. La fuga de la puerta I G en función de V GS del mismo par de dispositivos demuestra que la formación de nanocristales en Al 2 O 3 no aumenta la fuga de la puerta. La Figura 7b muestra que los NCFET alcanzan los puntos SS empinados por debajo de 60 mV / década para los barridos hacia adelante y hacia atrás. Las fluctuaciones SS en el NEI NCFET, también observadas en NC FinFETs [2, 18], podrían deberse al cambio de polarización de los diferentes nanocristales o dominios ferroeléctricos. El I medido DS - V DS Las curvas para el mismo par de dispositivos en la Fig. 7c muestran que en ∣ V GS - V TH ∣ =∣ V DS ∣ =1.0 V, el NCFET con RTA a 500 ° C logra un I un 29% más grande DS en comparación con el transistor recocido a 450 ° C. Esto se atribuye al hecho de que la movilidad del portador en el canal y las características de resistencia de contacto pueden mejorarse con el aumento de la temperatura de recocido [19]. La característica típica inducida por la capa ferroeléctrica, la resistencia diferencial negativa (NDR), se observa en el I DS - V DS curvas para los NCFET recocidos a las diferentes temperaturas.

un Medido I DS - V GS y yo G - V GS curvas de NCFET con NEI de 3,6 nm recocido a 450 ° C y 500 ° C. b Los NEI NCFET tienen puntos por debajo de 60 mV / década para un V DS valor de - 0,05 V. c yo DS - V DS curvas para los NEI NCFET que muestran los obvios fenómenos NDR. El transistor NC recocido a 500 ° C alcanza un 29% I DS mejora en comparación con el dispositivo con RTA a 450 ° C con una tensión de alimentación de 1,0 V

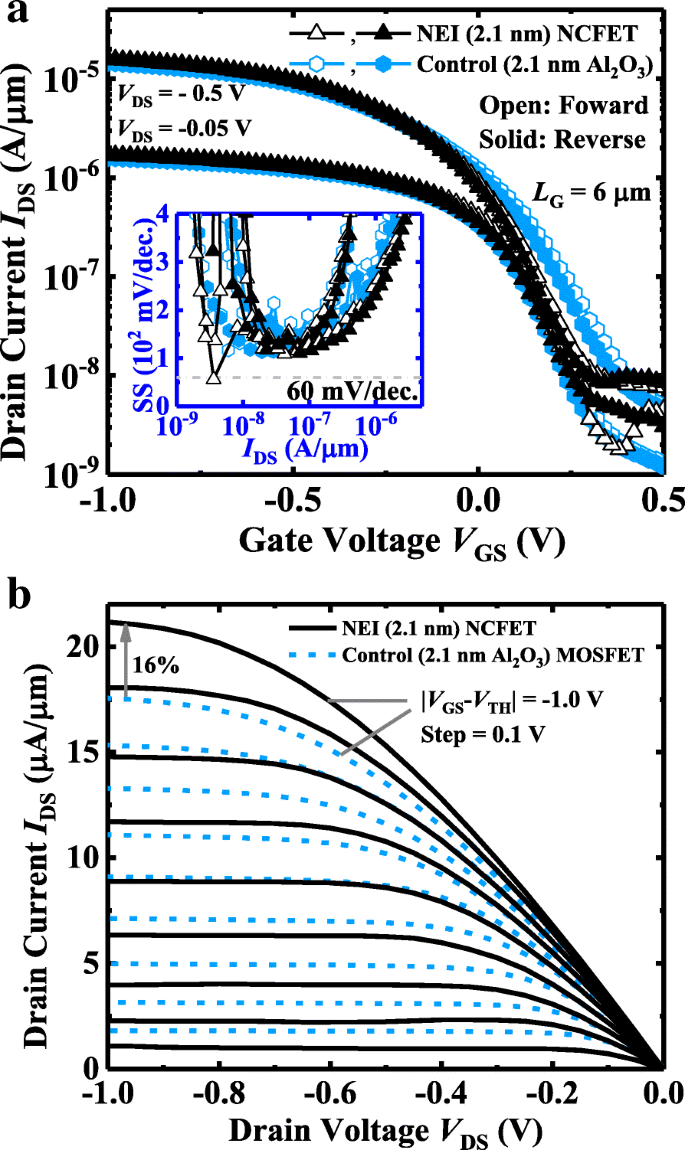

La figura 8a muestra I medido DS - V GS curvas de un NEI NCFET y un MOSFET de control con el mismo espesor de aislante de 2,1 nm. Los dispositivos tienen una L G de 6 μm. El NCFET presenta características sin histéresis. El recuadro muestra el punto SS frente a I DS curvas para los dispositivos, lo que demuestra que se logra una SS mejorada en el NCFET en comparación con el dispositivo de control, hasta el voltaje umbral. La Figura 8b muestra la I DS - V DS curvas del NEI NCFET y el control MOSFET. NCFET exhibe el fenómeno NDR para el bajo V GS . El efecto NDR corresponde a las características mejoradas de reducción de la barrera inducida por drenaje (DIBL) en NCFET en comparación con el MOSFET de control, como se muestra en la Fig. 8a. En ∣ V GS - V TH ∣ =∣ V DS ∣ =1.0 V, un 16% I DS La mejora se obtiene en NCFET en comparación con el dispositivo de control. NCFET con NEI de 2,1 nm tiene el NDR menos significativo en comparación con el transistor con NEI de 3,6 nm, lo cual es consistente con la conclusión en [20].

un yo DS - V GS curvas de un NEI NCFET y control MOSFET con Al 2 puro O 3 dieléctrico. Ambos dispositivos tienen el aislante de puerta de 2,1 nm. El recuadro muestra que el NCFET tiene un SS más pronunciado que el dispositivo de control hasta el voltaje de umbral. b Medido I DS - V DS curvas para NCFET y control MOSFET. Se observa NDR para NCFET a V muy bajo GS . En ∣ V GS - V TH ∣ =∣ V DS ∣ =1.0 V, NCFET alcanza un 16% I DS mejora en comparación con el dispositivo de control

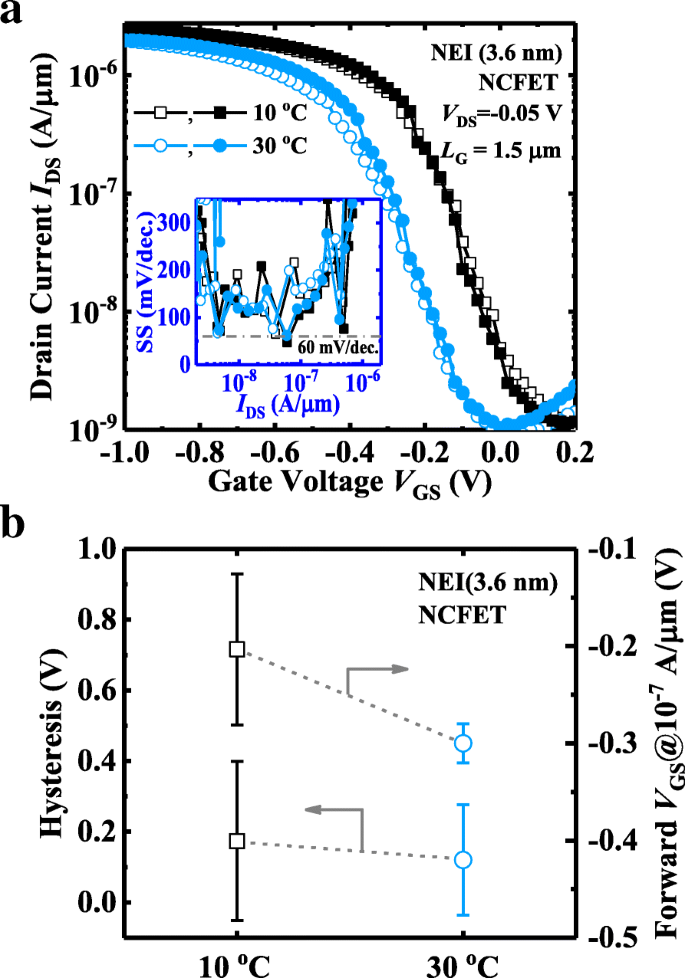

En este documento se investiga la dependencia de la temperatura del NCFET con el NEI de 3,6 nm de espesor. La figura 9a muestra I DS - V GS curvas medidas a 10 ° C y 30 ° C. El recuadro indica que el rendimiento SS del transistor no se degrada a temperaturas elevadas. A medida que aumenta la temperatura, el I - V la curva cambia a V más negativa GS debido al efecto dominante de la ferroelectricidad, que es opuesto a la tendencia de un MOSFET convencional. La Figura 9b resume los cambios en el voltaje de histéresis y el voltaje de umbral de conmutación hacia adelante con la temperatura. Adelante V GS cambia a valores más negativos a medida que aumenta la temperatura, lo que podría deberse a un aumento de E c del NEI.

un yo DS - V GS de un NEI (3,6 nm) NCFET medido a 10 ° C y 30 ° C. Las curvas muestran un cambio hacia un voltaje más negativo con el aumento de temperatura, como se esperaba. El recuadro muestra el punto empinado SS. b Gráficos estadísticos de histéresis (izquierda) y hacia adelante V GS @ 10 −7 A / μm (derecha) para NCFET con capa NEI de 3,6 nm. Adelante V GS cambia en la dirección negativa al aumentar la temperatura

NEI FeFET para aplicación de memoria no volátil

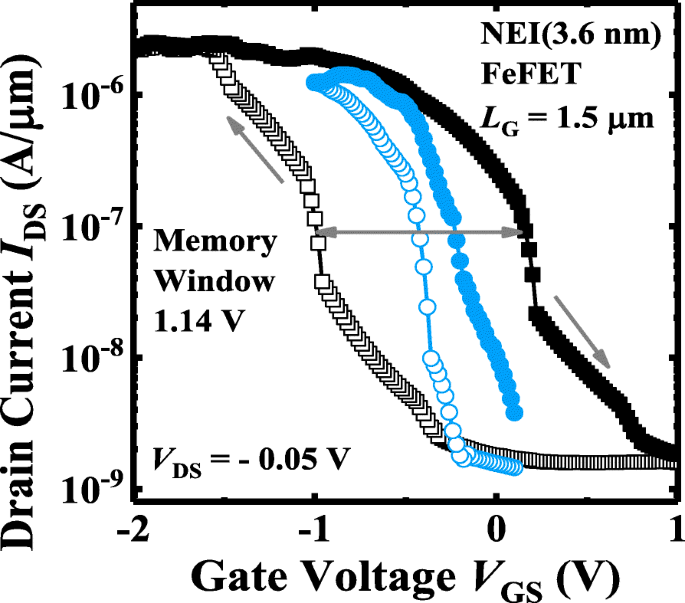

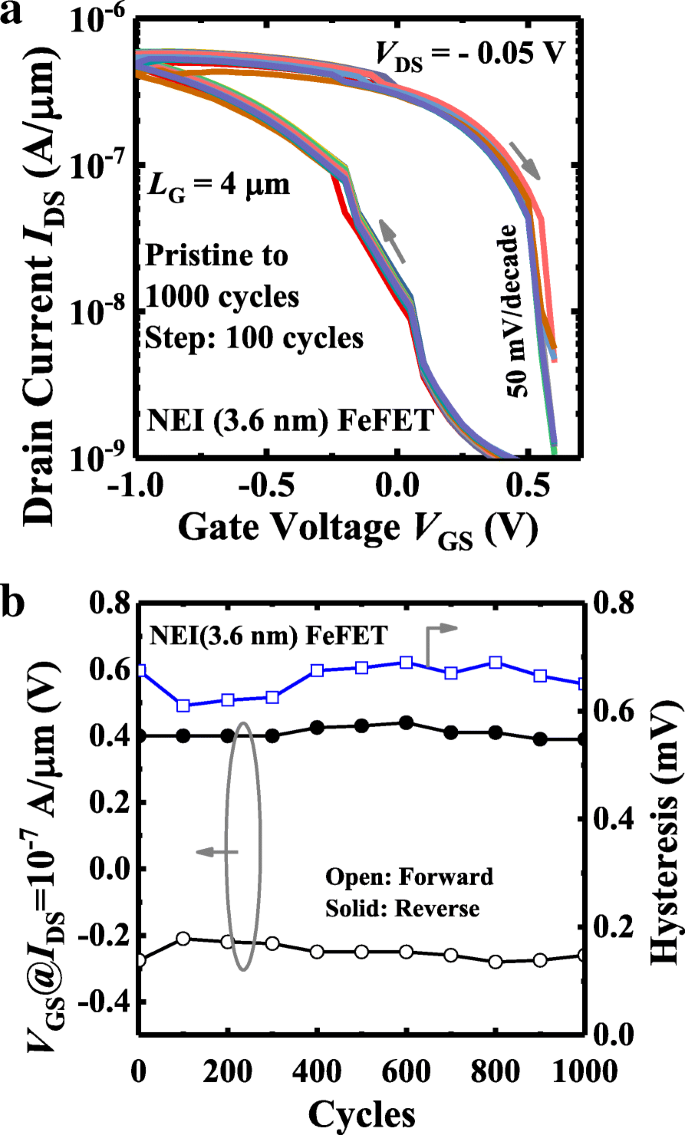

Al aumentar el rango de V GS barrido, el voltaje de histéresis de un NEI FeFET se puede aumentar para lograr una ventana de memoria grande y estable (MW) para operaciones de lectura y escritura. Como se muestra en la Fig.10, un FeFET con NEI de 3.6 nm demuestra que el MW aumenta de 0.2 a 1.14 V a medida que V GS El rango de barrido varía de (0,1 V, - 0,1 V) a (1 V, - 2 V). La resistencia de barrido de CC de otro dispositivo de memoria FeFET se muestra en la figura 11a, la figura 11b ilustra las características de histéresis en función del número de ciclos de barrido de CC. Estable I-V Se ve una ventana de histéresis de ~ 0,65 V.

Para una V grande GS Rango de barrido de CC, se observa un MW de 1,14 V para el NEI (3,6 nm) FeFET

un Medido I DS - V GS curvas para NEI (3,6 nm) FeFET, a través de 1000 ciclos de barrido de CC. b Las mediciones de resistencia de barrido de CC muestran que el NEI FeFET tiene un MW estable a través de 1000 ciclos

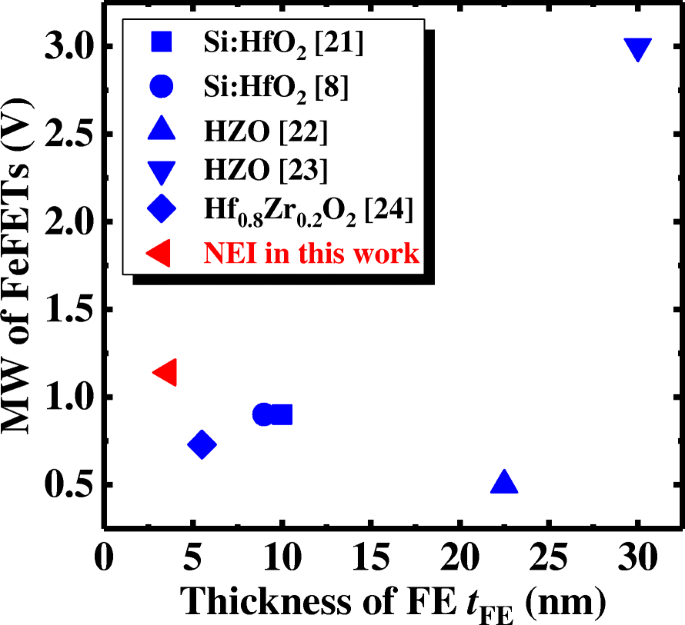

La Figura 12 compara el dispositivo de memoria NEI FeFET con los FeFET reportados, con respecto al espesor de capa de MW y FE [8, 21-24]. Cabe señalar que el dispositivo NEI FeFET en este trabajo logra un MW considerable (> 1 V) con el espesor de FE más delgado informado de 3.6 nm. Especulamos que es más fácil lograr la fase FE estable en NEI con un espesor menor, en comparación con el HfO dopado 2 [28,29,30].

Evaluación comparativa del dispositivo de memoria NEI FeFET frente a los FeFET informados, con respecto a MW y t FE . El FE más delgado se logra mediante el dispositivo de memoria NEI FeFET

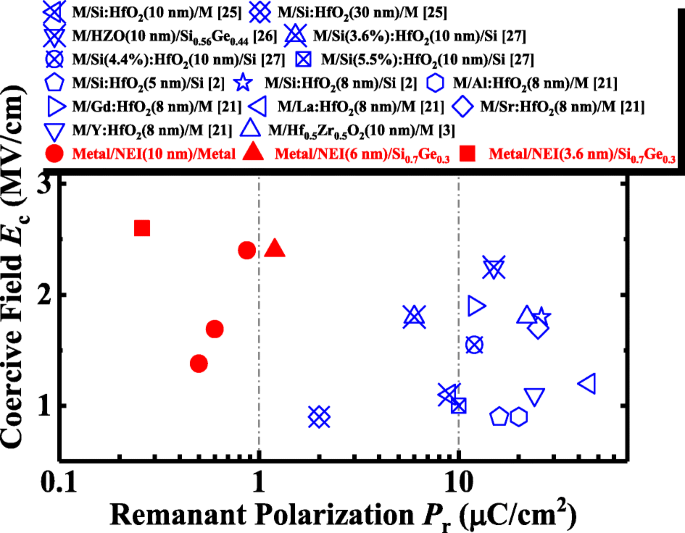

Finalmente, las ventajas del NEI FeFET proporcionadas por ZrO 2 Se discuten los nanocristales incrustados en un aislante de puerta amorfo. La Figura 13 compara la capa NEI con el HfO 2 dopado informado películas [2, 3, 21, 25-27], con respecto a E c y P r . NEI puede lograr un P mucho más bajo r en comparación con HfO 2 dopado para E similares c . Nuestros experimentos han demostrado que una P r por debajo de 1 μC / cm 2 puede proporcionar el MW requerido en los FeFET. La polarización excesiva podría conducir a una mayor despolarización, dando como resultado peores características de retención, que se informó en [25]. Además, las propiedades FE y DE de la capa NEI se pueden ajustar por separado: P r se mejora / reduce al aumentar / disminuir el volumen de nanocristales de FE, y κ aumenta al incorporar otros elementos en la matriz amorfa (por ejemplo, . , LaAlO 3 ), para optimizar el rendimiento de FeFET.

Evaluación comparativa de capas de NEI frente a HfO dopado 2 informado películas, con respecto a E c y P r . NEI logra una P mucho más baja r en comparación con HfO 2 dopado manteniendo similar E c. [2, 3, 21, 25, 26, 27]

Conclusiones

FeFET novedosos con ZrO 2 nanocristales incrustados en un Al 2 amorfo O 3 Se informa la capa aislante de la puerta. Los análisis físicos indican que menos del 0,5% de Zr en Al 2 O 3 produce suficiente ferroelectricidad para aplicaciones NCFET y NVM. Se observa un efecto NC estable a diferentes temperaturas de medición. Se demuestra el funcionamiento estable de la memoria FeFET con un aislador de compuerta extremadamente delgado (espesor total de 3.6 nm). El MW estable se alcanza en más de 1000 ciclos de resistencia de CC. El diseño propuesto de NEI FeFET proporciona un camino para reducir el grosor de la capa aislante de la compuerta FE / DE para que sea compatible con FinFET con pasos de aleta muy pequeños.

Abreviaturas

- Al 2 O 3 :

-

Óxido de aluminio

- ALD:

-

Deposición de la capa atómica

- BF 2 + :

-

Ión de fluoruro de boro

- DC:

-

Corriente continua

- Ec:

-

Campo coercitivo

- FeFET:

-

Transistor de efecto de campo ferroeléctrico

- Ge:

-

Germanio

- GeO x :

-

Óxido de germanio

- HF:

-

Ácido fluorhídrico

- HRTEM:

-

Microscopio electrónico de transmisión de alta resolución

- I DS :

-

Drenar corriente

- MOSFET:

-

Transistores de efecto de campo semiconductores de óxido metálico

- MW:

-

Ventana de memoria

- NC:

-

Capacitancia negativa

- NDR:

-

Resistencia diferencial negativa

- NEI:

-

Aislante-incrustado-de nanocristales

- Ni:

-

Níquel

- Pr:

-

Polarización remanente

- RTA:

-

Recocido térmico rápido

- SS:

-

Oscilación del subumbral

- TaN:

-

Nitruro de tantalio

- V GS :

-

Voltaje de puerta

- V TH :

-

Voltaje umbral

- ZrO 2 :

-

Dióxido de circonio

Nanomateriales

- Sensores y procesadores convergen para aplicaciones industriales

- Nanopartículas de oro multifuncionales para aplicaciones terapéuticas y diagnósticas mejoradas:una revisión

- Avances y desafíos de los nanomateriales fluorescentes para síntesis y aplicaciones biomédicas

- Tecnologías avanzadas de deposición de capas atómicas para micro-LED y VCSEL

- Compuestos de grafeno y polímeros para aplicaciones de supercapacitores:una revisión

- Evaluación de estructuras de grafeno / WO3 y grafeno / ceO x como electrodos para aplicaciones de supercondensadores

- Funciones duales del dispositivo V / SiOx / AlOy / p ++ Si como selector y memoria

- Efectos de las variaciones de grabado en la formación de canales Ge / Si y el rendimiento del dispositivo

- Accionamientos para refrigeración industrial y aplicaciones de refrigeración industrial

- Tornos giratorios para aplicaciones de taladrado y torneado

- Metales especiales para aplicaciones de dispositivos médicos