Velocidades del chip del procesador en memoria Cálculos de IA

Imec y GlobalFoundries han demostrado un chip de procesador en memoria que puede lograr una eficiencia energética de hasta 2900 TOPS / W, aproximadamente dos órdenes de magnitud por encima de los chips de procesador en memoria comerciales de la actualidad. El chip utiliza una idea establecida, la computación analógica, implementada en SRAM en la tecnología de proceso de silicio sobre aislante totalmente agotado (FD-SOI) de 22 nm de GlobalFoundries. El cómputo analógico en memoria (AiMC) de Imec estará disponible para los clientes de GlobalFoundries como una función que se puede implementar en la plataforma 22FDX de la empresa.

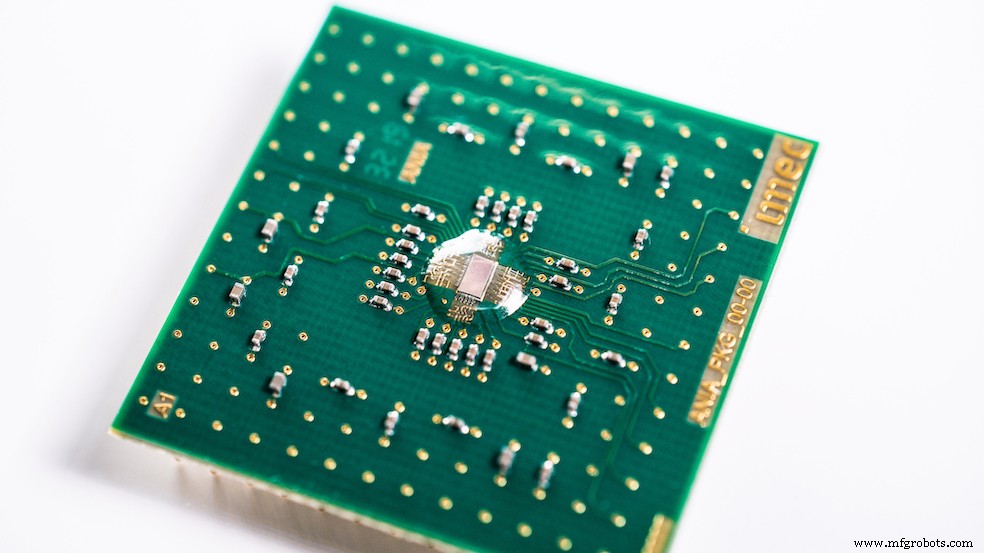

El chip de prueba AnIA de Imec, que se ve aquí montado en el PCB utilizado para la medición y caracterización, puede alcanzar hasta 2900 TOPS / W (Imagen:Imec)

Computación analógica

La computación analógica, o procesador en memoria, es una técnica establecida que ya se utiliza en chips aceleradores de IA comerciales de las startups Mythic, Syntiant, Gyrfalcon y otras.

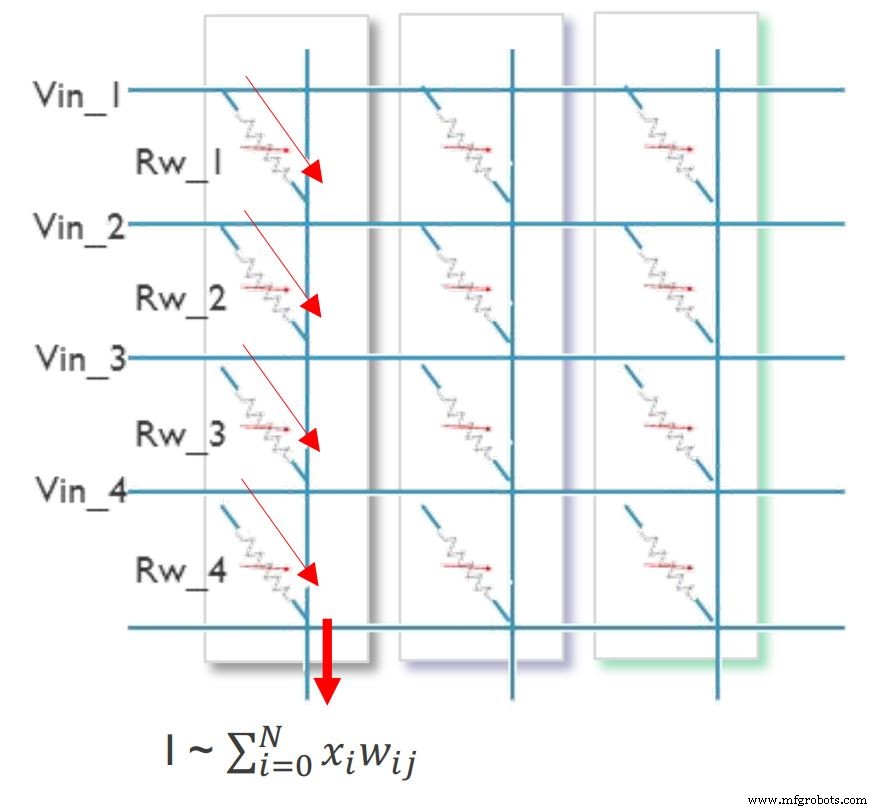

Dado que un modelo de red neuronal puede tener decenas o cientos de millones de pesos, el envío de datos entre la memoria y el procesador es ineficaz. La informática analógica utiliza una matriz de memoria para almacenar los pesos y también realizar operaciones de acumulación múltiple (MAC), por lo que no se necesita transferencia de memoria a procesador. Cada elemento de memristor (quizás una celda ReRAM) tiene su conductancia programada a un nivel analógico que es proporcional al peso requerido.

La aplicación de un voltaje proporcional a la activación de entrada (a través de la conversión de digital a analógico, a la izquierda del diagrama a continuación) significa que la corriente a través de cada elemento es proporcional al producto de la activación y el peso. La corriente a través de cada línea de bits vertical (líneas verticales en el diagrama a continuación) es la suma de estos productos de peso de activación, que se pueden alimentar a través de un convertidor de analógico a digital. Esta suma de los productos de peso de activación es fundamental para el cálculo de algoritmos de redes neuronales.

La computación analógica utiliza una matriz de celdas de memristor para calcular la multiplicación del vector de la matriz sin tener que enviar datos entre la memoria y el procesador (Imagen:Imec)

“En la práctica, son posibles muchas opciones además de ReRAM:podemos usar MRAM, Flash, DRAM… el objetivo de este programa es comprender cuál es la mejor para la aplicación y optimizar las opciones para cada dominio de aplicación”, explicó Diederik Verkest, programa director de aprendizaje automático en Imec.

Chip de prueba

Imec ha construido un chip de prueba, llamado acelerador de inferencia analógica (AnIA), basado en el proceso FD-SOI de 22 nm de GlobalFoundries. La matriz de 512k de celdas SRAM de AnIA más la infraestructura digital que incluye 1024 DAC y 512 ADC ocupa 4 mm 2 . Puede realizar alrededor de medio millón

Ioannis Papistas (Imagen:Imec)

cálculos por ciclo de operación basados en activaciones de entrada de 6 bits (bit de signo más), pesos ternarios (-1, 0, +1) y salidas de 6 bits.

"Podemos producir la salida de multiplicación de vectores de matriz a diferentes voltajes de suministro, 0,8 y 0,6 V", dijo Ioannis Papistas del grupo de aprendizaje automático de Imec. “Operar a voltajes de suministro más bajos sin afectar la precisión de la operación puede reducir significativamente el consumo de energía de la operación, lo cual es especialmente importante para la inferencia en sistemas con restricciones de energía. Esta es una característica importante de nuestro diseño, habilitada por el proceso 22FDX, que permite la inferencia competitiva en el borde ”.

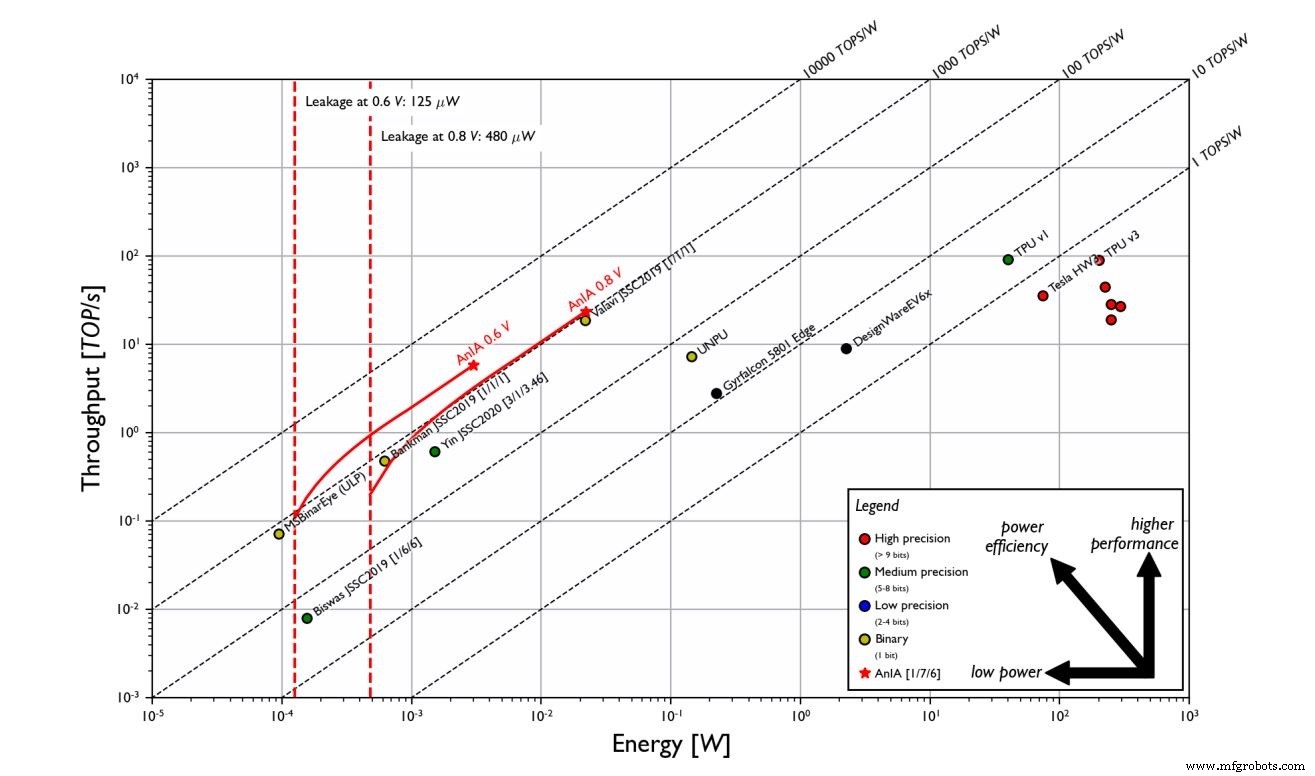

Imec mostró resultados de precisión para la inferencia de reconocimiento de objetos en el conjunto de datos CIFAR 10 que disminuyó solo un punto porcentual en comparación con una línea de base cuantificada de manera similar. Con una tensión de alimentación de 0,8 V, la eficiencia energética de AnIA está entre 1050 y 1500 TOPS / W a 23,5 TOPS. Para un voltaje de suministro de 0,6 V, AnIA alcanzó 5,8 TOPS a alrededor de 1800-2900 TOPS / W.

Eficiencia energética para varios aceleradores de IA en comparación con el chip de prueba AnIA de Imec (Haga clic para ampliar) (Imagen:Imec)

Innovación convencional

“La innovación [presentada por Imec] se convertirá en la corriente principal”, dijo Hiren Majmudar, vicepresidente y gerente general de la unidad de negocios de computación de GlobalFoundries. “Estamos viendo socios, clientes de GlobalFoundries que se encuentran en la etapa de postproducción con silicio validado ... esperamos que el silicio basado en computación analógica llegue a la producción a fines de este año o principios del próximo. En términos de la implementación del mercado masivo, anticipamos que la computación analógica comenzará a ingresar al mercado masivo ciertamente a más tardar en 2022. Pero potencialmente podría suceder antes que eso ”.

Diederik Verkest (Imagen:Imec)

GlobalFoundries está trabajando para incluir la tecnología AiMC de Imec como una característica que se puede implementar en la plataforma 22 FDX para habilitar aceleradores de IA energéticamente eficientes. El proceso FD-SOI está diseñado para un bajo consumo de energía, con la capacidad de operar hasta 0.5 V con 1 pico amperio por micrón para una fuga de espera ultra baja. 22FDX con la nueva función AiMC está en desarrollo en la línea de producción de 300 mm de GlobalFoundries en Fab 1 en Dresden, Alemania.

En cuanto a Imec, el programa de aprendizaje automático continuará. La ambición del grupo es llegar a 10,000 TOPS / W (10 TOPS por debajo de 100 mW) para sensores inteligentes siempre activos y dispositivos portátiles de consumo, dijo Verkest.

"En nuestro programa ML, nuestros próximos pasos son reducir el tamaño de estas celdas de cómputo y comenzar a considerar los dispositivos de memoria emergentes como una implementación de próxima generación para este principio", dijo.

>> Este artículo se publicó originalmente el nuestro sitio hermano, EE Times.

Incrustado

- Introducción a los circuitos integrados analógicos

- Circuitos computacionales

- Patatas fritas

- Diseñar con Bluetooth Mesh:¿Chip o módulo?

- La arquitectura del chip AI apunta al procesamiento de gráficos

- El pequeño módulo Bluetooth 5.0 integra una antena de chip

- Los investigadores crean una pequeña etiqueta de identificación de autenticación

- Se estrena el procesador de radar de imágenes automotrices de 30 fps

- El chip de radar de baja potencia utiliza redes neuronales con picos

- La placa del sensor inteligente acelera el desarrollo de la IA de borde

- Velocidades duraderas de UAV para la producción