La arquitectura híbrida acelera las cargas de trabajo de visión e inteligencia artificial

Un flujo de datos híbrido novedoso y una arquitectura de Von Neumann pueden acelerar las cargas de trabajo, incluidas subprogramas de redes neuronales, aprendizaje automático, visión por computadora, DSP y álgebra lineal básica.

Quadric, una startup de Silicon Valley, ha construido un acelerador diseñado para acelerar las cargas de trabajo de algoritmos de visión por computadora estándar y de inteligencia artificial para dispositivos periféricos como robots, automatización de fábricas e imágenes médicas. La arquitectura de hardware de la empresa es un flujo de datos híbrido novedoso y un diseño de Von Neumann que puede manejar cargas de trabajo que incluyen redes neuronales, aprendizaje automático, visión por computadora, DSP y subprogramas de álgebra lineal básica.

"Desde el principio, éramos muy conscientes de que la inteligencia artificial no es la única aplicación que se necesita para la computación en el dispositivo en dispositivos periféricos", dijo el director ejecutivo de Quadric, Veerbhan Kheterpal, a EE Times . “Los desarrolladores de estos productos necesitan que el sistema completo pueda ejecutar algoritmos informáticos clásicos de alto rendimiento, junto con IA. Esos son realmente los requisitos completos del sistema ".

Kheterpal enfatizó que la arquitectura no es una colección de aceleradores para cargas de trabajo individuales. Más bien, es una arquitectura unificada con un conjunto de instrucciones de datos paralelos diseñado para acelerar cargas de trabajo variadas, incluida la inferencia de IA.

“Donde la IA se está moviendo últimamente, hay algunas tendencias interesantes en cuanto a reemplazar capas enteras con una transformada rápida de Fourier (FFT)”, dijo Daniel Firu, director de producto de Quadric. Quadric se está posicionando para acelerar ese tipo de cargas de trabajo, citando un artículo reciente de Google en el que los investigadores aceleraron una red de transformadores reemplazando algunas capas con una FFT. Google reemplazó la subcapa de auto-atención de un codificador de transformador con una FFT para generar una red que logró una precisión del 92 por ciento en el punto de referencia BERT; el entrenamiento fue hasta siete veces más rápido en las GPU o el doble en las TPU de Google.

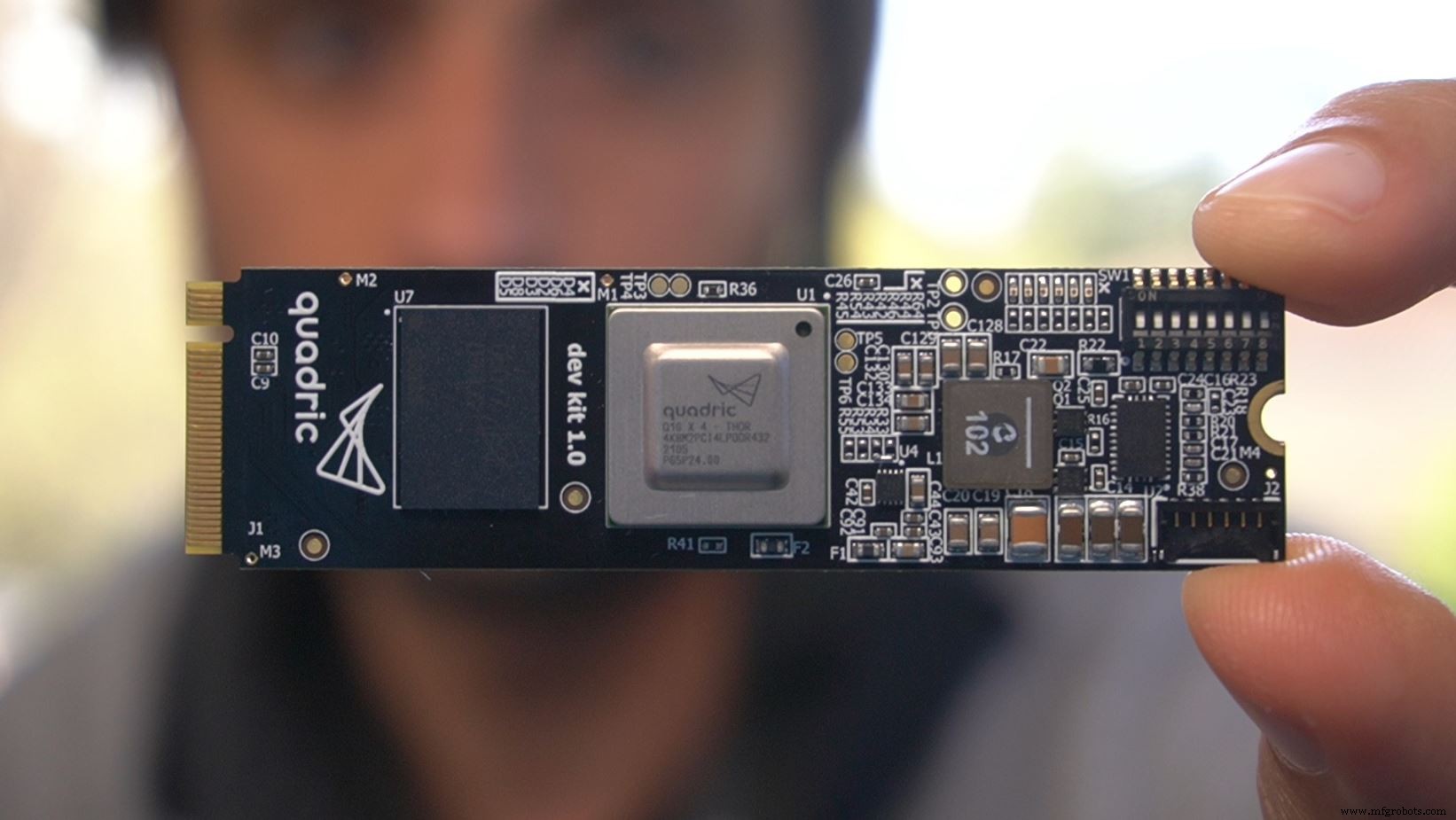

Kit de desarrollador de Quadric, una tarjeta M.2 con el procesador Q16 y 4 GB de memoria externa (Fuente:Quadric)

Robots de viñedos

Los tres cofundadores de Quadric, Veerbhan Kheterpal, Daniel Firu y Nigel Drego, fundaron anteriormente 21, una empresa minera de bitcoins que se vendió a Coinbase. Quadric, Burlingame, California, no comenzó diseñando chips. En cambio, originalmente construyó robots agrícolas que podían caminar arriba y abajo de los viñedos del valle de Napa mirando las vides y enviando alertas cuando veían fugas de riego o plagas.

Veerbhan Kheterpal (Fuente:Quadric)

“Cuando lo estábamos construyendo, nos dimos cuenta de que no iba a ser un producto viable construido a partir de la cadena de suministro de drones a un precio de $ 5 a $ 10,000”, dijo Kheterpal. “Tendría que fabricarse a partir de la cadena de suministro del tractor con un costo de 50.000 dólares y llevar PC grandes con GPU, con toneladas de cámaras. Fue entonces cuando nos propusimos buscar bajo el capó de todo ese software de robótica y descubrimos qué estaba causando fundamentalmente que esta necesidad de energía aumentara con plataformas como Nvidia e Intel ".

La empresa se centró en la construcción de un chip acelerador:"el chip que nos hubiera gustado tener", según Firu.

En 2017 se lanzó una ronda de financiación inicial, seguida de una ronda de la Serie A que generó $ 13 millones de clientes potenciales, incluido el inversor principal de Quadric, la automotriz japonesa Tier-One Denso. La financiación total de Quadric es de 18 millones de dólares.

Turing completo

Quadric emplea una arquitectura impulsada por instrucciones que toma elementos de arquitecturas de flujo de datos y los combina con elementos de una máquina Von Neumann. El objetivo es reemplazar sistemas heterogéneos en dispositivos de borde con algo menos complejo. Como máquinas completas de Turing, los núcleos Quadric Vortex ofrecen una combinación de aceleración con flexibilidad, afirma la compañía. La arquitectura es escalable en términos de matrices de núcleos y portátil hasta nodos de proceso avanzados (7 o 5 nm). Esto se adapta a aplicaciones de dispositivos periféricos con presupuestos de energía de aproximadamente cientos de milivatios a 20W.

El primer chip de la compañía, el Q16, es una matriz de núcleos Vortex de 16 x 16. Cada núcleo tiene la capacidad de realizar multiplicaciones de matrices y cálculos de IA, pero cada uno también tiene una ALU multifuncional, para operaciones como Y, O, reducción, desplazamiento y otras. El software permite a los desarrolladores expresar diversos tipos de algoritmos, incluidas las funciones de activación de LSTM y más. Las declaraciones If-Then-Else están disponibles en toda la matriz, lo que permite a los desarrolladores aprovechar la escasez de grano fino.

Cada núcleo de la matriz tiene acceso de ciclo único a sus núcleos vecinos, además de acceso de ciclo único a la memoria interna de 4 Kb. La memoria en chip también se incluye junto con la matriz, lo que brinda a los núcleos acceso determinista de baja latencia.

Los núcleos operan en paralelo en lo que Quadric llama una forma de “instrucción única, decodificación múltiple”; cada núcleo recibe la misma instrucción con cada ciclo. Pero según los datos dinámicos en tiempo de ejecución, cada núcleo puede interpretar esa instrucción de manera diferente. Eso permite que los núcleos, o grupos de núcleos, realicen funciones ligeramente diferentes.

También se incluye un bus de transmisión dedicado que optimiza el ancho de banda en la matriz y se puede usar para transmitir constantes, como pesos de redes neuronales, en todos los núcleos a la vez (Firu dijo que muchos algoritmos de visión por computadora también tienen información invariante de bucle que puede ser mapeado en el autobús).

La información dinámica ingresa a la matriz a través de unidades de almacenamiento de carga estáticas controladas por software que permiten tiempos de ejecución deterministas del kernel. El dispositivo permite la carga y el almacenamiento simultáneos desde dos bordes cualesquiera de un dispositivo, además de una propiedad especial desde un borde que se puede utilizar para enviar pesos de redes neuronales:cargar desde dos bordes y almacenar desde un tercer borde simultáneamente puede reducir los tiempos de ejecución de la ejecución de cómputo.

Daniel Firu (Fuente:Quadric)

"Puede cargar en un lado y luego almacenar desde un lado perpendicular", dijo Firu. “Eso permite que sucedan algunas cosas bastante interesantes a nivel de software. También puede comenzar a hacer cosas como reasignaciones de datos y rotaciones de imágenes y cosas así usando este paradigma ”.

Mientras tanto, las memorias estáticas controladas por software (no la caché) en el chip ofrecen espacio para grandes estructuras de datos. Quadric permite el acceso de API a estos para que los desarrolladores puedan definir estructuras de datos arbitrarias en su interior. En el chip Q16, las memorias son de 8 GB, suficiente para caber "dos o tres búferes de fotogramas en HD, o una red neuronal completa de pesos", dijo Firu.

Pila de software

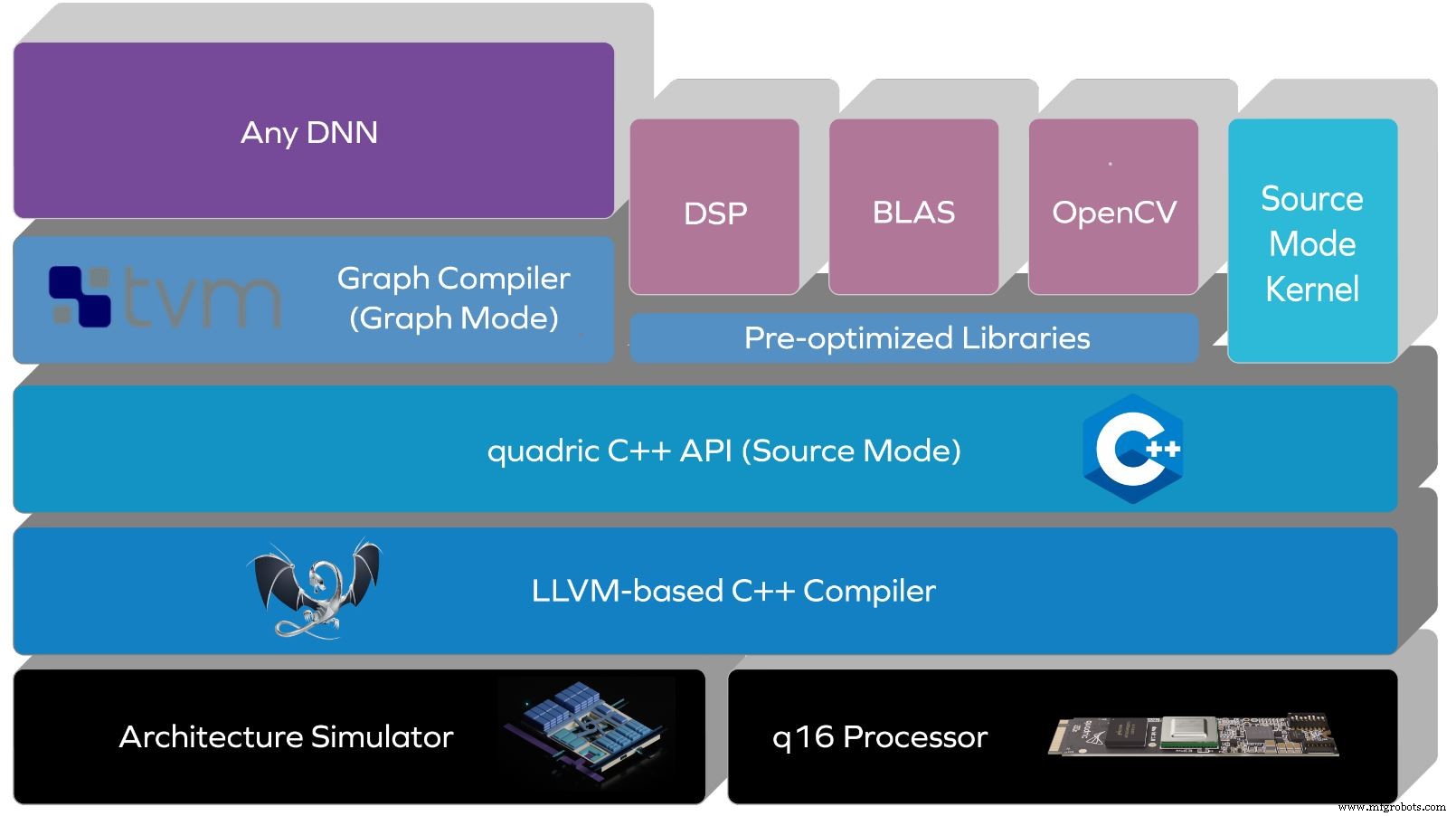

Quadric construyó su pila de software antes que el silicio. Los clientes lo han estado usando con el simulador de arquitectura de la empresa, o con FPGA, durante un año, dijo Kheterpal. La pila de Quadric abstrae la arquitectura y el conjunto de instrucciones a través de un compilador basado en LLVM, con una API de C ++ en la parte superior.

El modo de origen admite diferentes algoritmos de datos en paralelo con control C ++ a nivel de origen de las características arquitectónicas del procesador. A medida que las redes neuronales se vuelven más complejas, el modo de origen también permite a los desarrolladores expresar operaciones personalizadas.

Pila de software de Quadric (fuente:Quadric)

Una actualización futura de la pila ofrecerá un modo gráfico sin código, que admitirá las versiones de redes neuronales TensorFlow u ONNX. Eso incluirá un compilador de red neuronal profunda (DNN) basado en TVM que genera código automáticamente.

"Estamos combinando el poder de la ausencia de código con la flexibilidad de tener su propio código personalizado y combinarlos de formas interesantes para lograr su aplicación", dijo Kheterpal. “La mayoría de las plataformas solo ofrecerán una arquitectura específica de IA con algún tipo de compilador DNN, pero ¿qué pasa con la personalización? ¿Qué pasa con un DNN que no es compatible? ¿Qué pasa con los operadores que no son compatibles? No tenemos esas restricciones porque este es un núcleo completo de Turing, los núcleos pueden realizar cualquier operación. La flexibilidad del código brinda a los desarrolladores la capacidad de escribir cualquier algoritmo que deseen ”.

Hoja de ruta de chips

El chip Q16 de Quadric, que cuenta con 256 núcleos Vortex en una matriz de 16 x 16 en silicio de 16 nm, ofrece 4 INT8 DNN TOPS. Puede ejecutar ResNet-50 a 200 inferencias por segundo (para parámetros INT8 a un tamaño de imagen de 224 x 224), consumiendo un promedio de 2W.

La hoja de ruta de Quadric incluye una segunda generación de la arquitectura, más una salida de cinta de un chip Q32 (una matriz de 1.000 núcleos), "probablemente en 7 nm", dijo Firu. Si bien el Q16 es estrictamente un acelerador (se ubicaría junto a un procesador host del sistema), el Q32 en desarrollo también puede incluir núcleos Arm o RISC-V para actuar como host.

Ya está disponible un kit de desarrollador de formato M.2, con un procesador Q16 junto con 4 GB de memoria externa directamente asignados al espacio de memoria universal del Q16.

>> Este artículo se publicó originalmente en nuestro sitio hermano, EE. Tiempos.

Contenidos relacionados:

- Los aceleradores de hardware sirven aplicaciones de inteligencia artificial

- Cuando un DSP supera a un acelerador de hardware

- Una guía para acelerar las aplicaciones con las instrucciones personalizadas adecuadas de RISC-V

- El rendimiento del chip de inferencia se basa en el diseño optimizado del subsistema de memoria

- Los nuevos módulos de aceleración de IA mejoran el rendimiento del borde

- Edge AI desafía la tecnología de la memoria

Para obtener más información sobre Embedded, suscríbase al boletín informativo semanal por correo electrónico de Embedded.

Incrustado

- Entornos de nube híbrida:una guía de las mejores aplicaciones, cargas de trabajo y estrategias

- La arquitectura del chip AI apunta al procesamiento de gráficos

- La MCU inalámbrica presenta una arquitectura de doble núcleo

- Los procesadores especializados aceleran las cargas de trabajo de AI de punto final

- El diseño de referencia admite cargas de trabajo de IA que consumen mucha memoria

- La placa del sensor inteligente acelera el desarrollo de la IA de borde

- La cámara inteligente ofrece inteligencia artificial de borde de visión artificial de borde llave en mano

- IBM presenta una arquitectura de cadena de bloques híbrida para Internet de las cosas

- Omrons TM Cobot acelera la integración y la programación

- Visión hiperespectral. ¿Qué es?

- ¿Qué es el diseño arquitectónico?