Novedoso SCR de alto voltaje de retención con estructura de recombinación de portadora incorporada para protección ESD robusta e inmune al enganche

Resumen

Un nuevo rectificador controlado por silicio de alto voltaje compatible con procesos CMOS (HHV-SCR) para protección contra descargas electrostáticas (ESD) se propone y demuestra mediante pruebas de simulación y pulso de línea de transmisión (TLP). La región de recombinación de huecos (o electrones) recientemente introducida H-RR (o E-RR) no solo recombina el portador minoritario en la base del transistor parásito PNP (o NPN) por la capa N + (o P +), sino que proporciona la recombinación adicional para eliminar la portadores de avalancha de superficie por la capa P + (o N +) recién agregada en H-RR (o E-RR), lo que produce una mejora adicional del voltaje de mantenimiento ( V h ). Comparado con el V medido h de 1.8 V de rectificador controlado por silicio activado por bajo voltaje (LVTSCR), el V h de HHV-SCR se puede aumentar a 8.1 V mientras se mantiene una corriente de falla suficientemente alta ( I t2 > 2,6 A). Se logra una mejora de más de cuatro veces en la figura de mérito (FOM).

Introducción

Con el desarrollo de la tecnología integrada de semiconductores y la miniaturización constante del tamaño de las funciones de los dispositivos semiconductores, el daño del dispositivo inducido por ESD se está volviendo más severo. A costa de una gran área de chip, se informó de los dispositivos convencionales como el diodo y el MOSFET de canal N (ggNMOS) con conexión a tierra de diodos y con robustez normal de ESD [1]. Para lograr una capacidad ESD mejorada con una dimensión de dispositivo más pequeña, el rectificador controlado por silicio activado por bajo voltaje (LVTSCR) se ha considerado un dispositivo atractivo debido a su capacidad de alta corriente por unidad de área [2]. Para aplicaciones de bajo voltaje, debido al voltaje de disparo bajo incorporado ( V t1 ) ggNMOS, el LVTSCR con excelente solidez ESD es capaz de proporcionar una velocidad de respuesta ESD más rápida que la obtenida en SCR convencional. Sin embargo, la fuerte retroalimentación positiva inherente provoca un V extremadamente bajo h (1 ~ 2 V), que es responsable del enganche y del disparo incorrecto transitorio [3]. Estos efectos negativos pueden suprimirse eficazmente simplemente aumentando V h [3,4,5,6,7,8,9,10,11]. El dispositivo estará libre del enganche y del disparo incorrecto transitorio, mientras que el V h es superior a la tensión de alimentación (VDD). En consecuencia, la región N + ESD y la región P + LDD se agregaron en SCR con máscaras adicionales y pasos de implante de iones para mejorar V h [3]. Sin embargo, la robustez de ESD puede deteriorarse debido a la disipación de energía adicional junto con el aumento de V h . Además, la tecnología de pinza de voltaje del emisor para V h mejora con corriente de falla aceptable ( I t2 ) también se propuso [5]. Sin embargo, el V h en los enfoques antes mencionados no es ajustable, lo que aún presenta inconvenientes y limitaciones en aplicaciones versátiles.

En esta carta, se propone y demuestra un nuevo rectificador controlado por silicio de alto voltaje de retención (HHV-SCR) mediante simulación TCAD y pruebas TLP. El dispositivo alcanza simultáneamente un alto V h , alto I t2 y V ajustable h sin máscaras ni pasos adicionales. La prueba TLP se llevó a cabo para validar que el V h puede mejorarse de forma eficaz manteniendo un I suficientemente alto t2 . De acuerdo con los resultados probados, el HHV-SCR presenta un V cuatro veces mayor h que en el LVTSCR con la degradación insignificante en I t2 .

Método

En este trabajo, se investiga un nuevo SCR de alto voltaje de retención con una estructura de recombinación de portadora incrustada. Los modelos físicos IMPACT.I, BGN, CONMOB, FLDMOB, SRH y SRFMOB se utilizan en simulación numérica. Según el modelo, H-RR y E-RR están optimizados para lograr un alto V h y alto P M . Los HHV-SCR y LVTSCR fabricados son probados por el sistema TLP.

Estructura y mecanismo

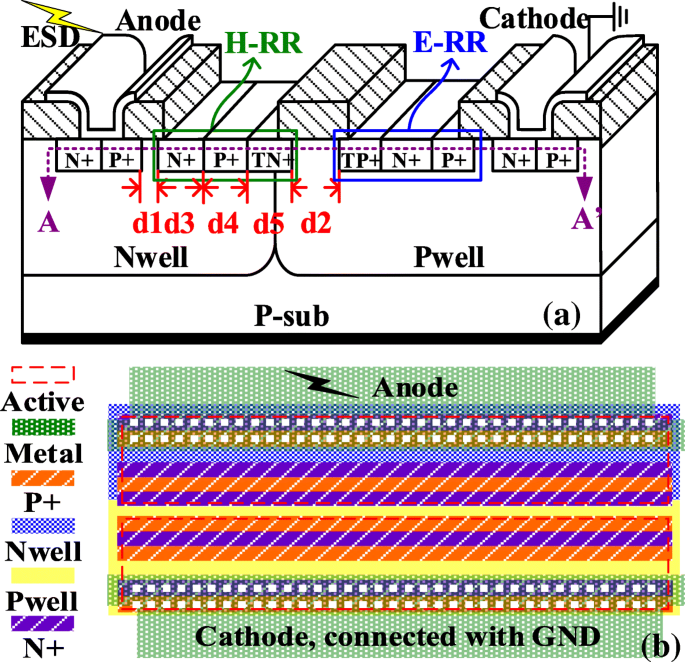

La vista esquemática en sección transversal del HHV-SCR propuesto y el diagrama de distribución se muestran en las Fig. 1a, b, respectivamente. Los nuevos H-RR y E-RR formados por N + y P + flotantes son idénticos al N + y P + en las áreas del ánodo y del cátodo, respectivamente. El N + flotante en H-RR (o P + flotante en E-RR) se coloca junto a la región P + en el ánodo (o la región N + en el cátodo). Además, el nuevo P + flotante en H-RR (o N + flotante en E-RR) también se encuentra junto al mencionado N + flotante en H-RR (o P + flotante en E-RR). El N + de disparo bajo en H-RR (TN +) y el P + de disparo bajo en E-RR (TP +) también se fabrican mediante los mismos procesos que la región N + (o P +) en el ánodo (o cátodo) para garantizar el V t1 dentro de un rango aceptable. Como voltaje ESD positivo ( V ESD ) elevándose hasta un cierto nivel, la unión TN + / P-well / TP + con un voltaje de ruptura bajo se descompondrá primero seguido por el retroceso de los transistores parásitos activados por la corriente de avalancha. La fuerte retroalimentación positiva de los BJT parásitos es responsable de la V considerablemente baja h de la LVTSCR. En el HHV-SCR, el N + en H-RR (o el P + en E-RR) recombinará los portadores minoritarios inyectados desde el borde del ánodo P + (o cátodo N +), lo que reduce la ganancia de corriente ( β ) del parásito PNP (o NPN) y elimina el efecto bipolar de superficie. Es importante destacar que el P + en H-RR (o el N + en E-RR) bloquea el camino de baja resistencia de la superficie al recombinar los electrones de la superficie (o huecos). Comparado con el H-RR sin P + (o E-RR sin N +), el nuevo P + en H-RR (o el N + en E-RR) proporciona la recombinación adicional para eliminar los electrones de superficie (o huecos) inyectados desde el cátodo ( o ánodo) y los inducidos por la ionización por impacto (que se muestra en la Fig. 3a), lo que provoca un aumento adicional de V h . Al combinar estas modificaciones, una mejora significativa en FOM es verificado. La figura de mérito (FOM) se cita de [7] y se define como la densidad de potencia tolerable de un solo dispositivo dada por FOM =( V h · Yo t2 ) / ( N · W ) para evaluar la V h y yo t2 rendimiento de un solo dispositivo. Generalmente, acompañado de la mejora de V h rendimiento, todavía causa la degradación de I t2 debido a la disipación de mayor potencia. Por lo tanto, el FOM más alto significa que el dispositivo único puede alcanzar la capacidad de corriente más alta en el V más alto h nivel ( N es el número del dispositivo de apilamiento; W es el ancho del dispositivo).

un La vista esquemática en sección transversal del HHV-SCR propuesto. b El diagrama de diseño del HHV-SCR propuesto

Resultados y discusión

Resultados simulados

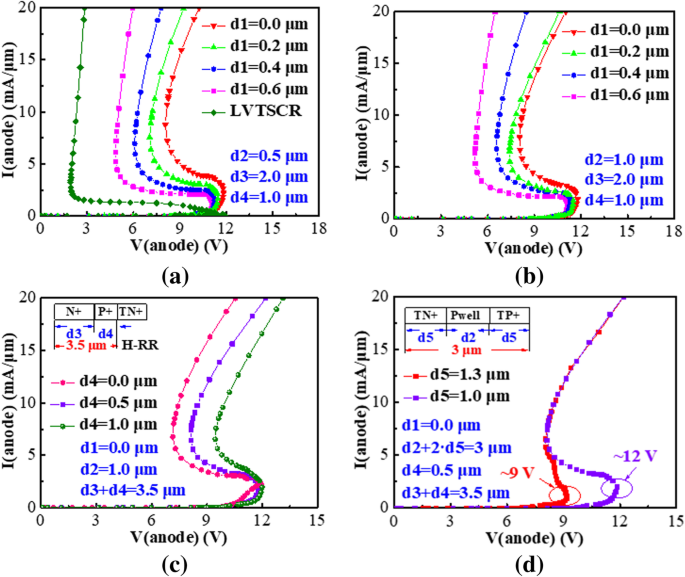

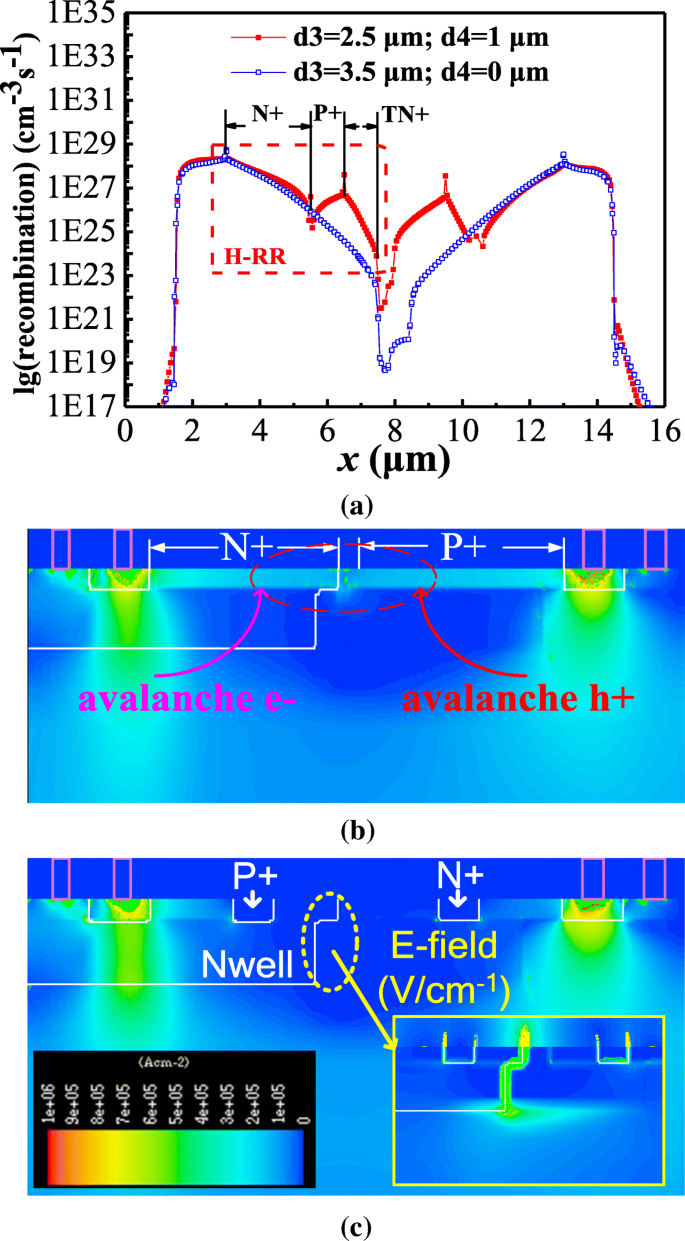

Las características del dispositivo fueron estudiadas y simuladas por TCAD Medici, donde se utilizaron los modelos correspondientes como la ionización por impacto y el modelo de movilidad dependiente de la concentración. Las curvas I-V simuladas de LVTSCR y HHV-SCR se muestran en la Fig. 2. La V h del LVTSCR es tan bajo como 1.8 V, mientras que el V h del HHV-SCR se mejora de 4,6 V a 8,1 V con d1 disminuido de 0,6 μm a 0 μm para d2 =0,5 μm. De hecho, el d1 más pequeño se favorece para mejorar la capacidad de recombinación de N + en H-RR (o P + en E-RR) para obtener un β más bajo , lo que explica que el HHV-SCR siempre alcanza el V más alto h para d1 =0 μm. Los resultados simulados en la Fig. 2b indican que el V h de HHV-SCR se mejora aún más con d2 aumentado de 0,5 a 1 μm debido al aumento de la longitud del dispositivo. Para la demostración, el P + en H-RR (o N + en E-RR) también es un factor clave para aumentar V h . Los resultados simulados se muestran en la Fig. 2c. Cuando el H-RR (o E-RR) con d3 + d4 fijo está completamente formado por dopaje pesado N + (o P +) (por ejemplo, d3 =3.5 μm, d4 =0 μm), el V h es 7.1 V. Al insertar P + dentro de H-RR y N + dentro de E-RR con d3 + d4 fijo (por ejemplo, d3 =2.5 μm, d4 =1.0 μm), la V simulada h se puede aumentar hasta aproximadamente 9,5 V. Se puede inferir que el nuevo P + en H-RR (o N + en H-RR) es eficaz para recombinar electrones de avalancha de superficie (o huecos) para bloquear la trayectoria de la corriente de superficie. Por lo tanto, un V más alto h es necesario para que el HHV-SCR mantenga la misma corriente de mantenimiento ( I h ). La curva de recombinación sola línea AA 'mostrada en la Fig. 3a demuestra el aumento de la tasa de recombinación inducida por nuevo P + en H-RR (o N + en E-RR). El TN + y TP + se adoptan para garantizar que V t1 dentro de un rango aceptable. Ajustando d2 y d5 en el d5 + d2 + d5 fijo, el V t1 de HHV-SCR se puede reducir significativamente de 12 V a 9,0 V para cumplir con la ventana de diseño de circuitos de 5 V con un impacto insignificante en V h , mostrado en la Fig. 2d. Los diagramas de distribución de corriente de los dispositivos simulados en el punto de retención también se muestran en la Fig. 3b, c, respectivamente. En comparación con la distribución de corriente en el HHV-SCR con d3 =3,5 μm, d4 =0 μm, la ruta de la corriente de superficie en el HHV-SCR propuesto está bloqueada debido a la tasa de recombinación adicional que se beneficia de P + en H-RR y N + en E -RR.

Características I-V snapback simuladas del LVTSCR convencional y HHV-SCR propuesto con el aumento de d1 de 0 μm a 0,6 μm en a d2 =0,5 μm y b d2 =1 μm. c Las curvas I-V de HHV-SCR con diferentes d3 y d4 para el d3 + d4 fijo (d3 + d4 =3,5 μm). d Las curvas I-V de HHV-SCR con varios V t1

un Las curvas de distribución de recombinación y las distribuciones actuales de HHV-SCR con ( b ) d3 =3,5 μm, d4 =0 μm y ( c ) d3 =2,5 μm, d4 =1 μm

Resultados experimentales

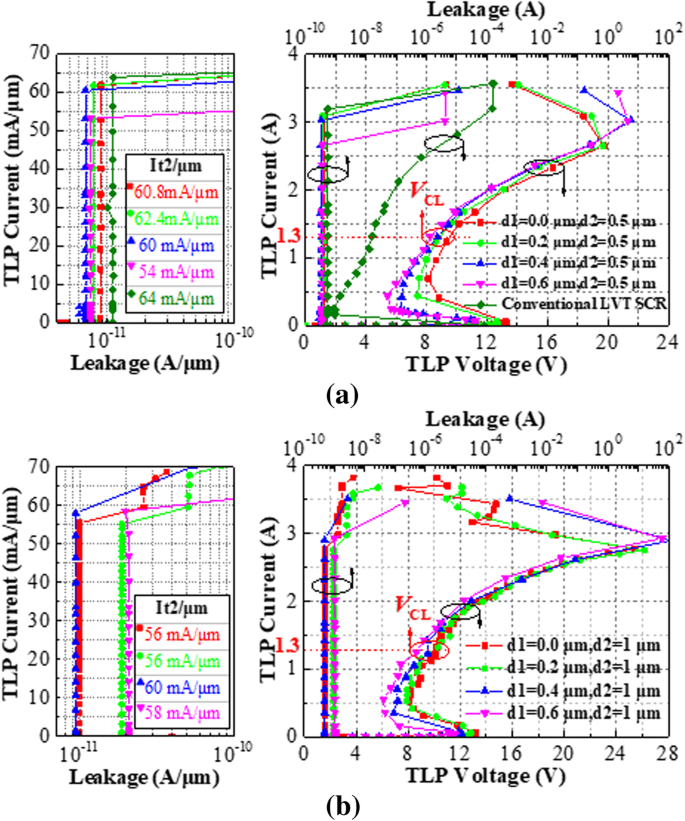

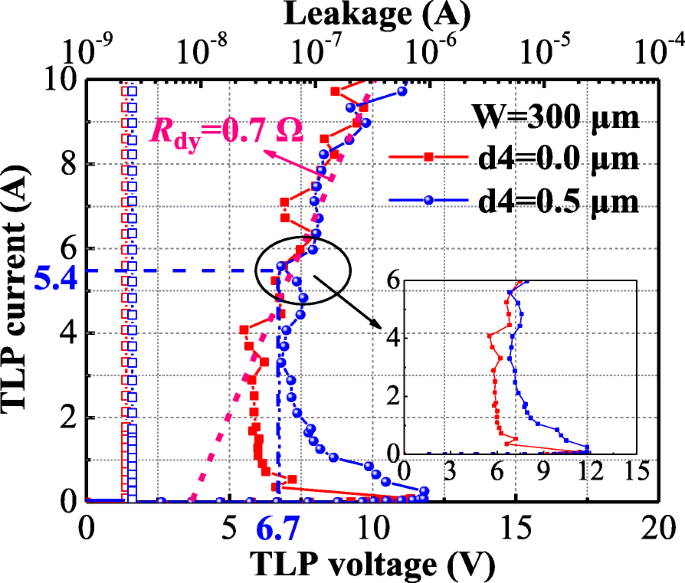

Los dispositivos fabricados son probados por el sistema TLP. Los anchos totales (W) de todos los SCR probados son 50 μm y con un solo dedo para la comparación de los parámetros (Tabla 1). Todos los dispositivos probados ocupan un área de diseño similar. Los parámetros del dispositivo se muestran en la Tabla 2. La Figura 4a muestra las curvas de medición de TLP de los HHV-SCR con d2 =0.5 μm (llamados dispositivos B1) y LVTSCR. Según los resultados experimentales, el V h de HHV-SCR se incrementa de 5,5 a 8,0 V con el d1 disminuido de 0,6 μm a 0,0 μm, que es mucho más alto que 1,8 V obtenido en el LVTSCR convencional. A medida que d2 aumenta de 0,5 a 1 μm, los HHV-SCR correspondientes (llamados dispositivos B2) obtienen un V más alto. h mostrado en la Fig. 4b. Teniendo en cuenta la ventana de diseño, la tensión de sujeción ( V CL ) bajo el índice dado también es un parámetro clave para evaluar la capacidad de sujeción. De los resultados probados, la V CL de HHV-SCR de un solo dedo también se mantiene dentro del rango aceptable en el HBM =2 kV ( I TLP =1,3 A) aunque el ancho de los dedos es de solo 50 μm. Sin embargo, todos los dispositivos no pueden proporcionar la V elegible CL bajo el estrés ESD más fuerte debido al alto V h y gran resistencia dinámica ( R dy ) inducida por un dispositivo de tamaño insuficiente. Para satisfacer el requisito más alto de ESD en el chip, el ancho del dedo se extiende a los 300 μm aceptables para d1 =0,6 μm, d4 =0,5 μm y d1 =0,6 μm, d4 =0 μm. La prueba de TLP que se muestra en la Fig.5 demuestra que el HHV-SCR con d4 =0.5 μm presenta la R extremadamente baja dy (aproximadamente 0,7 Ω), robustez ESD superior ( I t2 > 10 A) y alto V h de 6,7 V. Se puede observar que el V CL es tan bajo como 6,7 V en el I TLP =5,4 A (HBM =8 KV). Además, el V más alto h También se demuestra que se benefició de P + en H-RR (o N + en E-RR), en comparación con la curva TLP de SCR con d4 =0 μm. Los resultados probados de dispositivos de un solo dedo de 50 μm se enumeran en la Tabla 1.

Corriente de falla experimental en el ancho de la unidad y características TLP I-V correspondientes del LVTSCR convencional y los HHV-SCR propuestos con a d2 =0,5 μm y b d2 =1 μm a W =50 micras

Característica de TLP experimental de HHV-SCR con d4 =0,0 μm y d4 =1,0 μm en d1 =0,6 μm, W =300 micras

Conclusión

Un nuevo HHV-SCR compatible con el proceso CMOS se estudia y mide mediante la simulación TCAD y el sistema TLP. En comparación con el LVTSCR convencional, el HHV-SCR presenta una V significativamente mejorada h (una mejora de más del 450% en el V h se logra) y sin sacrificar el área de viruta. Además, el V h del HHV-SCR se puede ajustar de 5,5 V a 8,1 V para satisfacer los diferentes V h requisitos con degradación insignificante en I t2 . En términos de P M , en comparación con el LVTSCR convencional, también se logra una mejora de más del 200%.

Disponibilidad de datos y materiales

Todos los datos generados o analizados durante este estudio se incluyen en este artículo publicado.

Nanomateriales

- Un resumen sobre la tecnología IC para microcontroladores y sistemas integrados

- Maxim:transceptor IO-Link dual con regulador DC-DC y protección contra sobretensiones

- TRS-STAR:sistemas integrados robustos y sin ventilador de un valor

- Nuevas nanopartículas de Au Nanostars @ PEG biocompatibles para la obtención de imágenes de TC in vivo y las propiedades de depuración renal

- Nanoesferas de carbono monodispersas con estructura porosa jerárquica como material de electrodo para supercondensador

- Mejora de la absorción y modulación de frecuencia del microbolómetro THz con estructura de micropuente mediante antenas de tipo espiral

- Nuevas nanopartículas dirigidas al receptor CD44 y mitocondrial dual para liberación activada por estímulos redox

- Morfología, estructura y propiedades ópticas de películas semiconductoras con nanoislinas GeSiSn y capas tensas

- Soporte de catalizador anódico novedoso para pila de combustible de metanol directo:caracterizaciones y rendimiento de una sola pila

- Automatización y ciberseguridad:protección completa para los clientes

- Materiales y diseño de PCB para alta tensión