Una referencia de banda prohibida con sesgo propio de 180 nm con alta mejora de PSRR

Resumen

En este artículo, se presenta una referencia de banda prohibida (BGR) con autopolarización mejorada con una alta tasa de rechazo de la fuente de alimentación (PSRR). Un amplificador operacional que construye un circuito de retroalimentación se multiplexa con la generación de voltaje de coeficiente de temperatura positivo (TC) para un menor consumo de energía, donde se adopta un voltaje de compensación para lograr un voltaje proporcional a la temperatura absoluta (PTAT). Con la generación de referencia independiente de la temperatura, se realizan dos bucles de retroalimentación al mismo tiempo para la mejora de PSRR, que forman un bucle de retroalimentación negativa local (LNFL) y un bucle de autopolarización global (GSBL). El BGR propuesto se implementa en una tecnología BCD de 180 nm, cuyos resultados muestran que el voltaje de referencia generado es de 2.506 V, y el TC es de 25 ppm / ° C en el rango de temperatura de -55 a 125 ° C. La sensibilidad de línea (LS) es 0.08 ‰ / V. Sin ningún condensador de filtro, el PSRR es de 76 dB a bajas frecuencias, más de 46 dB hasta 1 MHz.

Introducción

La referencia de voltaje es uno de los módulos centrales en los sistemas electrónicos, que se usa ampliamente en electrónica médica, administración de energía, sensores ambientales inalámbricos y circuitos de comunicación. Con la mejora de la tecnología, el área del chip continúa reduciéndose y la capacidad antiinterferente continúa aumentando, y los requisitos para la optimización estructural y la inmunidad al ruido de la referencia de voltaje están aumentando dramáticamente, especialmente en aplicaciones a nanoescala [1].

Los circuitos de referencia de banda prohibida (BGR) convencionales requieren bloques de circuitos adicionales para proporcionar corriente de polarización para todo el circuito, lo que aumenta en gran medida el área del circuito y el consumo de energía. Al mismo tiempo, la corriente de polarización generada se ve muy afectada por la temperatura, lo que afecta el coeficiente de temperatura (TC) del voltaje de referencia. Se han reportado muchas técnicas de compensación de alto orden para TC mejoradas, como compensación de curvatura a trozos [2], compensación de curvatura exponencial [3], compensación de raíz cuadrada basada en fugas (LSRC) [4], y así sucesivamente. Otra desventaja del circuito BGR convencional es que se ve muy afectado por el entorno externo y el voltaje de salida es inestable, que es el tema central de este artículo.

La relación de rechazo de la fuente de alimentación (PSRR) es un parámetro importante para medir la inmunidad al ruido de una referencia de voltaje. Las soluciones convencionales para mejorar la PSRR tienen como costo el área del chip y el consumo de energía [5], como amplificadores adicionales, transistores de canal largo, estructuras en cascodo [6], etapa de ganancia adicional [7], etc. El atenuador activo y la compensación de adaptación de impedancia se adoptaron en [8] para mejorar el PSRR en frecuencias bajas y altas, respectivamente. Yue y col. [9] utilizó espejos de corriente en cascodo para mejorar PSRR. Se utilizaron técnicas de sesgo corporal y retroalimentación negativa en [10] para una alta PSRR.

Con el fin de superar los problemas mencionados anteriormente, en este informe se propone un BGR autodirigido mejorado con un alto PSRR. Se realizan dos bucles de retroalimentación al mismo tiempo para la mejora de PSRR, que forman un bucle de retroalimentación negativa local (LNFL) y un bucle de autopolarización global (GSBL). Mientras tanto, se logra una fuente de corriente de autopolarización (SBCS) para todo el BGR. En estado estable, el BGR propuesto se autoalimenta a través del GSBL sin módulos de corriente de polarización adicionales ni área de chip. La técnica presentada separa el voltaje de suministro del voltaje de referencia de salida a través de un amplificador de corriente integrado en GSBL, que puede mejorar efectivamente el PSRR. Además, para evitar la inestabilidad del voltaje de salida, se diseña un LNFL en el terminal de voltaje de salida para mantener estable el voltaje de salida. Además, la tensión de referencia estable a la temperatura se genera con LNFL y GSBL de forma multiplexada. Con estos métodos, se implementa un BGR auto-sesgado con alta mejora de PSRR con estructura compacta y consumo de corriente.

Método

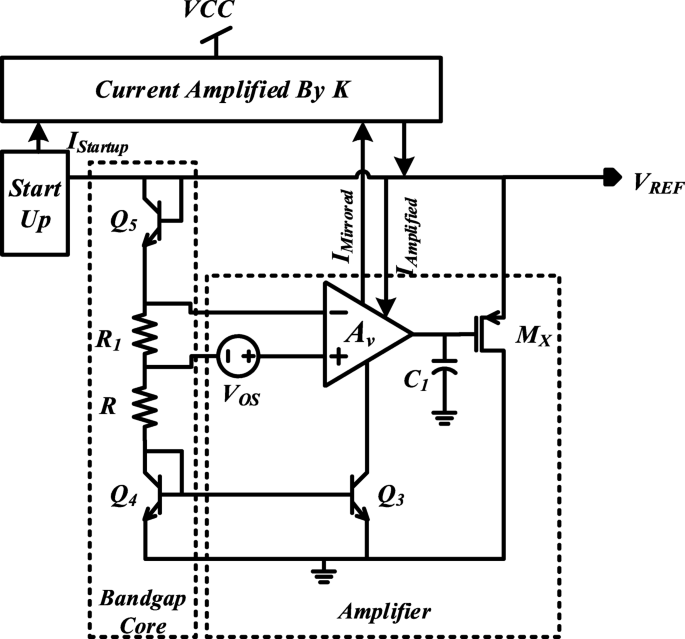

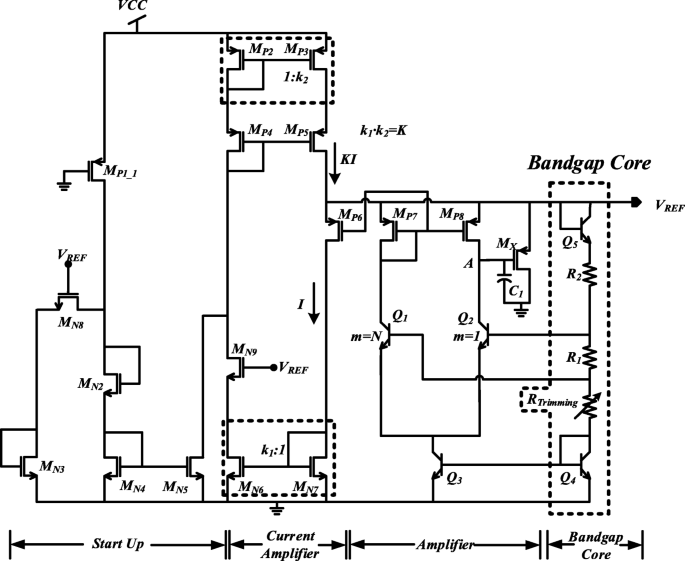

Como se muestra en la Fig. 1, el circuito BGR propuesto consta de un circuito de arranque, un amplificador de corriente, un amplificador operacional y un núcleo de referencia de banda prohibida. El circuito de puesta en marcha se utiliza para deshacerse del punto cero degenerado. El voltaje de compensación incorporado en el amplificador está configurado para ser proporcional al voltaje de temperatura absoluta (PTAT), que puede realizar una corriente PTAT a través de la resistencia R1. Con el TC positivo de voltaje en R1 y R2, el TC negativo de V BE (Q5) y V BE (Q4) se puede cancelar correctamente para lograr un voltaje de referencia estable a la temperatura en el nodo V REF . Al mismo tiempo, se formó un LNFL con la ayuda de un amplificador para mejorar el rendimiento. Combinado con el amplificador de corriente en la parte superior de la Fig. 1, se realiza un GSBL para una mejora adicional del PSRR. La implementación detallada del BGR propuesto se muestra en la Fig. 2.

Diagrama de arquitectura equivalente de la referencia de voltaje propuesta

Esquema de la referencia de voltaje propuesta

Circuito de puesta en marcha

El circuito de arranque se muestra en la parte izquierda de la Fig. 2. Al comienzo de la etapa de arranque, la tensión de salida V REF está en un nivel bajo, lo que mantiene a MN8 y MN9 desactivados. La corriente a través de MP1_1 se usa para generar una corriente de arranque a MP5, donde MP1_1 es una gran resistencia con una relación de aspecto bastante pequeña. El voltaje en V REF se cargará gradualmente con la corriente de arranque. Cuando el voltaje en V REF excede el voltaje de operación mínimo de la parte del núcleo de banda prohibida, se generará la corriente de polarización para el amplificador. Esto conducirá el BGR al punto de operación deseado. Al mismo tiempo, los transistores MN8 y MN9 se encenderán gradualmente, lo que cambia la corriente de suministro de MP5 a la corriente autopolar generada en el núcleo de banda prohibida. Una vez que se completa el inicio, la corriente de inicio no se apaga para V REF reajuste en el caso de que la tensión de referencia caiga por alguna razón [11].

Generador SBCS

Hay dos bucles SBCS en el BGR propuesto, que son útiles para mejorar el rendimiento [1]. El primero se encuentra en la corriente de cola del amplificador. La corriente PTAT a través del transistor Q4 se refleja en Q3. Sin embargo, la corriente a través de Q4 está determinada por el voltaje a través de la resistencia R1, que se fija al voltaje de compensación de entrada del amplificador. Debido a las mismas relaciones de aspecto de MP7 y MP8, el voltaje de compensación de entrada del amplificador se puede expresar como

$$ {V} _ {OS} ={V} _T \ ln N $$ (1)donde N es la relación de área de Q1 y Q2, y V T es el voltaje térmico. Por lo tanto, la corriente en las partes del núcleo del amplificador y de la banda prohibida es la corriente PTAT, que puede ser proporcionada por

$$ {I} _ {R1} ={V} _T \ ln N / {R} _1 $$ (2)La corriente del núcleo de referencia de banda prohibida se refleja en el amplificador como corriente de cola, formando el primer bucle autopolarizado.

El segundo bucle SBCS se compone del amplificador de corriente. La corriente PATA que se muestra en la ecuación (2) se refleja en el amplificador de corriente mediante el espejo de corriente de MP7 y MP6. Entonces la corriente, I , se amplifica con K como la fuente actual del nodo VREF, que se puede describir como

$$ K ={k} _1 {k} _2 $$ (3)donde k 1 = S MN 6 / S MN 7 , k 2 = S MP3 / S MP2 , S i es la relación de aspecto del transistor i . Por lo tanto, la corriente, KI , se vuelve a inyectar en el amplificador y en las partes centrales de la banda prohibida, lo que construye el segundo bucle de autopolarización.

Para garantizar el correcto funcionamiento con bajo consumo energético, la corriente KI , debe ser un poco más grande que el requisito de corriente mínimo del amplificador y el núcleo de banda prohibida. En el diseño propuesto, las corrientes a través de MP6, MP7 y MP8 se establecen al mismo nivel, I . La corriente a través del núcleo de banda prohibida es 2 I . Por lo tanto, la relación, 6 ≥ K > 5, debe satisfacerse [12,13,14].

V REF Circuito del generador

La V REF El circuito generador se muestra en la parte derecha de la Fig. 2, que consta de un amplificador y un núcleo de banda prohibida. Como se muestra en la ecuación (2), el voltaje de compensación PTAT del amplificador es multiplexado por los bucles SBCS [15]. Esto hace que la corriente a través de R1, R2 y R Trimming es la corriente PTAT, que se utiliza como compensación de temperatura del TC negativo de Q4 y Q5. El voltaje de referencia generado, V REF , se puede expresar como

$$ {V} _ {REF} =2 {V} _ {BE} + \ left (1+ \ frac {R_2 + {R} _ {Trim \ min g}} {R_1} \ right) {V} _T \ En N $$ (4)Con el ajuste de proporción de ( R 2 + R Recortar mínimo g ) / R 1 , se puede realizar un voltaje de referencia con compensación de temperatura con una deriva de baja temperatura.

Comentarios

Un LNFL se establece en el amplificador y el núcleo de banda prohibida, que está formado por dos pequeños LNFL. El primero, loop1, es de la entrada del amplificador a V REF y retroalimentación a la entrada del amplificador. El otro, loop2, es de V REF a través del núcleo Bandgap hasta la cola actual del amplificador y retroalimentación a V REF . Para el bucle 1, hay bucles locales dobles de retroalimentación positiva y retroalimentación negativa con la entrada del amplificador. El circuito de retroalimentación positiva se compone de Q5, R2, R1, Q1, MP8 y MX. El circuito de retroalimentación negativa consta de Q5, R2, Q2 y MX. La ganancia del circuito de retroalimentación positiva y negativa se deriva como

$$ {A} _ {V, PF} =\ frac {R_ {Recortar \ min g}} {R_1 + {R} _ {Recortar \ min g} + {R} _2} {g} _ {m, Q1} {r} _ {o, MP8} $$ (5) $$ {A} _ {V, NF} =\ frac {R_1 + {R} _ {Recortar \ min g}} {R_1 + {R} _ {Recortar \ min g} + {R} _2} {g} _ {m, Q2} {r} _ {o, MP8} $$ (6)donde g m , Q 1 es la transconductancia del transistor Q1, r o , MP 8 es la resistencia de salida del transistor MP8, y el g m de Q1 y Q2 es aproximadamente igual. Dado que el efecto del ciclo de retroalimentación negativa es más fuerte que el del ciclo de retroalimentación positiva, el ciclo1 se comporta como un ciclo de retroalimentación, cuya característica del ciclo se puede expresar como

$$ {T} _ {\ mathrm {loop} 1} \ approx \ frac {R_1} {R_1 + {R} _ {Trim \ min g} + {R} _2} {g} _ {m, Q1} {r } _ {o, MP8} $$ (7) $$ {p} _0 \ approx \ frac {1} {r_ {o, MP8} {C} _1} $$ (8)donde p 0 es el polo dominante. Con respecto a loop2, la interpretación puede ser dada por

$$ {T} _ {\ mathrm {loop} 2} \ approx \ frac {1 / {g} _ {m, MP8}} {R_1 + {R} _ {Trim \ min g} + {R} _2} $ $ (9) $$ {p} _1 \ approx \ frac {g_ {m, MP8}} {C_1} $$ (10)donde g m , MP 8 es la transconductancia del transistor MP8 y p 1 es el polo dominante. Como resultado, la ganancia de bucle total de LNFL es

$$ {T} _ {\ mathrm {LNFL}} \ approx \ frac {R_1 {g} _ {m, Q1} {r} _ {o, MP8} + 1 / {g} _ {m, MP8}} {R_1 + {R} _ {Recortar \ min g} + {R} _2} \ frac {1 + s / {z} _0} {\ left (1 + s / {p} _0 \ right) \ left (1+ s / {p} _1 \ right)} $$ (11)Teniendo en cuenta la ecuación (2), la ecuación (11) se puede reescribir como,

$$ {T} _ {\ mathrm {LNFL}} \ approx \ frac {r_ {o, MP8} \ ln N + 1 / {g} _ {m, MP8}} {R_1 + {R} _ {Trim \ min g} + {R} _2} \ frac {1 + s / {z} _0} {\ left (1 + s / {p} _0 \ right) \ left (1 + s / {p} _1 \ right)} $$ (12)donde z 0 ≈ g m , MP 8 / [ C 1 (1 + 1 / ln N )]. Desde N =8 en el diseño propuesto, hace el cero, z 0 , aproximadamente igual al doble del polo, p 1 , que puede extender el ancho de banda del bucle de LNFL al doble.

Un GSBL está formado por el amplificador de corriente, el núcleo de banda prohibida y el amplificador, que pueden proporcionar corriente de polarización para todo el circuito en un método de autopolarización con un rendimiento de PSRR mejorado. La ganancia de bucle de GSBL puede ser proporcionada por

$$ {T} _ {\ mathrm {GSBL}} \ approx \ frac {K \ left (1/3 {g} _ {m, MP8} \ Big \ Vert 1 / {g} _ {m, MX} \ derecha)} {R_1 + {R} _ {Recortar \ min g} + {R} _2} $$ (13)donde g m , MX es la transconductancia del transistor M X . El efecto principal del transistor M X es reducir la impedancia equivalente a V REF con la conveniencia de la compensación de bucle. T GSBL está configurado para ser más pequeño que uno en el diseño propuesto, lo que puede evitar la oscilación.

Con la ayuda de LNFL y GSBL, la estabilidad del voltaje de referencia generado, V REF , se puede mejorar enormemente.

PSRR de referencia de voltaje propuesto

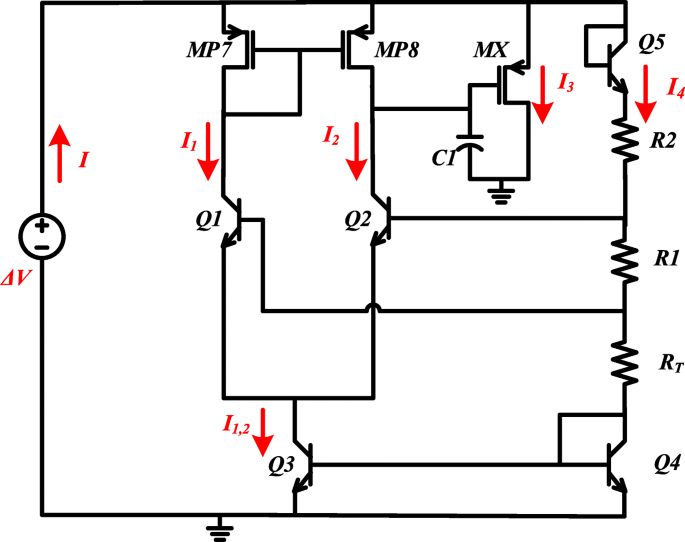

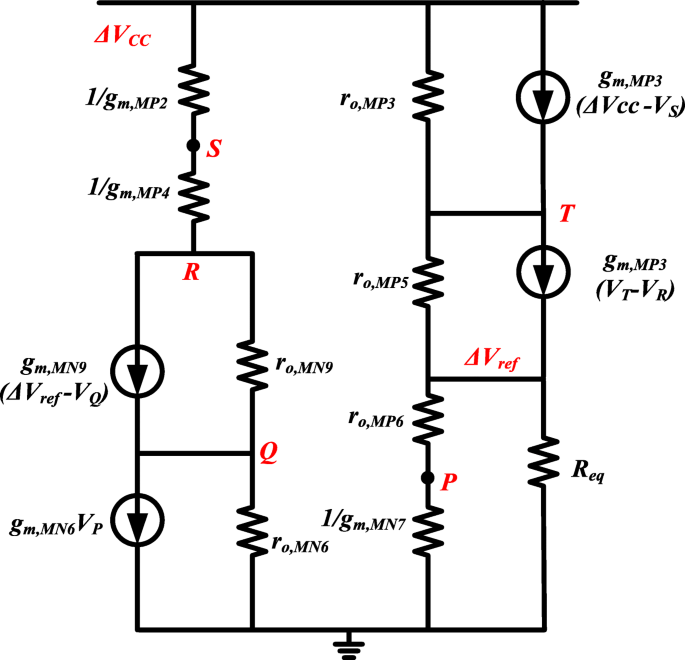

Para simplificar el cálculo de PSRR del circuito propuesto, la resistencia equivalente de la parte alimentada por el voltaje de referencia, V REF , se calcula en primer lugar. El diagrama de cálculo de esta parte se muestra en la Fig. 3 [16].

R eq diagrama de cálculo

La Figura 4a muestra un modelo de pequeña señal para el cálculo de la resistencia equivalente de las ramas del circuito 1, 2, donde las corrientes I 1 y yo 2 flujo en la Fig. 3, respectivamente. Entonces, la resistencia equivalente, R eq 1,2 , se puede expresar como

$$ {R} _ {eq1,2} \ approx \ frac {3 {R} _ {eq, 4} {r} _ {o, Q1}} {3 {g} _ {m, Q1} {r} _ {o, Q1} \ left ({R} _T + {R} _1 + {r} _ {o, Q3} \ right) + {g} _ {m, Q1} {R} _1 {r} _ {o, Q1} +3 {R} _ {eq, 4}} $$ (14)donde g m , Q 1 y r o , Q 1 son la transconductancia y la resistencia de salida de Q1, respectivamente; R eq 4 es la resistencia equivalente de la rama con I 4 . Dado que el voltaje de puerta de MP6 que se muestra en la Fig.2 está determinado por el voltaje de drenaje de MP7, también se debe calcular la atenuación de ruido de la fuente de alimentación (PSNA) en el nodo M, que puede ser dada por

$$ {V} _M =\ Delta {V} _ {ref} + \ frac {g_ {m, Q1} {R} _1 {r} _ {o, Q2}} {2 {g} _ {m, MP7 } \ left ({r} _ {o, Q2} + {r} _ {o, MP8} \ right) {R} _ {eq4}} \ Delta {V} _ {ref} \ approx \ Delta {V} _ {ref} $$ (15)donde r o , MP 8 y r o , Q 2 son resistencias de salida de MP8 y Q2, respectivamente; g m , MP 7 es la transconductancia de MP7. Como se afirma en la ecuación (15), el ruido de suministro tiene poca influencia en el voltaje de la puerta de la fuente de MP6. Esto hace que MP6 actúe como una impedancia alta, r o , MP 6 , que separa los impactos de ruido del amplificador y las partes centrales de la banda prohibida.

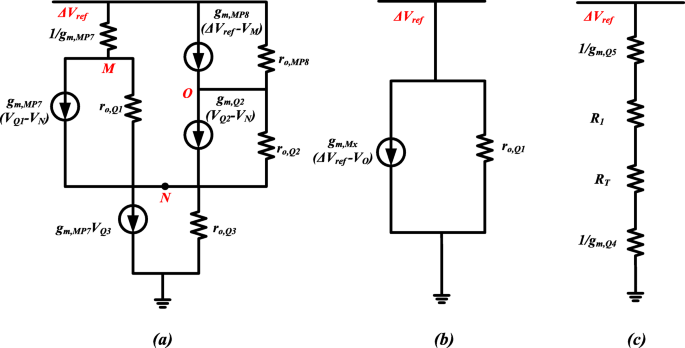

Modelo de pequeña señal para R eq . un R eq1,2 diagrama de cálculo. b R eq3 diagrama de cálculo. c R eq4 diagrama de cálculo

La resistencia equivalente de rama con I 3 en la Fig. 3 se puede derivar de la Fig. 4b, que se puede expresar como

$$ {R} _ {eq3} \ approx \ frac {6 {R} _ {eq, 4}} {g_ {m, mx} \ left [3 {g} _ {m, Q1} {r} _ { o, Q1} \ left ({R} _T + {R} _1 + {r} _ {o, Q3} \ right) +3 {R} _ {eq, 4} + {g} _ {m, Q1} {r } _ {o, Q1} {R} _1 \ right]} $$ (16)donde g m , Mx es la transconductancia de Mx. El modelo de pequeña señal de resistencia equivalente de rama con I 4 en la Fig. 3 se muestra en la Fig. 4c, que es,

$$ {R} _ {eq4} \ approx 1 / {g} _ {m, Q5} + {R} _1 + {R} _T + 1 / {g} _ {m, Q4} + {R} _2 $$ (17)Por lo tanto, la resistencia equivalente de pequeña señal del amplificador y las partes del núcleo de banda prohibida en la Fig.3 es

$$ {R} _ {eq} ={R} _ {eq1,2} \ left \ Vert {R} _ {eq3} \ right \ Vert {R} _ {eq4} $$ (18)Por lo tanto, el PSRR total de la referencia de voltaje propuesta se puede ilustrar en la Fig. 5. El PSRR puede estar dado por

$$ \ frac {\ Delta {V} _ {ref}} {\ Delta {V} _ {CC}} \ approx \ frac {6 {R} _ {eq, 4}} {g_ {m, mx} { g} _ {m, mp3} {r} _ {o, mp3} {r} _ {o, mp6} \ left [3 {g} _ {m, Q1} {r} _ {o, Q1} \ left ({R} _T + {R} _1 + {r} _ {o, Q3} \ right) +3 {R} _ {eq, 4} + {g} _ {m, Q1} {r} _ {o, Q1 } {R} _1 \ right]} $$ (19)Desde g m r o >> 1 es generalmente válido, la influencia del ruido de la fuente de alimentación en el voltaje de referencia generado se suprime en gran medida.

Modelo de pequeña señal para PSRR

Resultados y discusión

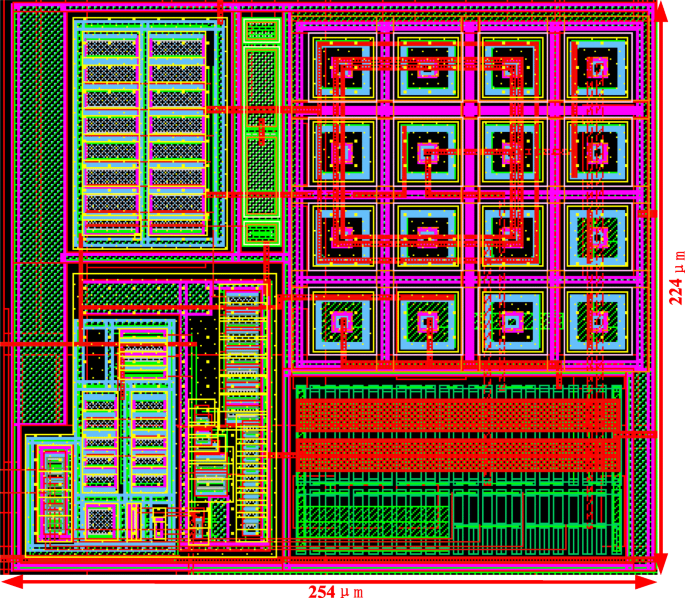

La referencia de voltaje se implementa en un proceso BCD de 180 nm, cuyo diseño se muestra en la Fig.6, ocupando un 0,05690 mm 2 área activa.

Disposición del circuito propuesto

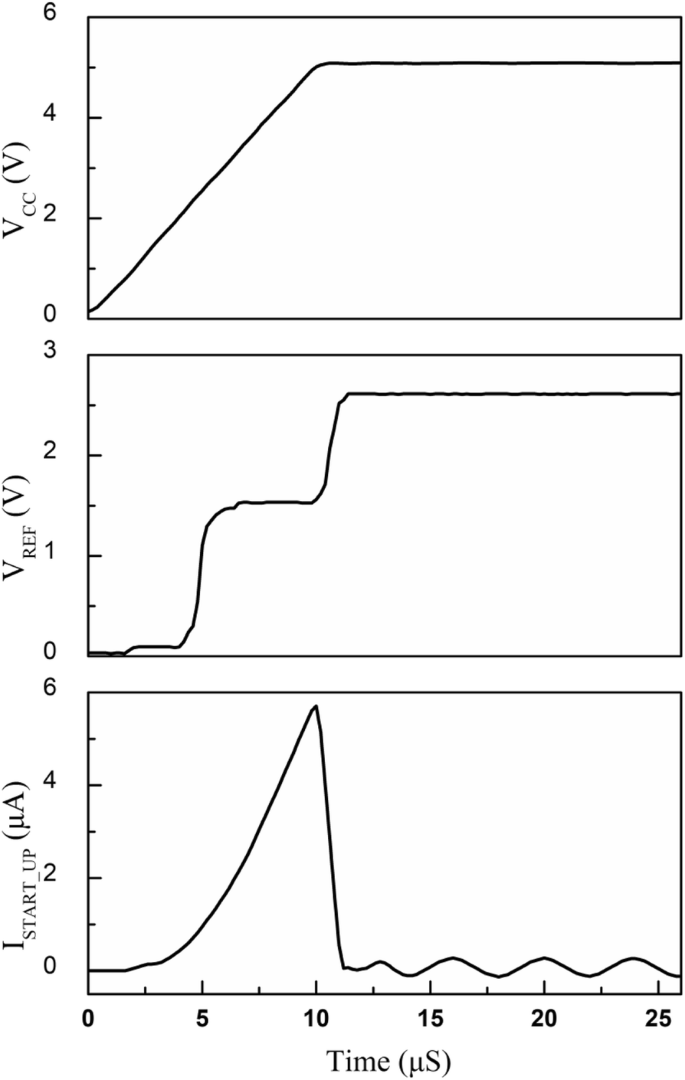

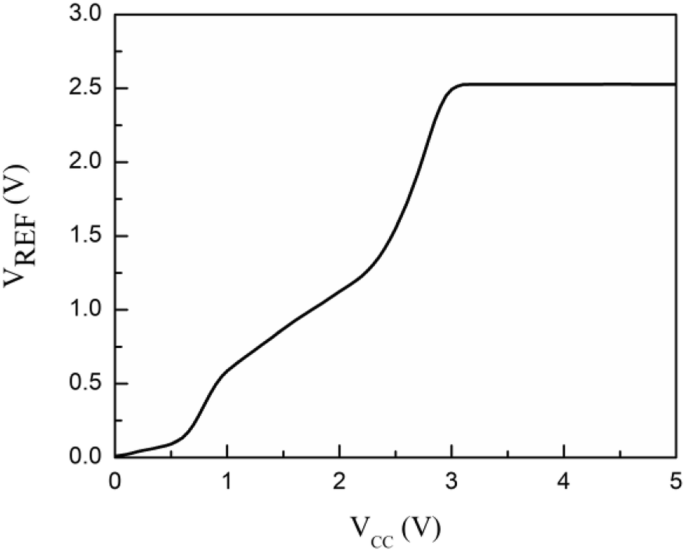

Las formas de onda de arranque simuladas se muestran en la Fig. 7, que ilustra el procedimiento transitorio con el establecimiento del voltaje de la fuente de alimentación. Cuando la tensión de alimentación es pequeña, todo el circuito de referencia no funciona por completo, lo que significa que la corriente de la rama de arranque es muy pequeña y la tensión de referencia se mantiene en cero. Con el aumento del voltaje de la fuente de alimentación, el voltaje de referencia generado es estable en primer lugar a aproximadamente 2 V SER debido al funcionamiento anormal de la parte del amplificador en la Fig. 2. Cuando el voltaje de suministro aumenta por encima del voltaje de suministro mínimo requerido del BGR propuesto, el amplificador operacional central comienza a funcionar y el voltaje de referencia se estabiliza rápidamente en el valor deseado. Además, la corriente de arranque cae casi a cero con un voltaje de referencia deseado, mientras que el SBCS propuesto reemplaza el suministro de corriente con el GSBL. El consumo de energía del circuito de arranque representa una pequeña parte del del chip.

Característica transitoria de arranque de la referencia de voltaje propuesta

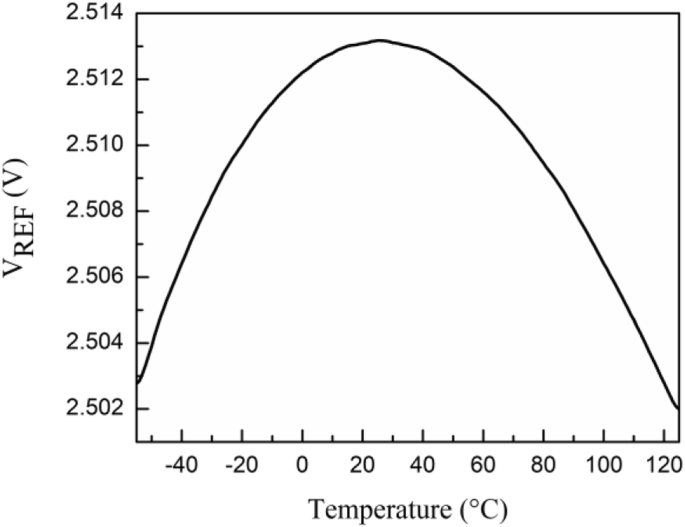

Las características de temperatura del voltaje de referencia generado, V REF , se muestran en la Fig. 8. La variación de voltaje de V REF en el rango de -55 ° C ~ 125 ° C es 11,3 mV, donde se alcanza un TC de 25 ppm / ° C.

Dependencia de la temperatura del voltaje de referencia generado

La Figura 9 demuestra la sensibilidad de línea (LS) del voltaje de salida de referencia. El BGR propuesto se puede establecer con éxito con una tensión de alimentación de 3 V y V REF la variación es de 0,2 mV dentro de una tensión de alimentación de 3-5 V. Esto significa que se obtiene un buen LS de 0.08 ‰ / V.

Dependencia del suministro de la tensión de referencia generada

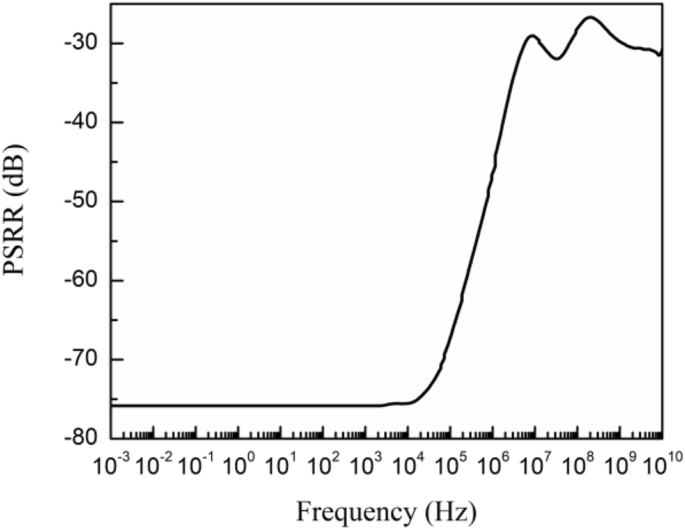

El rendimiento mejorado del PSRR se ilustra en la Fig. 10, que tiene un PSRR de 76 dB que coincide con los resultados teóricos de la ecuación (19) a bajas frecuencias y por encima de 46 dB hasta 1 MHz.

Característica PSRR de la referencia de voltaje propuesta

El método de recorte binario convencional es adecuado para el BGR propuesto, que adopta un recorte de 8 bits para R Recorte . Esto puede realizar un paso de recorte de 9 mV / LSB. La Tabla 1 muestra el rendimiento de la referencia de voltaje recortada con voltaje de suministro de 3-5 V y un rango de temperatura de -55 a 125 ° C en esquinas de proceso de diferencia, que incluyen casos típicos, lentos y rápidos. Como se muestra en la Tabla 1, la variación de temperatura está dentro del 0.6%, el LS está por debajo de 0.12 ‰ / V y el PSRR está por encima de 71 dB a 10 Hz.

La Tabla 2 brinda el resumen característico de la referencia de voltaje propuesta y la comparación con algunas referencias de voltaje informadas anteriormente. Dado que la referencia de voltaje propuesta tiene como objetivo una alta estabilidad de suministro, en este documento no se utiliza una compensación de temperatura de alto orden. Por lo tanto, el TC de [11,12,13], que se centra principalmente en los métodos de optimización de temperatura o potencia, es menor que el de la referencia de voltaje propuesta. El TC de la referencia de voltaje propuesta se puede optimizar aún más con los métodos de compensación de curvatura informados en la literatura según sea necesario. Con la estructura compacta propuesta, LNFL y GSBL se realizan con un voltaje de referencia independiente de la temperatura al mismo tiempo, que tiene el mejor rendimiento de PSRR y LS en la Tabla 2.

Conclusión

En este artículo se presenta una BGR compactada con sesgo propio con una alta PSRR. El voltaje PTAT se implementa mediante un amplificador operacional con voltaje de compensación de entrada asimétrico, y el voltaje de temperatura negativo se superpone para generar un voltaje de salida de referencia. Al mismo tiempo, se realizan dos bucles de retroalimentación, LNFL y GSBL, con las mismas partes para la estabilidad de la temperatura, lo que reduce la complejidad estructural. Esto conduce a la autosuficiencia de la corriente de suministro y la mejora de la sensibilidad de la fuente de alimentación con un alto PSRR.

Disponibilidad de datos y materiales

Todos los datos generados o analizados durante este estudio se incluyen en este artículo publicado.

Abreviaturas

- BGR:

-

Referencia de bandgap

- PSRR:

-

Relación de rechazo de la fuente de alimentación

- TC:

-

Coeficiente de temperatura

- PTAT:

-

Proporcional a la temperatura absoluta

- LNFL:

-

Bucle de retroalimentación negativa local

Nanomateriales

- Ohmímetros de alto voltaje

- Algunos ejemplos con circuitos de CA

- ST:regulador de conmutación con amplios rangos de voltaje

- Impresión 3D de alta velocidad con AFPM

- Impresión 3D de alta velocidad con AION500MK3

- Gran mejora de la conductividad térmica del compuesto de silicona con nanocables de cobre ultralargos

- Convertidor de polarización con birrefringencia controlable basado en metauperficie híbrida de grafeno totalmente dieléctrico

- Célula solar híbrida de silicio nanoestructurado orgánico de alto rendimiento con estructura de superficie modificada

- Una referencia de voltaje sin resistencia de baja potencia a nanoescala con PSRR alto

- Solución de problemas de fallas en la fuente de alimentación de alto voltaje

- Materiales y diseño de PCB para alta tensión